# Logic Design

Number Representation and Arithmetic Circuits

#### Number representation

- In a binary number the right-most bit is called the leastsignificant bit (LSB) and the left-most bit is called the most significant bit (MSB)

- A group of 4 bits is called a nibble

- A group of 8 bits is called a byte

### Number representation

- Numbers that are positive only are called unsigned

- Numbers that can be positive or negative are called signed

- Numbers could be integer or real

- Simplest: unsigned integer

- · A decimal integer:

$$D = d_{n-1}d_{n-2}...d_1d_0$$

$$V(D) = d_{n-1} \times 10^{n-1} + d_{n-2} \times 10^{n-2} + ... + d_1 \times 10^1 + d_0 \times 10^0$$

#### Number representation

- Conversion from decimal to binary: successively divide by 2

- In each step the remainder is the next binary digit

- The process continue until the quotient becomes zero

$$\begin{split} V &= b_{n-1} \times 2^{n-1} + b_{n-2} \times 2^{n-2} + \ldots + b_1 \times 2^1 + b_0 \times 2^0 \\ \frac{V}{2} &= b_{n-1} \times 2^{n-2} + b_{n-2} \times 2^{n-3} + \ldots + b_1 \times 2^0 + \frac{b_0}{2} \end{split}$$

#### Number representation

• Binary numbers:

$$\begin{split} B &= b_{n-1} b_{n-2} ... b_1 b_0 \\ V(B) &= b_{n-1} \times 2^{n-1} + b_{n-2} \times 2^{n-2} + ... + b_1 \times 2^1 + b_0 \times 2^0 \end{split}$$

1101

$$V = 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 13$$

$(1101)_2 = (13)_{10}$

#### Number representation

Convert (857)<sub>10</sub>

Result is  $(1101011001)_2$

#### Number representation

- The most common bases in addition to decimal are:

- base 2 (binary) { 0, 1 }

- base 8 (octal) { 0, 1, ... 7}

- base 16 (hexadecimal) { 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F }

- Reason for using octal and hexadecimal systems: useful shorthand notation for binary numbers

#### Number representation

- One octal digit represents three bits

- Conversion from binary to octal: starting from the LSB replace every group of three digits with their corresponding octal digit

- Conversion from binary to hexadecimal: starting from the LSB replace every group of four digits with their corresponding hexadecimal digit

- Conversion from octal to binary: substitute each octal digit by corresponding three bits

- Conversion from hexadecimal to binary: substitute each hex digit by four bits

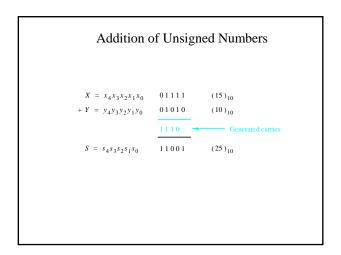

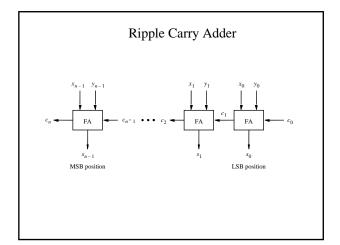

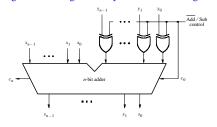

### Ripple Carry Adder

- When operands X and Y are applied as inputs to the adder, it takes some time before output sum S is valid.

- Each full-adder has a delay before its  $\boldsymbol{s}_i$  and  $\boldsymbol{c}_{i+1}$  are valid

- If this delay is  $\Delta t$  the complete sum will be valid after a delay of  $n\Delta t$

- Because of the way the carry signal "ripple" through the fulladder, this circuit is called a ripple-carry adder

### Signed Numbers

- One of the bits (usually the left-most bit) is reserved for the sign of the number.

- Usually a 1 indicates *negative* and 0 indicates *positive*.

#### Signed Numbers

- Extending the 'natural' binary representation of positive integers to negative integers can be done in at least 3 different schemes: sign-magnitude, one's complement and two's complement.

- Sign-and-magnitude: The most significant bit (MSB) is reserved to the sign, 0 is positive, 1 is negative. All other bits are used to store the magnitude in the natural representation.

- · Addition and subtraction are complicated.

- There are two representations for zero!

#### Signed Numbers

- One's complement Positive integers are like in the natural representation, negative numbers are obtained by complementing each bit of the corresponding positive number (i.e. the absolute value).

- There are two representations for zero! Bitwise addition of N and -N gives -0.

- Positive integers still have MSB = 0, and negative integers have MSB=1.

- 1's complement of an n-bit negative number K is obtained by subtracting its equivalent positive number P from 2<sup>n</sup>-1

- K<sub>1</sub>=(2<sup>n</sup>-1)-P

|           | Positive                  |    |                       | Negative Integers    |                |

|-----------|---------------------------|----|-----------------------|----------------------|----------------|

| ⊦N        | Integers<br>(all systems) | -N | Sign and<br>Magnitude | 2's Complement<br>N* | 1's Complement |

| +0        | 0000                      | -0 | 1000                  | _                    | 1111           |

| <b>-1</b> | 0001                      | -1 | 1001                  | 1111                 | 1110           |

| -2        | 0010                      | -2 | 1010                  | 1110                 | 1101           |

| -3        | 0011                      | -3 | 1011                  | 1101                 | 1100           |

| -4        | 0100                      | -4 | 1100                  | 1100                 | 1011           |

| -5        | 0101                      | -5 | 1101                  | 1011                 | 1010           |

| -6        | 0110                      | -6 | 1110                  | 1010                 | 1001           |

| -7        | 0111                      | -7 | 1111                  | 1001                 | 1000           |

|           |                           | -8 |                       | 1000                 |                |

#### Signed Numbers

- Two's complement Like one's complement, but negative numbers are having 1 added after complementation.

- Bitwise addition of N and -N gives 0 if you ignore the carry out of the MSB.

- Positive integers still have MSB = 0, and negative integers have MSB=1. Only one representation for zero!

- 2's complement of an n-bit negative number K is obtained by subtracting its equivalent positive number P from 2<sup>n</sup>

- K<sub>2</sub>=2<sup>n</sup>-P

#### 2's complement signed numbers

$$B=b_{n-1}b_{n-2}...b_1b_0$$

$$V = (-b_{n-1} \times 2^{n-1}) + b_{n-2} \times 2^{n-2} + ... + b_1 \times 2^1 + b_0 \times 2^0$$

Largest negative number: -2n-1

Largest positive number: 2<sup>n-1</sup> -1

#### Signed Numbers

- Relationship between 2's complement and 1's complement

- $K_2 = K_1 + 1$

- A simple way of finding the 2's complement is to find 1's complement and add 1

- Rule for finding 2's complement:

- Given signed number B=b<sub>n-1</sub>b<sub>n-2</sub>...b<sub>1</sub>b<sub>0</sub>

- 2's complement:  $K=k_{n-1}k_{n-2}...k_1k_0$

- Examine bits of B from right to left, copy all bits of B that are 0 and the first bit that is 1, then complement the rest of the bits

## 1's complement addition

#### Addition and Subtraction

- Addition of 1's complement numbers might need a correction

- Time needed to add two 1's complement numbers may be twice as long as time needed to add two unsigned numbers

#### 2's complement addition

### Radix-complement schemes

- Complements general theory

- The r's complement of an n-digit number N in base r is:  $K_r \!\!= r^n \text{-} N \qquad \qquad \text{for } N \neq 0$

- (0 for N=0)

- The (r-1)'s complement,  $\boldsymbol{K}_{r\text{-}1}$  is defined as:  $\boldsymbol{K}_r\text{=} (r^n\text{-}1)\text{-}N$

- The concept of subtracting a number by adding its radixcomplement is general

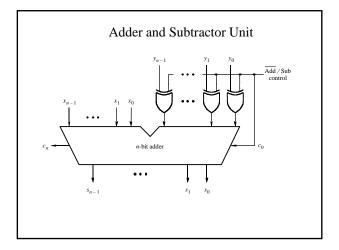

## 2's complement subtraction

### Arithmetic Overflow

- If n bits are used to represent signed numbers, result must be in the range  $-2^{n-1}$  to  $2^{n-1}-1$

- If the result does not fit in this range, we say that arithmetic overflow has happened

- We should be able to detect overflow

- The key to determining the overflow is carry-out from MSB position and carry-out from the sign bit

- If they are the same no overflow has happened.

$$overflow = c_{n-1} \oplus c_n$$

#### Arithmetic Overflow

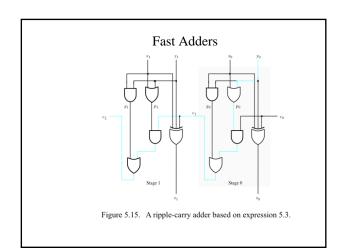

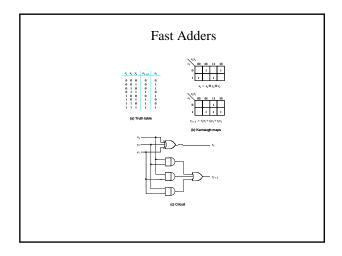

#### Fast Adders

$$c_{i+1} = x_i y_i + x_i c_i + y_i c_i$$

$$c_{i+1} = x_i y_i + (x_i + y_i) c_i$$

$$c_{i+1} = g_i + p_i c_i$$

$$g_i = x_i y_i$$

$$p_i = x_i + y_i$$

$$c_{i+1} = g_i + p_i g_{i-1} + p_i p_{i-1} g_{i-2} + .... + p_i p_{i-1} ... p_2 p_1 g_0 + p_i p_{i-1} ... p_1 p_0 c_0$$

### Performance Issue

- Speed of any circuit is limited by the longest delay along the paths through the circuit

- This is called the critical path delay

- Critical path for the ripple adder is from input y, through the XOR gate and through the carry circuit of each stage.

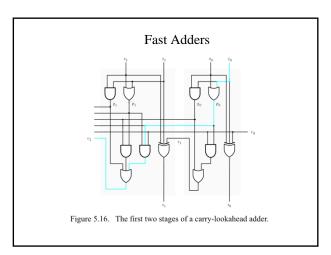

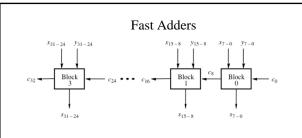

#### Fast Adders

- In an n-bit carry-look ahead adder the final carry-out signal would be produced after three gate delays

- The total delay in an n-bit carry-look ahead adder is four gate delays.

- Complexity of an n-bit carry look ahead adder increases rapidly as n becomes larger

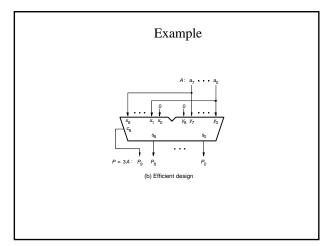

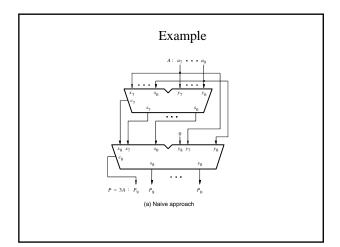

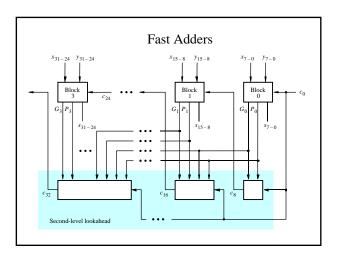

- We can use a hierarchical approach in designing large adders.

#### Fast Adders

$c_8 = g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4 + p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2 + \\ p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 c_0$

$P_0 = p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0$

$$\begin{split} G_0 &= g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4 + p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2 + p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0 \end{split}$$

$$c_8 = G_0 + P_0 c_0$$

$$c_{16} = G_1 + P_1 c_8 = G_1 + P_1 G_0 + P_1 P_0 c_0$$

Figure 5.17. A hierarchical carry-lookahead adder with ripple-carry between blocks.

#### Fast Adders

- A faster circuit can be designed in which a second-level carrylook-ahead is performed to produce quickly the carry signals between blocks.

- Instead of producing a carry-out signal from the most significant bit of the block, each block produces generate and propagate signals for the entire block

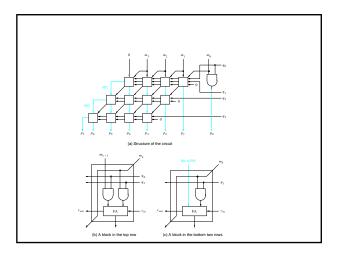

#### **Technology Considerations**

- So far we assumed gates with any number of inputs can be used.

- Fan-in is limited to a small number

- More gates should be used to implement the logic

- Example: max fan-in is four

$$\begin{split} c_8 &= g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4 + p_7 p_6 p_5 p_4 g_3 + p_7 p_6 p_5 p_4 p_3 g_2 + \\ p_7 p_6 p_5 p_4 p_3 p_2 g_1 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 g_0 + p_7 p_6 p_5 p_4 p_3 p_2 p_1 p_0 c_0 \end{split}$$

$$\begin{split} c_8 &= (g_7 + p_7 g_6 + p_7 p_6 g_5 + p_7 p_6 p_5 g_4) + \\ [p_7 p_6 p_5 p_4 (g_3 + p_3 g_2 + p_3 p_2 g_1 + p_3 p_2 p_1 g_0)] + \\ (p_7 p_6 p_5 p_4) (p_3 p_2 p_1 p_0) c_0 \end{split}$$

- Because fan-in limitation reduces the speed of carry-lookahead adder, some devices with low fan-in include dedicated circuit for implementing fast adders

- Example: FPGA

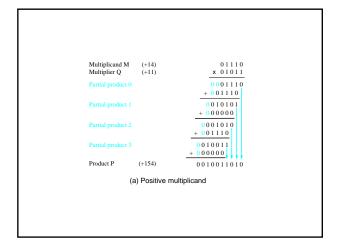

## Multiplication of unsigned numbers

Each multiplier bit is examined: if 1, a shifted version of the multiplicand is added to form the partial product; if zero nothing is added

## Multiplication

- A number is multiplied by  $2^k$  by shifting it left by k bit positions

- This is true both for unsigned and signed numbers

- Shifting to the right by k bit, is equivalent to dividing by  $2^k \\$

- For unsigned numbers the empty bit positions are filled with zero.

- For signed numbers, in order to preserve the sign, the empty bit positions are filled with the sign bit

## Multiplication of unsigned numbers

(b) Multiplication for implementation in hardware

- B=011000=24

- B/2=001100=12

- B/4=000110=6

- B=101000=-24

- B/2=110100=-12

- B/4=111010=-6

$$M = m_{3}m_{2}m_{1}m_{0}$$

$$Q = q_{3}q_{2}q_{1}q_{0}$$

$$PP0 = pp0_{3}pp0_{2}pp0_{1}pp0_{0}$$

$$PP0 \qquad 0 \quad pp0_{3} \quad pp0_{2} \quad pp0_{1} \quad pp0_{0}$$

$$+ \quad m_{3}q_{1} \quad m_{2}q_{1} \quad m_{1}q_{1} \quad m_{0}q_{1} \quad 0$$

$$PP1 \qquad pp1_{4} \quad pp1_{3} \quad pp1_{2} \quad pp1_{1} \quad pp1_{0}$$

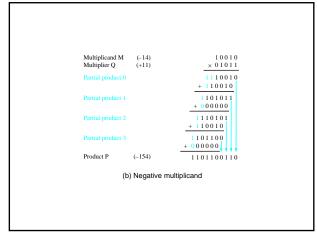

## Multiplication of Signed Numbers

- If multiplier is positive essentially the same scheme as unsigned numbers can be used

- Since shifting the multiplicand to the left results in one of the operands having n+1 bits, the addition has to be performed using the second operand represented in n+1 bits

- An n bit signed number is represented as an n+1 bit number by replicating the sign bit

- Replication of the sign bit is called sign extension

#### Fixed point

- A fixed point number consists of integer and fraction parts.

- The position of radix point is fixed

$$B = b_{n-1}b_{n-2}...b_1b_0b_{-1}b_{-2}...b_{-k}$$

$$V(B) = \sum_{i=-k}^{n-1} b_i \times 2^i$$

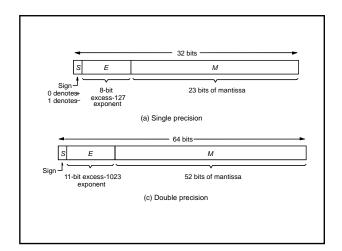

#### Floating point

- Fixed point numbers: limited range

- Floating point: numbers are represented by a mantissa and an exponent: Mantissa x R<sup>Exponent</sup>

- Normalized: radix point is the right of fist nonzero digit

- Example: 5.234 x 10<sup>43</sup>

- For binary R=2

- How mantissa and exponent are represented has been standardized by IEEE

- Single precision (32 bits) and double precision (64 bits)

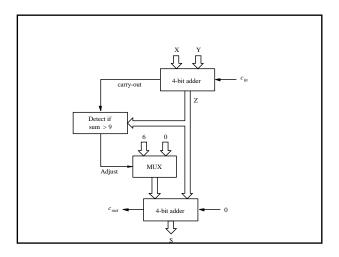

#### **BCD**

- BCD representation was used in some early computers

- Drawback: complexity of circuits that perform arithmetic operations

- BCD addition:

- X and Y two BCD digits (each four bits)

- S=X+Y

- If  $X + Y \le 9$  the addition is the same as the addition of 2 unsigned binary numbers

- If X+Y > 9 the result requires two BDC digits and the fourbit sum may be incorrect.

- Value=(+ or -)1.M x2<sup>E-127</sup>

- Double precision

- Exponent=E-1023

Value=(+ or -)1.M x2<sup>E-1023</sup>

## Binary coded decimal (BCD)

- Each digit in a decimal number is represented by its binary

- Since there are 10 digits we need 4 bits per digit

| Decimal digit | $\operatorname{BCD}$ code |

|---------------|---------------------------|

| 0             | 0000                      |

| 1             | 0001                      |

| 2             | 0010                      |

| 3             | 0011                      |

| 4             | 0100                      |

| 5             | 0101                      |

| 6             | 0110                      |

| 7             | 0111                      |

| 8             | 1000                      |

| 9             | 1001                      |

#### ASCII code

- ASCII code: the most popular code for representing information in digital systems used for letters numbers and some control characters.

- Control characters: those needed in computer systems to handle and transfer data, e.g., return character

- ACII representation of numbers is not convenient for arithmetic operations

- It is best to covert ASCII numbers to binary for arithmetic operations

| Bit<br>positions                   | Bit positions 654                      |                 |                          |                          |              |                                    |                        |     |  |  |

|------------------------------------|----------------------------------------|-----------------|--------------------------|--------------------------|--------------|------------------------------------|------------------------|-----|--|--|

| 3210                               | 000                                    | 001             | 010                      | 011                      | 100          | 101                                | 110                    | 111 |  |  |

| 0000                               | NUL                                    | DLE             | SPACE                    | 0                        | 0            | P                                  | ,                      | P   |  |  |

| 0001                               | SOH                                    | DC1             | 1                        | 1                        | A            | Q                                  |                        | q   |  |  |

| 0010                               | STX                                    | DC2             |                          | 2                        | В            | R                                  | Ъ                      | r   |  |  |

| 0011                               | ETX                                    | DC3             | *                        | 3                        | C            | S                                  | С                      | 8   |  |  |

| 0100                               | EOT                                    | DC4             | 8                        | 4                        | D            | T                                  | d                      | t   |  |  |

| 0101                               | ENQ                                    | NAK             | %                        | 5                        | $\mathbf{E}$ | U                                  | e                      | u   |  |  |

| 0110                               | ACK                                    | SYN             | &c                       | 6                        | F            | v                                  | f                      | v   |  |  |

| 0111                               | BEL                                    | ETB             | ,                        | 7                        | G            | w                                  | g                      | w   |  |  |

| 1000                               | BS                                     | CAN             | (                        | 8                        | H            | X                                  | h                      | x   |  |  |

| 1001                               | HT                                     | EM              | )                        | 9                        | 1            | Y                                  | i                      | У   |  |  |

| 1010                               | LF                                     | SUB             |                          |                          | J            | z                                  | j                      | z   |  |  |

| 1011                               | VT                                     | ESC             | +                        | ;                        | K            | [                                  | k                      | {   |  |  |

| 1100                               | FF                                     | FS              | ,                        | <                        | L            | \                                  | 1                      | 1   |  |  |

| 1101                               | CR                                     | GS              | -                        | -                        | M            | ]                                  | $\mathbf{m}$           | }   |  |  |

| 1110                               | SO                                     | RS              |                          | >                        | N            |                                    | $\mathbf{n}$           |     |  |  |

| 1111                               | SI                                     | US              | /_                       | ?                        | 0            | _                                  | 0                      | DEL |  |  |

| NUL                                | Null/Idle                              |                 | SI                       |                          |              | Shift                              |                        |     |  |  |

| SOH                                | Start of h                             |                 | Di                       |                          |              | Data link escape                   |                        |     |  |  |

| STX                                | Start of t                             |                 |                          | C1-DC                    |              | Devio                              |                        |     |  |  |

|                                    |                                        |                 |                          | Negative acknowledgement |              |                                    |                        |     |  |  |

| EOT                                | End of tr                              | ansmiss         |                          |                          |              |                                    | Synchronous idle       |     |  |  |

| ACQ Acknowledgement CAN C          |                                        |                 | End of transmitted block |                          |              |                                    |                        |     |  |  |

|                                    |                                        |                 |                          |                          |              |                                    | Cancel (error in data) |     |  |  |

| BEL                                | Audible signal                         |                 |                          | EM                       |              | End of medium                      |                        |     |  |  |

| BS Back space<br>HT Horizontal tab |                                        |                 | SUB                      |                          |              | Special sequence                   |                        |     |  |  |

|                                    |                                        |                 |                          |                          | Escape       |                                    |                        |     |  |  |

| LF                                 | Line feed<br>Vertical tab<br>Form feed |                 |                          | GS<br>RS                 |              | File separator                     |                        |     |  |  |

| VT                                 |                                        |                 |                          |                          |              | Group separator                    |                        |     |  |  |

| FF                                 |                                        |                 |                          |                          |              | Record separator<br>Unit separator |                        |     |  |  |

| CR                                 |                                        | Carriage return |                          |                          |              |                                    |                        |     |  |  |

| SO                                 | Shift out                              |                 | D                        |                          |              | Delete/Idle                        |                        |     |  |  |

| Bit position                       | s of code format = 6 5 4 3 2 1 0       |                 |                          |                          |              |                                    |                        |     |  |  |

### ASCII code

- ASCII uses 7-bit, natural size in computer systems is one-byte (8-bits)

- Two common ways on going to 8-bits

- Set the eight bit to 0

- Use the eight-bit to indicate the parity of the other bits

- Even parity: the parity bit is given a value such that total number of 1's is even

- Odd parity: the parity bit is given a value such that total number of 1's is odd

- Even parity generator:  $p = x_6 \oplus x_5 \oplus ... \oplus x_0$

- Parity checker:  $c = p \oplus x_6 \oplus x_5 \oplus ... \oplus x_0$