### EE 3CL4, §6 1/101

Tim Davidson

Compensators

Lead

compensation

Lead Compensate

Lead Compensato example

compensatio and steady-state

Lag

Compensation

Design via Root

Locus

Lag compensator example

Prop. vs Lead

Insights

Lead-Lag

Lead-Lag Compensate

A mundicular

# EE3CL4:

# Introduction to Linear Control Systems

Section 6: Design of Lead and Lag Controllers using Root Locus

Tim Davidson

McMaster University

Winter 2020

### EE 3CL4, §6 2/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensate example

Cascade compensatio and steady-state errors

Compensation

Design via Boot

Lag compensator example

vs Lag

Lead-Lag compensation

Lead-Lag Compensator example

Δ prelud

### **Outline**

- 1 Compensators

- 2 Lead compensation Design via Root Locus Lead Compensator example

- 3 Cascade compensation and steady-state errors

- 4 Lag Compensation

Design via Root Locus

Lag compensator example

- 5 Prop. vs Lead vs Lag

- 6 Insights

- Lead-Lag compensation Lead-Lag Compensator example

- 8 A prelude

### EE 3CL4, §6 4/101

#### Tim Davidson

### Compensators

Lead compensation Design via Root

Lead Compensati example

cascade compensation and steady-state errors

### Lag

Compensation

Design via Root

Lag compensator example

To a Contact

Lead-Lag

Lead-Lag Compensator example

A prelude

# Compensators

- Early in the course we provided some useful guidelines regarding the relationships between the pole positions of a system and certain aspects of its performance

- Using root locus techniques, we have seen how the pole positions of a closed loop can be adjusted by varying a parameter

- What happens if we are unable to obtain that performance that we want by doing this?

- Ask ourselves whether this is really the performance that we want

- Ask whether we can change the system, say by buying different components

- seek to compensate for the undesirable aspects of the process

### EE 3CL4, §6 5/101

#### Tim Davidson

### Compensators

#### Lead

compensation

Lead Compensate

example

compensation and steady-state

errors

Compensation

Design via Root

Lag compensator example

Prop. vs Lead vs Lag

Insights

### Lead-Lag

Lead-Lag Compensato example

A prelude

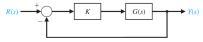

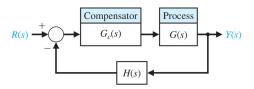

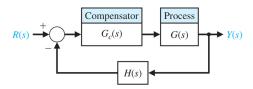

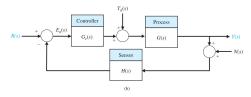

## Cascade compensation

- Usually, the plant is a physical process

- If commands and measurements are made electrically, compensator is often an electric circuit

- General form of the (linear) compensators we will consider is

$$G_c(s) = \frac{K_c \prod_{i=1}^{M} (s + z_i)}{\prod_{j=1}^{n} (s + p_j)}$$

- Therefore, the cascade compensator adds open loop poles and open loop zeros

- These will change the shape of the root locus

### EE 3CL4, §6 6/101

Tim Davidson

### Compensators

### Lead

Compensation

Design via Root

Lead Compensate

Cascade compensatio and steady-state errors

### Lag

Compensation

Design via Root

Lag compensator example

Prop. vs Lea

Insights

### Lead-Lag

Lead-Lag Compensato example

A prelude

# Compensator design

- Where should we put new poles and zeros to achieve desired performance?

- · That is the art of compensator design

- We will consider first order compensators of the form

$$G_c(s) = rac{\mathcal{K}_c(s+z)}{(s+

ho)} = rac{ ilde{\mathcal{K}}_c(1+s/z)}{(1+s/

ho)}, \quad ext{where } ilde{\mathcal{K}}_c = \mathcal{K}_c z/

ho$$

- with the pole -p in the left half plane

- and the zero, -z in the left half plane, too

- For reasons that will soon become clear

- when |z| < |p|: phase lead network

- when |z| > |p|: phase lag network

#### Tim Davidson

Compensators

### Lead

compensation

Lead Compensat

Cascade compensatio and

steady-state errors

### l an

### Compensation Design via Root

Locus

Lag compensator example

Prop. vs Le

Insights

### Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

## Lead compensation

$$G_c(s) = \frac{K_c(s+z)}{(s+p)}$$

with |z| < |p|. That is, zero closer to origin than pole

Let  $p = 1/\tau_p$  and  $z = 1/(\alpha_{\text{lead}}\tau_p)$ . Since z < p,  $\alpha_{\text{lead}} > 1$ . Define  $\tilde{K}_c = K_c z/p = K_c/\alpha_{\text{lead}}$ . Then

$$G_c(s) = rac{K_c(s+z)}{(s+

ho)} = rac{ ilde{K}_c(1+lpha_{\mathsf{lead}} au_p s)}{(1+ au_p s)}$$

### EE 3CL4, §6 9/101

### Tim Davidson

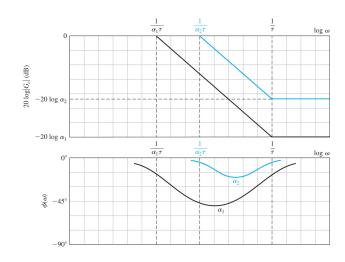

### Lead compensation

Lag compensator

Lead-Lag

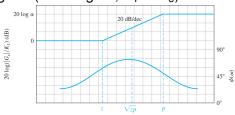

Frequency response:

$$G_c(j\omega) = rac{ ilde{K}_c(1+j\omegalpha_{\mathsf{lead}} au_p)}{(1+j\omega au_p)}$$

Bode diagram (in the figure,  $K_1 = K_c$ )

ω (log scale)

• Between  $\omega = z$  and  $\omega = p$ ,  $|G_c(j\omega)| \approx K_c \omega \alpha_{\text{lead}} \tau_p$

What kind of operator has a frequency response with magnitude proportional to  $\omega$ ? Differentiator

Note that the phase is positive. Hence "phase lead"

### EE 3CL4, §6 10/101

### Tim Davidson

Compensator

## Lead compensation

Design via Root Locus

Lead Compensator example

Cascade compensation and steady-state

errors

### Lag

Design via Root

Lag compensator example

Prop. vs Leavs Lag

Insights

### Lead-Lag compensatio

Lead-Lag Compensate

A prolude

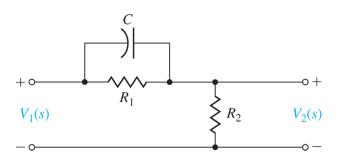

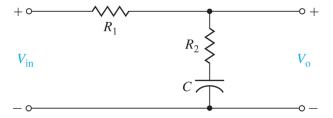

## A passive phase lead network

Homework: Show that  $\frac{V_2(s)}{V_1(s)}$  has the phase lead characteristic

### EE 3CL4, §6 11/101

#### Tim Davidson

Compensator

## Lead compensation

Design via Root Locus

Lead Compensator example

Cascade compensation and steady-state

and steady-state errors

Lag

Compensation

Design via Root

Lag compensator

example

Insight

Lead-Lag

Lead-Lag Compensate

A proludo

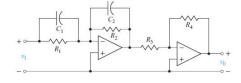

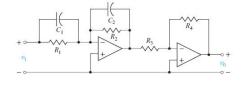

# Active lead and lag networks

Here's an example of an active network architecture.

$$\begin{aligned} \text{Lead or lag} \qquad & G_c = \frac{R_4 R_2 (R_1 C_1 s \, + \, 1)}{R_3 R_1 (R_2 C_2 s \, + \, 1)} \\ \text{Lead if } & R_1 C_1 \, > \, R_2 C_2 \\ \text{Lag if } & R_1 C_1 \, < \, R_2 C_2 \end{aligned}$$

EE 3CL4, §6 12/101

Tim Davidson

Compensator

compensation

Design via Root

Lead Compensate example

cascade compensation and steady-state errors

Lag Compensati

Locus

Lag compensator

Prop. vs Lea vs Lag

Insight

Lead-Lag compensation

Lead-Lag Compensato example

A prelude

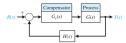

# Principles of Lead design via Root Locus

- The compensator adds poles and zeros to the P(s) in the root locus procedure.

- Hence we can change the shape of the root locus.

- If we can capture desirable performance in terms of positions of closed loop poles

- then compensator design problem reduces to:

- changing the shape of the root locus so that these desired closed-loop pole positions appear on the root locus

- finding the gain that places the closed-loop pole positions at their desired positions

- What tools do we have to do this?

- Phase criterion and magnitude criterion, respectively

#### Tim Davidson

Compensator

compensation

Design via Root

Lead Compensate

Lead Compensati example

compensation and steady-state errors

Lag

Compensation

Design via Root

Locus

Lag compensato example

vs Lag

Insights

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

### **Root Locus Principles**

- The point  $s_0$  is on the root locus of P(s) if  $1 + KP(s_0) = 0$ .

- In first order compensator design with  $G(s) = \frac{K_G \prod_{i=1}^M (s+z_i)}{\prod_{j=1}^n (s+p_j)}$  and  $G_c(s) = \frac{K_c(s+z)}{(s+p)}$ , we have  $P(s) = \frac{(s+z)}{(s+p)} \frac{\prod_{i=1}^M (s+z_i)}{\prod_{j=1}^n (s+p_j)}$  and  $K = K_c K_G$ . We will restrict attention to the case of K > 0

- Phase cond.  $s_0$  is on root locus if  $\angle P(s_0) = 180^{\circ} + \ell 360^{\circ}$ :

$$\sum_{i=1}^{M} (\text{angle from } -z_i \text{ to } s_0) - \sum_{j=1}^{n} (\text{angle from } -p_j \text{ to } s_0)$$

$$+ (\text{angle from } -z \text{ to } s_0) - (\text{angle from } -p \text{ to } s_0)$$

$$= 180^{\circ} + \ell 360^{\circ}$$

• Mag. cond. If  $s_0$  satisfies phase condition, the gain that puts a closed-loop pole at  $s_0$  is  $K = 1/|P(s_0)|$ :

$$K = \frac{\prod_{j=1}^{n} (\text{dist from } -p_j \text{ to } s_0)}{\prod_{j=1}^{M} (\text{dist from } -z_j \text{ to } s_0)} \times \frac{(\text{dist from } -p \text{ to } s_0)}{(\text{dist from } -z \text{ to } s_0)}$$

EE 3CL4, §6 14/101

Tim Davidson

Compensators

Lead

Design via Root Locus

Lead Compensator example

compensation and steady-state errors

Compensation

Design via Root

Lag compensator example

Prop. vs L vs Lag

nsights

Lead-Lag compensatio

Lead-Lag Compensator example

A preluc

# RL design: Basic procedure

- 1 Translate design specifications into desired positions of dominant poles

- Sketch root locus of uncompensated system to see if desired positions can be achieved

- 3 If not, choose the positions of the pole and zero of the compensator so that the desired positions lie on the root locus (phase criterion), if that is possible

- 4 Evaluate the gain required to put the poles there (magnitude criterion)

- 6 Evaluate the total system gain so that the steady-state error constants can be determined

- 6 If the steady state error constants are not satisfactory, repeat

This procedure enables relatively straightforward design of systems with specifications in terms of rise time, settling time, and overshoot; i.e., the transient response.

For systems with steady-state error specifications, Bode (and Nyquist) methods may be more straightforward (later)

### EE 3CL4, §6 15/101

Tim Davidson

Compensator

compensation

Design via Root

Lead Compensator example

compensatio and steady-state

Lag Compensatio

Lag compensator

example

Insights

Lead-Lag compensatio

Lead-Lag Compensator example

A prelude

## Lead Comp. example

Consider a case with  $G(s) = \frac{1}{s(s+2)}$  and H(s) = 1. Design a lead compensator to achieve:

- damping coefficient  $\zeta \approx$  0.45 and

- velocity error constant  $K_v = \lim_{s \to 0} sG_c(s)G(s) \ge 20$

- swift transient response (small settling time)

### What to do?

- Can we achieve this with proportional control?

- If not we will attempt lead control

### EE 3CL4, §6 16/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

Compensat

Design via Boot

Lag compensator

example

Insights

Lead-Lag

Lead-Lag Compensate example

A prelude

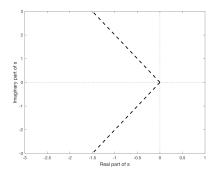

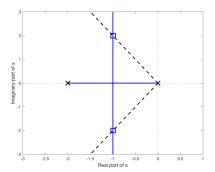

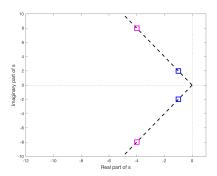

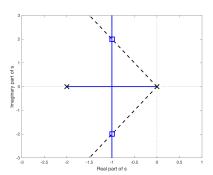

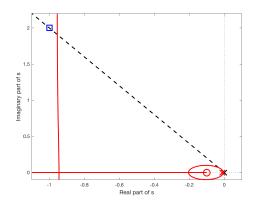

## Attempt prop. control

- Closed loop poles that correspond to  $\zeta=0.45$  lie on rays of angle  $\cos^{-1}(0.45)\approx 60^\circ$  to neg. real axis

- Sketch them

### EE 3CL4, §6 17/101

### Tim Davidson

Compensators

compensatio

Design via Root

Lead Compensator example

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Locus

Lag compensator example

. . . . .

Lead-Lag

Lead-Lag Compensator example

A prelude

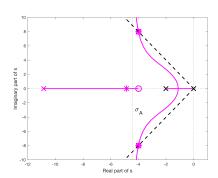

# Attempt prop. control, II

• Add sketch of root locus of  $\frac{1}{s(s+2)}$

- Is there an intersection? Yes

- What is the value of  $K = K_{amp}K_G$  that puts closed-loop poles at intersection point?

### EE 3CL4, §6 18/101

### Tim Davidson

### Compensators

compensation Design via Root

### Lead Compensator example

cascade compensation and steady-state errors

### Lag

Compensation

Design via Root

Locus

Lag compensator example

Prop. vs Lea

### Insight

### Lead-Lag compensation

Lead-Lag Compensato example

A prelude

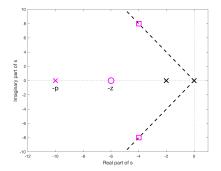

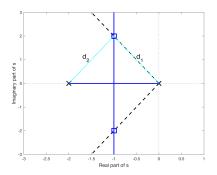

# Attempt prop. control, III

• That gain is  $K = \frac{\prod \text{distances from OL poles}}{\prod \text{distances from OL zeros}}$

- $K = d_1 d_2 = 5$ .

- Since  $K_G = 1$ ,  $K_{amp} = 5$ .

### EE 3CL4, §6 19/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Lag compensator example

Prop. vs Lea

Insights

Lead-Lag compensation

Lead-Lag Compensato example

A prelude

# Assessing our prop. design

- $K_{amp} = 5$ .

- Place actual closed loop poles on the root locus (asterisks)

- As expected, they are at the target locations (open squares)

- What is the corresponding K<sub>V</sub>?

- $K_v = \lim_{s \to 0} sG_c(s)G(s) = \frac{K_{amp}}{2} = 2.5$ :(

- Do the closed-loop poles have responses that decay quickly? No,  $T_s \approx 4 \text{s}$

### EE 3CL4, §6 20/101

#### Tim Davidson

Design via Root

#### Lead Compensator example

Design via Root

Lag compensator

Lead-Lag

A prelude

## Prop. control, step response

### EE 3CL4, §6 21/101

#### Tim Davidson

Compensators

compensation

Design via Root

Locus

Lead Compensator example

compensation and steady-state

Compensation

Design via Root

Lag compensator example

Prop. vs Leavs Lag

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

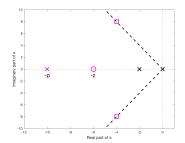

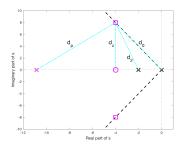

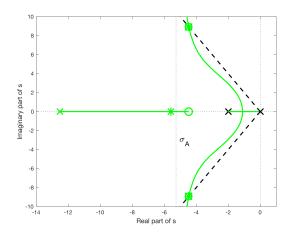

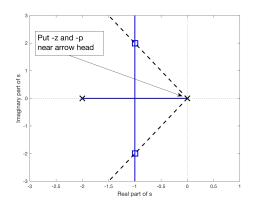

# Lead compensated design

- Where should the closed-loop poles be?  $\cos^{-1}(0.45) \approx 60^{\circ}$

- Note that the settling time is not specified; it only needs to be small. This provides design flexibility.

- However, we need a large  $K_{\nu}$  which will require large gain. Need desired positions far from open loop poles.

- Let's start with desired roots at  $-4 \pm j8$  (purple squares)

- This pair has  $T_s = 1$ s and  $\omega_n = \sqrt{4^2 + 8^2} \approx 8.9$

### EE 3CL4, §6 22/101

Tim Davidson

Compensator

compensation

Design via Root

Lead Compensator

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Lag compensator

Prop. vs Leavs Lag

Insights

Lead-Lag compensation

Lead-Lag Compensato example

A prelude

## How to choose z, p and $K_c$

- · Lead design questions:

- How do we choose z and p to ensure that there exists a gain that will put closed loop poles at the squares?

- Once we have done that, how do we find the gain that puts the closed-loop poles at the squares?

### EE 3CL4, §6 23/101

Tim Davidson

Compensators

Lead compensatio

Lead Compensator

Cascade compensation and steady-state errors

Lag Compensation

Compensation

Design via Root

Locus

Lag compensator example

example

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

# How to choose z, p and $K_c$

- We want squares to be on the root locus

- That is, if s<sub>0</sub> denotes the position of one of the squares, we want 1 + G<sub>c</sub>(s<sub>0</sub>)G(s<sub>0</sub>) = 1 + KP(s<sub>0</sub>) = 0

- In other words, we want  $P(s_0) = -1/K$

- Separating that complex-valued equation into magnitude and phase components, we want

- $\angle P(s_0) = 180^\circ$ ; phase criterion

- $|P(s_0)| = 1/K$ ; magnitude criterion

### Lead Compensator

Cascade compensation and steady-state errors

Lag

Design via Root Locus

Lag compensator example

Prop. vs Lead vs Lag

Insights

Lead-Lag

Lead-Lag Compensate example

A prelude

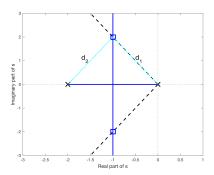

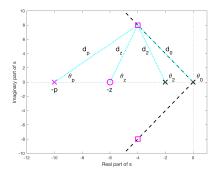

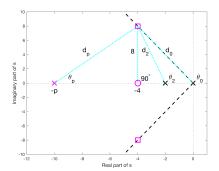

# How to choose z, p and $K_c$

• To find z and p we use the phase criterion

$$\sum$$

(angles from OL zeros)  $-\sum$  (angles from OL poles)  $= 180^{\circ}$

$\implies \theta_z - \theta_0 - \theta_2 - \theta_p = 180^{\circ}$

• Then, to find  $K_c$  we use the magnitude criterion

$$K = K_c K_G = \frac{\prod \text{distances from OL poles}}{\prod \text{distances from OL zeros}} = \frac{d_0 d_2 d_p}{d_z}$$

### EE 3CL4, §6 25/101

#### Tim Davidson

### Compensators

Lead compensation

### Lead Compensator

Cascade compensation and steady-state errors

### Lad

Compensation

Design via Root

Lag compensator example

Prop ve Lea

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

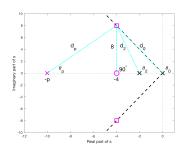

# How to choose z and p

- Can we start to think of this geometrically, rather than algebraically?

- Phase condition equation at  $s_0$ :  $\theta_z \theta_\rho = 180^\circ + \theta_0 + \theta_2$

- One linear equation, two unknowns. Many solutions

- However, we can find out something about  $\angle G_c(s_0)$

- Since  $G_c(s) = K_c \frac{s+z}{s+p}$ , with  $K_c > 0$ ,  $\angle G_c(s_0) = \angle (s_0 + z) \angle (s_0 + p) = \theta_z \theta_p$  Can you see this angle in the figure? It is  $\phi_c$

- Since  $90^{\circ} < \theta_0, \ \theta_2 < 180, \implies 0 < \phi_c < 180$

- That is, we need a phase lead compensator

- What does that say about z and p? -p < -z

### EE 3CL4, §6 26/101

#### Tim Davidson

Compensators

compensation

Design via Root

Locus

Lead Compensator example

compensatio and steady-state errors

Lag Compensatio Design via Root

Lag compensator example

vs Lag

Insights

Lead-Lag compensation

Lead-Lag Compensate

A prelude

# Simplifying rule of thumb

- What are good choices for z and p amongst those that provide the right amount of phase lead?

- Simplifying rule of thumb: When amount of phase lead required at  $s_0$  is less than  $90^\circ$ , place zero on the real axis "underneath" the desired closed-loop pole positions.

- When applicable, this reduces the complexity of the design procedure; now we only have to design the pole position; often a reasonable choice

- Can iterate on zero position as needed

### EE 3CL4, §6 27/101

#### Tim Davidson

#### Compensator

Lead compensation

### Lead Compensator example

Cascade compensatio and steady-state errors

### Compensa:

Design via Root Locus

Lag compensator example

Prop vs Lo

Insights

### Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

# How to choose p

With rule of thumb in place

Find  $\theta_p$  using

$$\sum$$

angles from OL zeros  $-\sum$  angles from OL poles  $=180^{\circ}$   $\sim 90 - (116 + 104 + \theta_p) = 180$

$\implies \theta_n \approx 50$

• Hence, pole at  $-p = -4 - 8/\tan(\theta_p) \approx -10.86$

### EE 3CL4, §6 28/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

Lag Compensatio

Design via Root Locus

Lag compensator example

vs Lag

Insights

Lead-Lag

Lead-Lag Compensate example

A prelude

## Checking our work

Does the root locus for the compensated system go through the desired positions?

### EE 3CL4, §6 29/101

Tim Davidson

Compensators

compensation

Lead Compensator

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Lag compensator

Prop. vs Le

Insights

### Lead-Lag

Lead-Lag Compensato example

A prelude

# How to choose $K_c$

What is the gain that puts closed-loop poles in the boxes? Recall

$$K = K_c K_G = \frac{\prod \text{distances from OL poles}}{\prod \text{distances from OL zeros}} = \frac{d_0 d_2 d_p}{d_z}$$

- In this example  $K_G = 1$

- Therefore,  $K_c = \frac{d_0 d_2 d_p}{d_z} \approx \frac{8.94(8.25)(10.54)}{8} \approx 97.1$

### EE 3CL4, §6 30/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensatio and steady-state

Lag

Compensation

Design via Root

Lag compensator

Prop. vs Lea

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

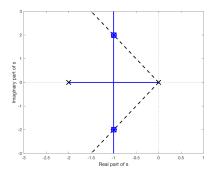

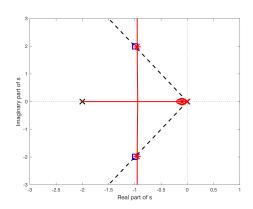

# Summarizing initial design

- Our compensator is  $G_c(s) = \frac{97.1(s+4)}{(s+10.86)}$

- The compensated open loop is  $G_c(s)G(s)=rac{97.1(s+4)}{s(s+2)(s+10.86)}$

- Mark all closed-loop poles on the root locus (asterisks)

Note that conjugate pair hit the target (as designed),

and that the real pole is not far from the (open/closed loop) zero

• Velocity constant:  $K_{\nu} = \lim_{s \to 0} sG_{c}(s)G(s) \approx 17.9$  :(

### EE 3CL4, §6 31/101

Tim Davidson

Compensator

Compensation

Design via Root

Lead Compensator example

compensatio and steady-state errors

Lag Compensation Design via Root

Lag compensator example

. . . . .

Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

### What to do now?

- We tried hard, but did not achieve the design specs

- Let's go back and re-examine our choices

- Zero position of compensator was chosen via rule of thumb

- Can we do better?

Yes, but two parameter design becomes trickier.

- What were other choices that we made?

- We chose desired poles to be of magnitude  $\omega_n \approx 8.9$

- We could choose them to be further away;

larger gain to get there (and faster transient response)

- By how much?

- Show that when desired poles have  $\omega_n=10$  as well as the required  $\zeta\approx 0.45$ , then the choice of  $z\approx 4.47$ ,  $p\approx 12.5$  and  $K_C\approx 125$  results in  $K_V\approx 22.3$

### EE 3CL4, §6 32/101

#### Tim Davidson

Compensators

Lead compensatio

Lead Compensator

example

compensati and steady-state errors

Lag Comp

Design via Root Locus

Lag compensator example

vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensate

A prelude

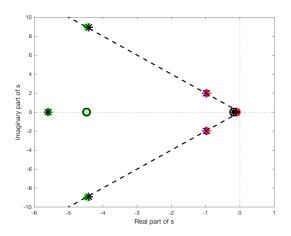

### Root Locus, new lead comp.

### EE 3CL4, §6 33/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

errors Lag

Design via Root

Locus

Lag compensator example

vs Lag

Insights

Lead-Lag compensation

Lead-Lag Compensato

A prolude

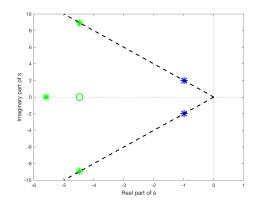

## Comparisons to prop. design

### Closed-loop pole and zero positions

EE 3CL4, §6 34/101

Tim Davidson

Compensators

Lead compensation Design via Root

Lead Compensator example

compensation and steady-state errors

Lag Compensation Design via Root

Lag compensator example

Insights

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

## Comparisons

|                            | Propcontr.           | Lead contr.                                                 |

|----------------------------|----------------------|-------------------------------------------------------------|

| Controller, $G_C(s)$       | 5                    | $\frac{125(s+4.47)}{(s+12.5)}$                              |

| OL TF, $G_C(s)G(s)$        | $\frac{5}{s(s+2)}$   | $\frac{125(s+4.47)}{(s+12.5)} \; \frac{1}{s(s+2)}$          |

| CL TF, $\frac{Y(s)}{R(s)}$ | $\frac{5}{s(s+2)+5}$ | $\frac{125(s+4.47)}{s(s+2)(s+12.5)+125(s+4.47)}$            |

| CL poles                   | −1 ± <i>j</i> 2      | $-4.47 \pm j8.94, -5.59$                                    |

| CL zeros                   | $\infty, \infty$     | $-4.47, \infty, \infty$                                     |

| CL TF, again               | $\frac{5}{s^2+2s+5}$ | $\frac{131(1+0.013s)}{s^2+8.94s+100} - \frac{1.71}{s+5.59}$ |

- Complex conjugate poles still dominate

- Closed-loop zero at -4.47 (which is also an open-loop zero) reduces impact of closed-loop pole at -5.59;

residue of that pole in partial fraction expansion is small

### EE 3CL4, §6 35/101

#### Tim Davidson

Compensators

### Lead

compensation

Design via Root

Lead Compensator

### example

compensat and steady-stat

steady-stat errors

### Lag

Design via Root Locus

Lag compensator example

Prop. vs Lea

Insights

### Lead-Lag

Lead-Lag Compensate

A prelude

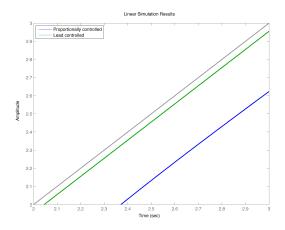

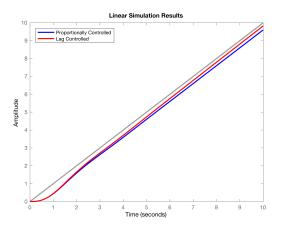

# New lead comp., ramp response

### EE 3CL4, §6 36/101

#### Tim Davidson

Design via Root

Lead Compensator

### example

# Design via Root

Lag compensator

Lead-Lag

A prelude

# New lead comp., ramp response, detail

### EE 3CL4, §6 37/101

#### Tim Davidson

#### Lead Compensator example

Lag compensator

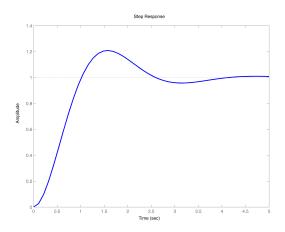

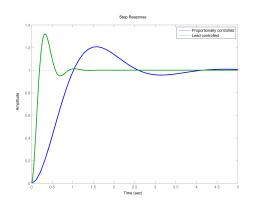

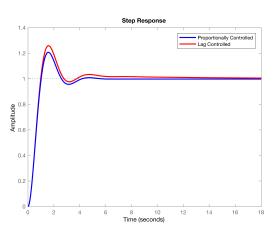

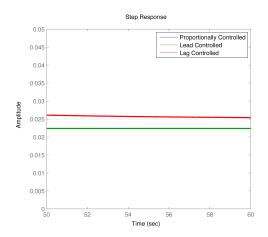

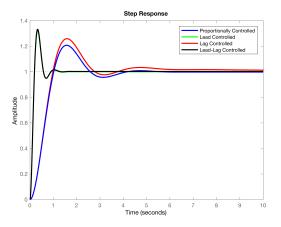

# New lead comp., step response

Note faster settling time than prop. controlled loop, However, the CL zero has increased the overshoot a little

Perhaps we should go back and re-design for  $\zeta \approx 0.40$ in order to better control the overshoot

EE 3CL4, §6 38/101

Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

compensatio and steady-state errors

Lag Compensatio Design via Root

Lag compensator example

vs Lag

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

### **Outcomes**

- Root locus approach to phase lead design was reasonably successful in terms of putting dominant poles in desired positions; e.g., in terms of  $\zeta$  and  $\omega_n$

- We did this by positioning the pole and zero of the lead compensator so as to change the shape of the root locus

- However, root locus approach does not provide independent control over steady-state error constants (details upcoming)

- That said, since lead compensators reduce the DC gain (they resemble differentiators), they are not normally used to control steady-state error.

- The goal of our lag compensator design will be to increase the steady-state error constants, without moving the other poles too far

#### EE 3CL4, §6 40/101

#### Tim Davidson

Compensator

compensatio

compensation

Lead Compensate

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Lag compensator example

vs Lag

Insight

Lead-Lag compensation

Lead-Lag Compensato example

A prelude

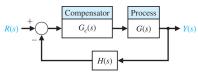

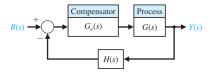

# Cascade compensation

- Throughout this lecture, and all the discussion on cascade compensation, we will consider the case in which H(s) = 1.

- We will consider first order compensators of the form

$$G_c(s) = rac{\mathcal{K}_c(s+z)}{(s+p)}$$

with the pole, -p, and the zero, -z, both in the left half plane

- when |z| < |p|: phase lead network

- when |z| > |p|: phase lag network

#### Tim Davidson

Compensator

compensation

compensatio

Lead Compensate

Cascade compensation and steady-state errors

#### Lag

Compensation

Design via Root

Lag compensator

Prop ve Lo

Inciahto

Lead-Lag

Lead-Lag Compensator example

A prelud

### Steady-state errors

If closed loop stable, steady state error for input R(s):

$$e_{ss} = \lim_{t \to \infty} e(t) = \lim_{s \to 0} s \frac{R(s)}{1 + G_C(s)G(s)}$$

Let

$$G(s)=rac{K_G\prod_i(s+z_i)}{\prod_i(s+p_i)}$$

and consider  $G_C(s)=rac{K_C(s+z)}{(s+p)}$

- Consider the case in which G(s) is a type-0 system.

- Steady state error due to a step r(t) = Au(t):  $e_{ss} = \frac{A}{1 + K_{cons}}$ , where

$$K_{\text{posn}} = G_C(0)G(0) = \frac{K_C z}{\rho} \frac{K_G \prod_i z_i}{\prod_i \rho_i}$$

- Note that for a lead compensator, z/p < 1,

- So lead compensation may degrade steady-state error performance

Acida, Mhat about a laf atan far Tima > 1 ayatama?

#### EE 3CL4, §6 42/101

Tim Davidson

Compensators

Lead compensation

Lead Compensator example

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Lag compensator

example example

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

# Steady-state error

- Now, consider the case in which G(s) is a type-1 system,  $G(s) = \frac{K_G \prod_i (s+z_i)}{s \prod_i (s+p_i)}$

- Steady-state error due to a ramp r(t) = At: e<sub>ss</sub> = A/K<sub>v</sub>, where the velocity constant is

$$K_V = \lim_{s \to 0} sG_c(s)G(s) = \frac{K_C z}{p} \frac{K_G \prod_i z_i}{\prod_i p_i}$$

- Once again, lead compensation may degrade steady-state error performance

- Is there a way to increase the value of these error constants while leaving the closed loop poles in essentially the same place as they were in an uncompensated system? Perhaps |z| > |p|?

#### Tim Davidson

#### Compensators

#### Lead

compensatio

Design via Roo

Lead Compensate example

# Cascade compensatio and steady-state

and steady-state errors

#### Lag

Compensation

Design via Boot

Locus

Lag compensator example

Prop. vs Lea vs Lag

Insights

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

# Lag compensation

$$G_c(s) = rac{K_c(s+z)}{(s+p)}$$

with |z| > |p|. That is, pole closer to origin than zero

Let  $z=1/\tau_z$  and  $p=1/(\alpha_{\text{lag}}\tau_z)$ . Since z>p,  $\alpha_{\text{lag}}>1$ . Define  $\tilde{K}_c=K_cz/p=K_c\alpha_{\text{lag}}$ . Then

$$G_c(s) = rac{\mathcal{K}_c(s+z)}{(s+

ho)} = rac{ ilde{\mathcal{K}}_c(1+ au_z s)}{(1+lpha_{ ext{lag}} au_z s)}$$

Tim Davidson

Compensator

compensation

Lead Compensate example

Cascade compensatio and steady-state

errors

Compensation

Locus .

Lag compensator example

Incidate

Lead-Lag

Lead-Lag Compensator example

A prelude

# Frequency response

$$G_c(j\omega) = rac{ ilde{K}_C(1+j\omega au_z)}{(1+j\omegalpha_{ ext{lag}} au_z)}$$

### Magnitude

- Low frequency gain:  $\tilde{K}_C$

- Corner freq. in denominator at  $\omega_p = p = 1/(\alpha_{lag}\tau_z)$

- Corner freq. in numerator at  $\omega_z = z = 1/\tau_z$

- $\omega_p < \omega_z$

- High frequency gain:  $\tilde{K}_C/\alpha_{\text{lag}} = K_C$

### Phase

- $\phi(\omega) = \operatorname{atan}(\omega \tau_z) \operatorname{atan}(\alpha_{\operatorname{lag}} \omega \tau_z)$

- At low frequency:  $\phi(\omega) = 0$

- At high frequency:  $\phi(\omega) = 0$

- In between: negative, with max. lag at  $\omega = \sqrt{ZD}$

#### EE 3CL4, §6 46/101

#### Tim Davidson

Compensator

compensation

Design via Root

Lead Compensator

Cascade

compensation and steady-state

#### Lag Compensation

Design via Root Locus

Lag compensator example

vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

# Bode Diagram, with $\tilde{K}_c = 1$

Note integrative characteristic

#### EE 3CL4, §6 47/101

#### Tim Davidson

Design via Root

Lead Compensator

#### Lag Compensation

Design via Root

Lag compensator

Lead-Lag example

A prelude

### A passive phase lag network

#### EE 3CL4, §6 48/101

#### Tim Davidson

Compensators

#### Load

compensation

Design via Root

Lead Compensator

example example

Cascade compensation and steady-state

steady-state errors

#### Lag Compensation

Design via Root

Lag compensator

Prop. vs Lea

Insights

### Lead-Lag

Lead-Lag Compensate

A proludo

# Active lead and lag networks

Here's an example of an active network architecture.

$$\begin{aligned} \text{Lead or lag} \qquad & G_c = \frac{R_4 R_2 (R_1 C_1 s \, + \, 1)}{R_3 R_1 (R_2 C_2 s \, + \, 1)} \\ \text{Lead if } & R_1 C_1 > R_2 C_2 \\ \text{Lag if } & R_1 C_1 < R_2 C_2 \end{aligned}$$

#### EE 3CL4, §6 49/101

Tim Davidson

Compensators

compensation

Design via Root

Lead Compensato example

compensation and steady-state errors

Compensat

Design via Root

Locus

Lag compensator

example

Prop vs Le

Insights

Lead-Lag compensatio

Lead-Lag Compensator example

A prelude

# Lag compensator design

- Lag compensator:  $G_c(s) = K_c \frac{s+z}{s+p}$ . with |z| > |p|.

- Recall position error constant for compensated type-0 system and velocity error constant for compensated type-1 system:

$$K_{\text{posn}} = \frac{K_C z}{p} \frac{K_G \prod_i z_i}{\prod_j p_j}, \qquad K_{\text{v}} = \frac{K_C z}{p} \frac{K_G \prod_i z_i}{\prod_j p_j}$$

where in the latter case the product in the denominator is over the non-zero poles.

### **Design Principles**

- We don't try to reshape the uncompensated root locus.

- We just try to increase the value of the desired error constant by a factor  $\alpha_{\text{lag}} = z/p$  without moving the existing closed-loop poles (well not much)

- Reshaping was the goal of lead compensator design

EE 3CL4, §6 50/101

Tim Davidson

Compensator

Lead compensation Design via Root Locus

Cascade compensation and

and steady-state errors

Compensation

Design via Root

Lag compensator

Lag compensator example

Incidhto

Lead-Lag

Lead-Lag Compensato example

A prelude

# Lag compensator design

### Design principles:

- Don't reshape the root locus

- Adding the open loop pole and zero from the compensator should only result in a small change to the angle criterion for any (important) point on the uncompensated root locus

- Angles from compensator pole and zero to any (important) point on the locus must be similar

- Pole and zero must be close together

- Increase value of error constant:

- Want to have a large value for  $\alpha_{lag} = z/p$ .

- How can that happen if z and p are close together?

- Only if z and p are both small, i.e., close to the origin

EE 3CL4, §6 51/101

Tim Davidson

Compensators

compensation

Design via Root

Lead Compensate

compensation and steady-state errors

Lag

Compensation

Design via Root

Lag compensator example

Prop. vs Le

nsights

Lead-Lag

Lead-Lag Compensator example

A preluc

# Lag comp. design via Root

- 1 Obtain the root locus of uncompensated system

- 2 From transient performance specs, locate suitable dominant pole positions *on that locus*

- 3 Obtain the loop gain for these points,  $K_{unc} = K_{amp}K_G$ ; hence the (closed-loop) steady-state error constant

- **4** Calculate the necessary increase. Hence  $\alpha_{lag} = z/p$

- **6** Place pole and zero close to the origin (with respect to desired pole positions), with  $z = \alpha_{\text{lag}} p$ . Typically, choose z and p so that their angles to desired poles differ by less than 1°.

- 6 Set  $K_C = K_{amp}$

What if there is nothing suitable at step 2?

- · Perhaps do lead compensation first,

- then lag compensation on lead compensated plant.

i.e., design a lead-lag compensator

Lead Compensato

Cascade compensation and steady-state errors

Lag Compensat

Design via Root Locus

Lag compensator example

Prop. vs Lea

nsights

Lead-Lag

Lead-Lag Compensator example

A prelude

# Example

Let's consider, again, the case with  $G(s) = \frac{1}{s(s+2)}$ . Design a lag compensator to achieve damping coefficient  $\zeta \approx 0.45$  and velocity error constant  $K_V \ge 20$

**Note:** we will get a different closed loop from our lead design.

First step, obtain uncompensated root locus, and locate desired dominant pole locations

EE 3CL4, §6 53/101

Tim Davidson

Compensators

compensation

Design via Root

Lead Compensate

Cascade compensatio and steady-state

Lag

Compensation

Design via Root

Lag compensator example

vs Lag

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

# Uncompensated root locus

In this example, this step is the same as the first step in our lead design example

- So, yes, it is possible to achieve a damping coefficient  $\zeta \approx$  0.45 using proportional control

- What is the gain that puts the closed loop poles there?

#### EE 3CL4, §6 54/101

#### Tim Davidson

Lag compensator example

Lead-Lag

# Finding the gain for prop. control

• That gain is  $K = K_{amp}K_G = \frac{\prod distances from OL poles}{\prod distances from OL zeros}$

- $K = d_1 d_2 = 5$ .

- Since  $K_G = 1$ ,  $K_{amp} = 5$ .

EE 3CL4, §6 55/101

Tim Davidson

Compensator

Lead compensation Design via Root Locus

Lead Compensati example

compensatio and steady-state errors

Lag Compensation

Lag compensator example

Prop vs Lea

Incidhte

Lead-Lag

Lead-Lag Compensate example

A prelude

# Evaluate the velocity error constant, and choose z/p

- Velocity error constant of uncompensated loop:  $K_{v,\text{unc}} = \lim_{s \to 0} sG_c(s)G(s) = K_{\text{amp}}K_G/2$

- Since  $K_G = 1$  and  $K_{amp} = 5$ ,  $K_{v,unc} = 2.5$

- In order to obtain  $K_{\nu} \ge 20$ , the factor by which we need to increase  $K_{\nu, \text{unc}}$  by at least 20/2.5 = 8

- That implies that in the design of our lag controller, we should choose pole and zero such that z/p ≥ 8,

- where z is chosen to be close to the origin with respect to dominant closed-loop poles, so that the root locus doesn't change too much near those dominant closed-loop poles

#### EE 3CL4, §6 56/101

#### Tim Davidson

Compensators

#### Lead

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

errors

Lag

Design via Root

Lag compensator example

Prop. vs Leavs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

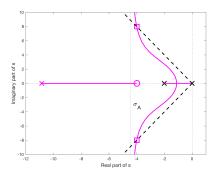

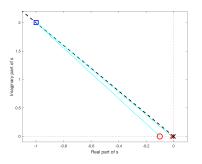

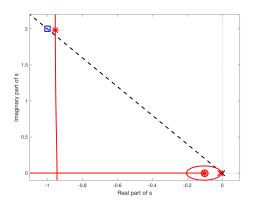

### Positioning zero and pole

with  $z/p \ge 8$

#### EE 3CL4, §6 57/101

#### Tim Davidson

Compensators

compensatio

Design via Root

Lead Compensato

Cascade compensationand steady-state errors

Lag Compensation

Lag compensator

example

Insiahts

Lead-Lag

Lead-Lag Compensator example

A prelude

# Zooming in

• Try -z = -0.1, along with -p = -1/80.

- Angles from new open-loop zero and open-loop pole to desired closed-loop pole position are pretty close.

- Therefore, their effects will nearly cancel out in phase criterion at values of s near box

- As a result, compensated root locus should pass close by the desired positions

#### EE 3CL4, §6 58/101

#### Tim Davidson

Compensators

#### اممما

compensation Design via Root

Lead Compensato

Cascade compensation and steady-state

Lag

Design via Root Locus

Lag compensator example

Prop. vs Lea

Insights

Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

### Lag compensated root locus

Yes, indeed, the lag compensated root locus does pass close by the desired positions

### EE 3CL4, §6 59/101

#### Tim Davidson

Compensators

### Lead

compensation

Lead Compensator

example example

compensation and steady-state

Lag

Design via Root

Lag compensator example

Prop. vs Lea

Insights

Lead-Lag

Lead-Lag Compensato

A prelude

# Lag compensated root locus, zoomed in

#### EE 3CL4, §6 60/101

#### Tim Davidson

Compensators

Lead compensation Design via Root Locus

Lead Compensato example

Cascade compensation and steady-state

Lag Compensation

Design via Root Locus

Lag compensator example

vs Lag

Insights

Lead-Lag

Lead-Lag Compensato example

A prolude

# Choosing K<sub>c</sub>

- Choose  $K_c$  to be the same as  $K_{amp}$  from the uncompensated design

- That is,  $K_c = 5$

- Plot actual closed loop poles on the locus (asterisks)

#### EE 3CL4, §6 61/101

#### Tim Davidson

Compensators

### Lead

compensation

Lead Compensator

Cascade

compensationand steady-state errors

### Lag

Design via Root

### Lag compensator example

Prop. vs Lea vs Lag

Insights

### Lead-Lag

Lead-Lag Compensati example

A prelude

### Zoomed in

#### EE 3CL4, §6 62/101

#### Tim Davidson

Compensators

compensation

Lead Compensator example

Cascade compensation and steady-state

errors

Lag

Compensatio

Design via Root

Locus

Lag compensator example

Prop. vs Lea vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensate

A prolude

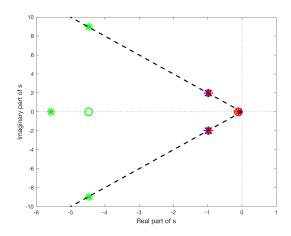

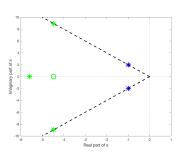

# Comparisons to prop. design

### Closed-loop pole and zero positions

#### EE 3CL4, §6 63/101

Tim Davidson

Compensators

Lead compensation Design via Root

Locus Lead Compensat example

compensatio and steady-state errors

Compensation

Lag compensator example

Incidhto

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

# Comparisons

|                            | Propcontr.           | Lag contr.                                                                   |

|----------------------------|----------------------|------------------------------------------------------------------------------|

| Controller, $G_C(s)$       | 5                    | $\frac{5(s+0.1)}{(s+1/80)}$                                                  |

| OL TF, $G_C(s)G(s)$        | $\frac{5}{s(s+2)}$   | $\frac{5(s+0.1)}{(s+1/80)} \frac{1}{s(s+2)}$                                 |

| CL TF, $\frac{Y(s)}{R(s)}$ | $\frac{5}{s(s+2)+5}$ | $\frac{5(s+0.1)}{s(s+2)(s+1/80)+5(s+0.1)}$                                   |

| CL poles                   | −1 ± <i>j</i> 2      | $-0.955 \pm j$ 1.979, $-0.104$                                               |

| CL zeros                   | $\infty, \infty$     | $-0.1,\infty,\infty$                                                         |

| CL TF, again               | $\frac{5}{s^2+2s+5}$ | $\frac{4.999(1+7\times10^{-4}s)}{s^2+1.909s+4.827} + \frac{-0.004}{s+0.104}$ |

- Complex conjugate poles still dominate

- Closed-loop zero at -0.1 (which is also an open-loop zero) reduces impact of closed-loop pole at -0.104;

residue of that pole in partial fraction expansion is small

#### EE 3CL4, §6 64/101

#### Tim Davidson

Compensators

### Lead

compensation

Design via Root

Lead Compensator

#### 0----

compensation

and steady-state errors

#### Lag

Compensation

Design via Root

### Lag compensator example

Prop. vs Lead

Insights

### Lead-Lag

Lead-Lag Compensate example

A prelude

### Ramp response

#### EE 3CL4, §6 65/101

#### Tim Davidson

Compensators

### Lead

compensation

Design via Root

Lead Compensator example

# Cascade compensation

and steady-state

### Lan

Design via Root

### Lag compensator example

Prop. vs Lead vs Lag

Insights

### Lead-Lag

Lead-Lag Compensate

A prelude

### Ramp response, detail

#### EE 3CL4, §6 66/101

#### Tim Davidson

Compensators

compensatio

Lead Compensator

Cascade compensatio and steady-state errors

Compensation

Design via Root

Lag compensator example

Pron vs Lea

Insights

Lead-Lag compensation

Lead-Lag Compensato example

A prelude

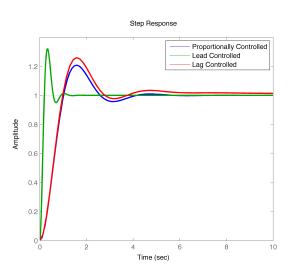

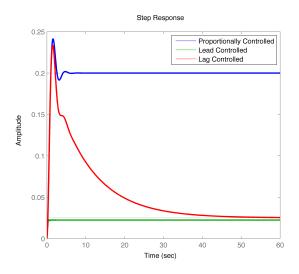

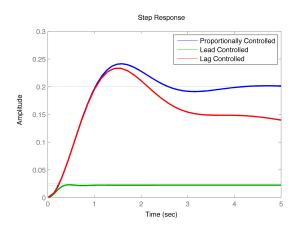

# Step response

Note longer settling time of lag controlled loop, and slight increase in overshoot, due to extra closed-loop pole-zero pair that do not quite cancel each other out

#### EE 3CL4, §6 68/101

#### Tim Davidson

Compensator

compensation

Lead Compensato

cascade compensation and steady-state errors

#### Lag Compensati

Design via Root

Lag compensator example

Prop. vs Lead

vs Lag

Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

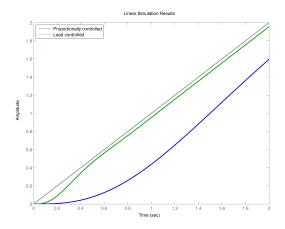

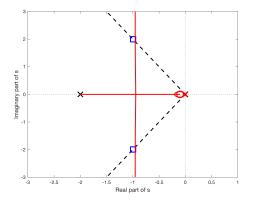

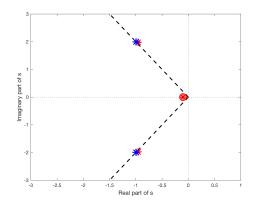

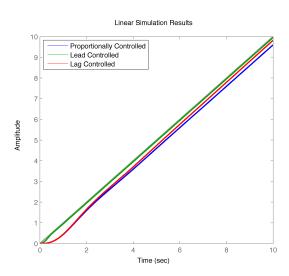

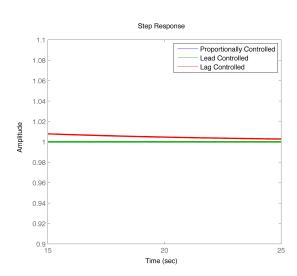

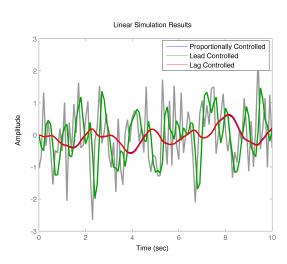

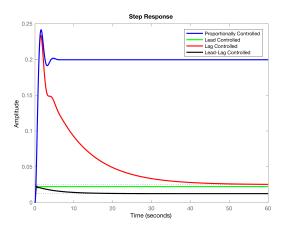

# Prop, Lead, Lag Design Comparisons

Recall the design example that we have considered for lead and lag designs:

For  $G(s) = \frac{1}{s(s+2)}$  and with H(s) = 1, design a compensator to achieve:

- damping coefficient  $\zeta \approx 0.45$  and

- velocity error constant  $K_{\nu} = \lim_{s \to 0} sG_{c}(s)G(s) \ge 20$

- swift transient response (small settling time)

#### We have done

- · Proportional design (blue), which failed to meet specifications

- Lead design (green)

- Lag design (red)

#### EE 3CL4, §6 69/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

Lag Compensation

Design via Root Locus

Lag compensator example

Prop. vs Lead vs Lag

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

# Prop, Lead, Lag Design Comparisons

### Closed-loop pole and zero positions

#### EE 3CL4, §6 70/101

#### Tim Davidson

#### Compensators

### compensati

Design via Root

Lead Compensate example

Cascade compensation and steady-state errors

#### Lag

Compensation

Design via Root

Lag compensator

example

Prop. vs Lead

# vs Lag

### Lead-Lag

Lead-Lag Compensato example

A prelude

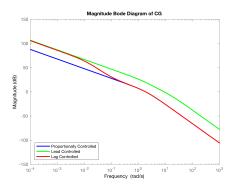

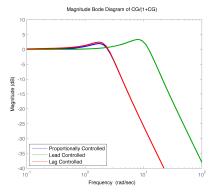

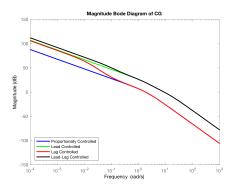

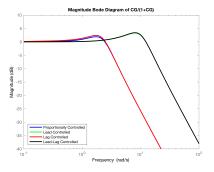

# Bode, open loop, $G_c(j\omega)G(j\omega)$

- Recall  $K_v = \lim_{s \to 0} sG_c(s)G(s)$

- Low freg's: curves approx linear with slope -20dB/dec.

- That is  $20 \log_{10}(|G_c(j\omega)G(j\omega)|) \approx 20 \log_{10}(A) 20 \log_{10}(\omega)$

- That means  $G_c(j\omega)G(j\omega) \approx \frac{A}{j\omega}$ ;  $G_c(s)G(s) \approx \frac{A}{s}$ ;  $\Longrightarrow K_{\nu} = A$

- Thus, when low freq. slope is -20dB/dec, "higher" curves mean larger  $K_{\nu}$

Lag compensator example

Prop. vs Lead

vs Lag

Lead-Lag

Lead-Lag Compensate example

A prelude

# Low freq. analysis

- Let's now do that analytically

- For each design, for small s,  $G_c(s)G(s) \approx rac{A}{s}$

- $G(s) = \frac{1}{s(s+2)}$

- **Prop:**  $G_c(s) = 5$ . Hence, A = 2.5

- **Lead:**  $G_c(s) = \frac{125(s+4.47)}{(s+12.5)}$ . Hence, A = 22.3

- Lag:  $G_c(s) = \frac{5(s+0.1)}{(s+1/80)}$ . Hence, A = 20

Lag compensator example

Prop. vs Lead

vs Lag

Lead-Lag compensatio

Lead-Lag Compensator example

A prelude

# Prop, Lead, Lag Design Comparisons

For given example:  $G(s) = \frac{1}{s(s+2)}$ ,  $\zeta \approx 0.45$

| 3(3+2)              |                      |                                                             |                                                                              |  |

|---------------------|----------------------|-------------------------------------------------------------|------------------------------------------------------------------------------|--|

|                     | Propcontr.           | Lead contr.                                                 | Lag contr.                                                                   |  |

| $G_C(s)$            | 5                    | $\frac{125(s+4.47)}{(s+12.5)}$                              | $\frac{5(s+0.1)}{(s+1/80)}$                                                  |  |

| $\frac{Y(s)}{R(s)}$ | $\frac{5}{s^2+2s+5}$ | $\frac{131(1+0.013s)}{s^2+8.94s+100} - \frac{1.71}{s+5.59}$ | $\frac{4.999(1+7\times10^{-4}s)}{s^2+1.909s+4.827} + \frac{-0.004}{s+0.104}$ |  |

| CL poles            | −1 ± <i>j</i> 2      | $-4.47 \pm j8.94, -5.59$                                    | $-0.955 \pm j$ 1.979, $-0.104$                                               |  |

| CL zeros            | $\infty, \infty$     | $-4.47, \infty, \infty$                                     | $-0.1,\infty,\infty$                                                         |  |

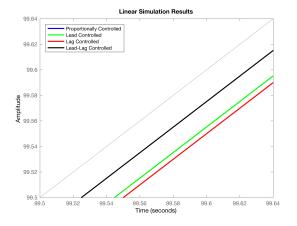

| $1/K_{\nu}$         | 0.4                  | 0.045                                                       | 0.05                                                                         |  |

- Lag design retains similar CL poles to prop. design, plus a "slow" pole with a small residue

- CL poles of lead design quite different

- Lead and lag meet  $K_{\nu}$  specification  $(1/K_{\nu} = e_{\rm ss,unit\ ramp})$

#### EE 3CL4, §6 73/101

#### Tim Davidson

#### Compensators

### Lead ..

Design via Root

Lead Compensator example

Cascade compensatio and

and steady-state errors

#### Lag

Compensation

Design via Root

Locus

Lag compensator example

# Prop. vs Lead vs Lag

Insights

### Lead-Lag

Lead-Lag Compensate

A prelude

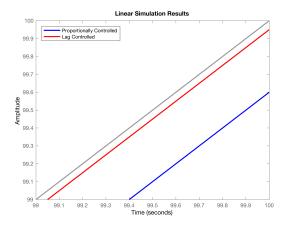

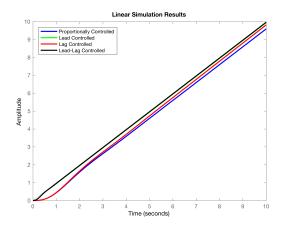

### Ramp response

#### EE 3CL4, §6 74/101

#### Tim Davidson

#### Compensators

#### Lead

compensation

Design via Root

Lead Compensator example

Cascade compensatio and

and steady-state errors

#### Lan

Compensation

Design via Root

Lag compensator example

Prop. vs Lead vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensate

A prelude

### Ramp response, detail

#### EE 3CL4, §6 75/101

#### Tim Davidson

#### Compensators

### Lead

Design via Root Locus

Lead Compensator example

compensation and steady-state

### Lag

Compensation

Design via Root

Lag compensator example

# Prop. vs Lead vs Lag

Insights

### Lead-Lag

Lead-Lag Compensate example

A prelude

# Step response

#### EE 3CL4, §6 76/101

#### Tim Davidson

#### Compensators

Lead

Design via Root

Lead Compensator

Cascade compensationand

and steady-state

Lag

Compensation

Design via Root Locus

Lag compensator example

# Prop. vs Lead vs Lag

Insights

Lead-Lag

Lead-Lag Compensate example

A prelude

# Step response, detail

#### EE 3CL4, §6 77/101

#### Tim Davidson

Compensators

#### . . . . .

compensation

Design via Root

Lead Compensator example

#### Caccad

compensation and steady-state errors

#### Lag

Design via Root

Design via Roo

Lag compensator

### Prop. vs Lead vs Lag

Insiahts

Lead-Lag

Lead-Lag Compensator example

A prelude

# Anything else to consider?

#### EE 3CL4, §6 78/101

#### Tim Davidson

Compensators

compensation

Locus

example example

compensation and steady-state

Lag

Compensation

Design via Root

Lag compensator example

Prop. vs Lead vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensato example

A prelude

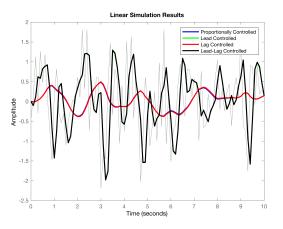

### Anything else to consider?

With H(s) = 1,

$$Y(s) = rac{G_c(s)G(s)}{1 + G_c(s)G(s)} \, R(s) + rac{G(s)}{1 + G_c(s)G(s)} \, T_d(s) \ - rac{G_c(s)G(s)}{1 + G_c(s)G(s)} \, N(s)$$

$$E(s) = rac{1}{1 + G_c(s)G(s)} R(s) - rac{G(s)}{1 + G_c(s)G(s)} T_d(s) + rac{G_c(s)G(s)}{1 + G_c(s)G(s)} N(s)$$

#### EE 3CL4, §6 79/101

#### Tim Davidson

Design via Root

Lead Compensator

Design via Root

Lag compensator

Prop. vs Lead vs Lag

Lead-Lag

A prelude

### Response to step disturbance

#### EE 3CL4, §6 80 / 101

#### Tim Davidson

Design via Root

Lead Compensator

Design via Root

Lag compensator

Prop. vs Lead

vs Lag

Lead-Lag

## Response to step disturbance, detail early

#### EE 3CL4, §6 81/101

#### Tim Davidson

Compensators

Lead

Compensation

Design via Root

Lead Compensator

Cascade compensationand steady-state

errors Lag

Compensation

Design via Root

Lag compensator example

Prop. vs Lead vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensate example

A prelude

# Response to step disturbance, detail late

Homework: Show that  $e_{ss}$  for a step disturbance is 0.2, 0.0225 and 0.025 for prop., lead, lag, respectively

#### EE 3CL4, §6 82/101

#### Tim Davidson

Compensators

#### Load

compensation

Design via Root

Lead Compensator

Lead Compensate example

Cascade compensation and

steady-state

#### .

Compensation

Design via Root

Lag compensator

Prop. vs Lead vs Lag

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

# Error due to Gaussian sensor noise

#### EE 3CL4, §6 83/101

#### Tim Davidson

Lag compensator

Prop. vs Lead

## vs Lag

Lead-Lag

# Bode diagram of $G_{C}(s)G(s)/(1+G_{C}(s)G(s))$

- Prop. and lag designs do a better job at filtering out the higher frequency noise components

- You could also see this bandwidth diff. in open loop Bode plots

- Reduced bandwidth also means slower step and ramp responses

#### EE 3CL4, §6 85/101

Tim Davidson

Compensator

compensation

Design via Root

Lead Compensate example

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Locus

Lag compensator example

Insights

Lead-Lag

Lead-Lag Compensato example

A prelude

### Insights

- If we would like to improve the transient performance of a closed loop

- We can try to place the dominant closed-loop poles in desired positions

- One approach to doing that is lead compensator design

- However, that typically requires the use of an amplifier in the compensator, and hence requires a power supply

- Broadening of bandwidth improves transient performance but exposes loop to noise

- If we would like to improve the steady-state error performance of a closed loop without changing the dominant transient features too much

- We can consider designing a lag compensator to provide the required gain

- However, that typically produces a "weak" slow pole that slows the decay to steady state

#### EE 3CL4, §6 87/101

Tim Davidson

Compensator

Lead compensation Design via Root

Lead Compensati example

compensatio and steady-state

errors

Compensation

Design via Root

Lag compensator example

Insights

Lead-Lag compensation

Lead-Lag Compensato example

A prelude

### What if we want to do more?

- What happens if we want to improve transient performance and improve steady-state error?

- For example, what if we want to design a compensator for  $G(s) = \frac{1}{s(s+2)}$  that achieves

- 1 Specified maximum overshoot; minimum value for  $\zeta$

- Specified (2%) settling time; largest (least negative) real part of closed loop pole

- 3 Specified steady-state error for ramp input; min. value for  $K_{\nu}$ , related to DC open loop "gain"

- Lead compensation gives (some) ability to address 1 and 2

- Lag compensation gives (some) ability to address 3

- What should we do?

Cascade compensation and steady-state

errors

Compensation

Design via Root

Lag compensator example

Prop. vs Lea

Insight

Lead-Lag compensation

Lead-Lag Compensato example

A prolude

### Lead-lag compensation

- Here is one thing that we can do:

- Step 1: Design a lead compensator  $G_{c,\text{lead}}(s)$  for the process G(s) to change the shape of the root locus and choose the gain so that the poles are in the desired position

- Step 2: Design a lag compensator,  $G_{c,lag}(s)$  to leave the dominant closed-loop poles of the lead-compensated process  $\tilde{G}(s) = G_{c,lead}(s)G(s)$  in approximately the position but provide extra low-frequency gain

- This is called a lead-lag controller:  $G_c(s) = G_{c,lead-lag}(s) = G_{c,lag}(s)G_{c,lead}(s)$

Tim Davidson

Compensator

compensation

Lead Compensal

Cascade compensatio and steady-state errors

Lag Compensation

Lag compensator

example

Incidhte

Lead-Lag

Lead-Lag Compensator example

A prelude

### Lead-Lag Comp. example

Consider a case with  $G(s) = \frac{1}{s(s+2)}$  and H(s) = 1. Design a compensator to achieve:

- damping coefficient  $\zeta \approx 0.45$

- dominant poles with real parts  $\approx -4.5$ , so that they correspond to a 2% setting time of  $\approx \frac{4}{4.5} \sim 0.9$ s

- velocity error constant  $K_v = \lim_{s \to 0} sG_c(s)G(s) \ge 40$

### What to do?

- Our second lead compensator (with the green root locus),  $G_{c,\text{lead}}(s) = \frac{125(s+4.47)}{(s+12.5)}$ , achieves the first two requirements

- However, that design has  $K_{\nu} \approx 22.3$

- Now design a lag compensator to increase  $K_{\nu}$  to 40

#### EE 3CL4, §6 90/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

#### Lag

Compensation

Design via Root

Lag compensator example

Prop. vs Leavs Lag

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

### Lead-Lag Design

- $G_{c,\text{lead}}(s)G(s)$  has  $K_{v}\approx 22.3$ .

- Lag compensator must increase this to around 40. Therefore, we need  $z_{\rm lag}/p_{\rm lag}\approx 1.8$ .

- Looking at the closed loop poles of lead compensated plant (green, see also table on slide 33),

we can try

$$z_{laq} = 0.18$$

,  $p_{laq} = 0.1$ .

• Therefore  $G_{c, \text{lead-lag}}(s) = \frac{125(s+0.18)(s+4.47)}{(s+0.1)(s+12.5)}$

#### EE 3CL4, §6 91/101

#### Tim Davidson

Compensators

compensation

Design via Root

Lead Compensator example

Cascade compensation and steady-state

Compensation

Design via Root

Lag compensator

Prop. vs Leavs Lag

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

## Prop, Lead, Lag, Lead-Lag Design Comparisons

### Closed-loop pole and zero positions

#### Tim Davidson

#### Compensators

### Lead

Design via Roo

Lead Compensate

Cascade compensatio and steady-state

#### Lag

Compensation

Design via Root

Lag compensator

Prop. vs Lea

Insights

### Lead-Lag compensatio

Lead-Lag Compensator example

A prelude

### Bode, open loop, $G_c(j\omega)G(j\omega)$

- Recall  $K_v = \lim_{s\to 0} sG_c(s)G(s)$

- At low freq. slope is -20dB/dec. Hence  $G_c(s)G(s) \approx \frac{A}{s}$ . Hence,  $K_V = A$ .

- Since  $G_{c,\text{lead-lag}}(s) = \frac{125(s+0.18)(s+4.47)}{(s+0.1)(s+12.5)}$ ,  $A_{\text{lead-lag}} = 40.23$

- By comparison with slide 70 (and as seen in plot),  $A_{\text{lead-lag}} > A_{\text{lead}} \gtrsim A_{\text{lag}} > A_{\text{prop}}$

EE 3CL4, §6 93/101

Tim Davidson

Compensators

Lead compensation Design via Root

Lead Compensate example

Cascade compensation and steady-state errors

Lag

Compensation

Design via Root

Locus

Lag compensator example

vs Lag

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

### Lead, Lead-Lag Comparisons

Prop. and Lag designs are on slide 71

|                     | Lead contr.                                                  | Lead-Lag contr.                                                                                     |

|---------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| $G_C(s)$            | $\frac{125(s+4.47)}{(s+12.5)}$                               | $\frac{125(s+0.18)(s+4.47)}{(s+0.1)(s+12.5)}$                                                       |

| $\frac{Y(s)}{R(s)}$ | $\frac{131(1+0.0130s)}{s^2+8.94s+100} - \frac{1.71}{s+5.59}$ | $\frac{131(1+0.0132s)}{s^2+8.82s+99.46} - \frac{1.73}{s+5.60} + \frac{6.15\times10^{-4}}{s+0.1806}$ |

| CL poles            | $-4.47 \pm j8.94, -5.59$                                     | $-4.41 \pm j8.95, -5.60, -0.1806$                                                                   |

| CL zeros            | $-4.47,\infty,\infty$                                        | $-4.47, -0.18, \infty, \infty$                                                                      |

| 1/K <sub>v</sub>    | 0.045                                                        | 0.0249                                                                                              |

- Lead-lag design retains similar CL poles to lead design, plus a "slow" pole with very small residue

- Lead-lag will have smaller steady-state error for a ramp input.

- Anything else? Recall larger low-frequency gain

#### EE 3CL4, §6 94/101

#### Tim Davidson

#### Compensators

### Lead compensation

compensation

Design via Root

Lead Compensator example

Cascade compensation and

and steady-state errors

#### Lag

Compensation

Design via Root

Locus

Lag compensator example

Prop. vs Lea

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

### Ramp response

#### EE 3CL4, §6 95/101

#### Tim Davidson

Compensators

### Lead

compensation

Design via Root

Lead Compensator example

Cascade compensatio and stoady state

steady-state errors

### Lag

Design via Root Locus

Lag compensator example

Prop. vs Lea

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

### Ramp response, detail

#### EE 3CL4, §6 96/101

#### Tim Davidson

Compensators

### Lead ..

compensation

Design via Root

Lead Compensator example

compensati and steady-state

### Lag

Design via Root Locus

Lag compensator example

Prop. vs Lea vs Lag

Insights

Lead-Lag compensatio

Lead-Lag Compensator example

A prelude

### Step response

#### EE 3CL4, §6 97/101

#### Tim Davidson

Compensators

compensation

Lead Compensate

Cascade compensatio and steady-state

Lag Compensation

Design via Root Locus

Lag compensator example

Prop. vs Leavs Lag

Insights

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

### Response to step disturbance

Note reduced steady-state disturbance error of lead-lag design. This is due to larger  $K_{\nu}$ , which comes from larger low-frequency "gain"

EE 3CL4, §6 98/101

#### Tim Davidson

Compensators

#### Load

compensation

Design via Root

Lead Compensator

Cascade

and steady-state

errors

#### Lag

Compensation

Design via Root

Locus

Lag compensator example

Prop. vs Lea

Insights

Lead-Lag

Lead-Lag Compensator example

A prelude

# Error due to Gaussian sensor noise

#### EE 3CL4, §6 99/101

#### Tim Davidson

Compensator

compensatio

Compensatio

Design via Root

Lead Compensate example

Cascade compensation and steady-state

Lag

Compensation

Design via Root

Lag compensator

Prop. vs Lea

Insights

Lead-Lag compensation

Lead-Lag Compensator example

A prelude

# Bode diagram of $G_C(s)G(s)/(1+G_C(s)G(s))$

- Prop. and lag designs do a better job at filtering out the higher frequency noise components

- You could also see this bandwidth diff. in open loop Bode plots

- Reduced bandwidth also means slower step and ramp responses

#### EE 3CL4, §6 101/101

Tim Davidson

Lag compensator

A prelude

## A prelude to frequency-domain design

- In our design process there were connections between performance measures and the frequency responses of the open loop and the closed loop.

- Perhaps we might be able to build a design technique around Bode magnitude and phase diagrams of the open-loop transfer function, rather than the open-loop poles and zeros