# Extraction of the Induced Gate Noise, Channel Noise, and Their Correlation in Submicron MOSFETs from RF Noise Measurements

Chih-Hung Chen, Student Member, IEEE, M. Jamal Deen, Senior Member, IEEE, Yuhua Cheng, Member, IEEE, and Mishel Matloubian, Member, IEEE

Abstract—An extraction method to obtain the induced gate noise  $(\overline{i_d^2})$ , channel noise  $(\overline{i_d^2})$ , and their cross correlation  $(\overline{i_g}i_d^*)$  in submicron MOSFETs directly from scattering and RF noise measurements has been presented and verified by measurements. In addition, the extracted induced gate noise, channel noise, and their correlation in MOSFETs fabricated in 0.18- $\mu$ m CMOS process versus frequencies, bias conditions, and channel lengths are presented and discussed.

*Index Terms*—Channel noise, cross-correlation noise, induced gate noise, noise of MOSFETs, RF noise extraction.

#### I. INTRODUCTION

**■** URRENTLY, there is a trend to replace RF ICs with BJTs and GaAs FETs with deep submicron MOSFETs which have unity current-gain frequencies  $(f_T)$  of several tens of gigahertz [1]. However, for many RF ICs, low noise performance is very important. Therefore, RF noise modeling of deep submicron MOSFETs is very important for devices used in the front-end transceivers. When transistors operate in the gigahertz range, the random potential fluctuations in the channel resulting in the channel noise will be coupled to the gate terminal through the gate oxide capacitance and cause the induced gate noise, which is usually correlated with the channel noise. Because of the difficulties in the extraction of the induced gate noise and its correlation term with the channel noise, several noise models [2], [3] and simulation results [4] have been presented, but they could not be verified directly with the noise sources obtained from RF noise measurements for deep submicron MOSFETs. Therefore, obtaining the noise currents directly from RF noise measurements is crucial for the high-frequency noise modeling of deep submicron MOSFETs.

In this paper, a systematic procedure to extract the induced gate noise  $(\overline{i_g^2})$ , channel noise  $(\overline{i_d^2})$ , and their cross correlation  $(\overline{i_g}i_d^*)$  directly from the S-parameter and RF noise parameter

Manuscript received May 1, 2001; revised July 13, 2001. This work was supported in part by Conexant Systems, Inc. for device fabrication and by grants from Conexant Systems, Inc., Micronet (a federal network center of excellence in microelectronics), Mitel, Ottawa, ON, Canada, and the Natural Sciences and Engineering Research Council (NSERC) of Canada. The review of this paper was arranged by Editor J. N. Hollenhorst.

C.-H. Chen and M. J. Deen are with the Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON, Canada L8S 4K1 (e-mail: chench@mcmaster.ca).

Y. Cheng and M. Matloubian are with Conexant Systems, Inc., Newport Beach, CA 92660 USA

Publisher Item Identifier S 0018-9383(01)10108-5.

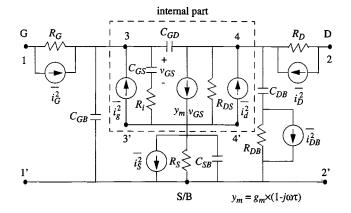

Fig. 1. RF noise model of an intrinsic MOSFET that is suitable for high-frequency circuit applications.

measurements is presented. With the help of the direct calculation technique [5], [6] for the noise parameters of transistors, the extracted noise currents are fed back to the equivalent noise model to calculate the noise parameters—minimum noise figure  $NF_{\rm min}$ , equivalent noise resistance  $R_{\rm n}$ , and optimized source reflection coefficient  $\Gamma_{\rm OPT}$ —and to compare them to the measured data for the verification of the extracted noise sources. After that, the extracted noise currents of the MOSFETs fabricated in a 0.18- $\mu$ m CMOS process versus frequency, bias condition, and channel length are presented and discussed.

## II. PROCEDURE OF NOISE EXTRACTION

Fig. 1 shows the noise model of an intrinsic MOSFET that is suitable for RF applications. It consists of two parts: an internal part (including  $C_{\rm GS}$ ,  $C_{\rm GD}$ ,  $R_i$ ,  $g_m$ ,  $R_{\rm DS}$ ,  $\overline{i_g^2}$  and  $\overline{i_d^2}$ ) and an external part which includes all the components outside of the dashed box. After the devices and dummy structures, as described in [7], are fabricated, the induced gate noise, channel noise, and their correlation in MOSFETs can be extracted by using the following 15-step procedure.

- Step 1) Measure the scattering parameters  $S_{\mathrm{DUT}}$ ,  $S_{\mathrm{OPEN}}$ ,  $S_{\mathrm{THRU1}}$  and  $S_{\mathrm{THRU2}}$  of the device-under-test (DUT), OPEN, THRU1, and THRU2 dummy structures, respectively.

- Step 2) Measure the noise parameters  $NF_{\min, DUT}$ ,  $Y_{\text{opt}, DUT}$ , and  $R_{\text{n}, DUT}$  of the DUT.

- Perform a parameter de-embedding to get the Step 3) intrinsic scattering  $(Y_{dev})$  and noise parameters  $(NF_{\text{min,dev}}, Y_{\text{opt,dev}}, \text{ and } R_{\text{n,dev}})$  [7], [8].

- Perform a parameter extraction [9] based on  $Y_{\text{dev}}$ Step 4) and other measured data to get all the element values (e.g.,  $g_m$ ,  $C_{GS}$ ,  $C_{GD}$ , etc.,) in the RF noise

- Step 5) Calculate the correlation matrix  $C_{A\mathrm{dev}}$  of the transistor based on the intrinsic noise parameters by (1), shown at the bottom of the page, where k is Boltzmann's constant,  $T_o$  is the standard reference temperature (290 K), and the asterisk denotes the complex conjugate.

- Step 6) Calculate the four-port admittance matrix  $Y_{

m extr}$  of the extrinsic part in the RF transistor model by excluding  $C_{GS}$ ,  $C_{GD}$ ,  $g_m$ ,  $R_{DS}$ , and  $R_i$  which define the intrinsic part and partition  $Y_{\text{extr}}$  as [10]

$$Y_{\text{extr}} = \begin{bmatrix} Y_{ee} & Y_{ei} \\ Y_{ie} & Y_{ii} \end{bmatrix}$$

(2)

where the submatrixes  $Y_{ee}$ ,  $Y_{ei}$ ,  $Y_{ie}$ , and  $Y_{ii}$  are  $2 \times 2$  matrixes.

- Calculate the two-port admittance  $Y_{\mathrm{intr}}$  of the in-Step 7) trinsic part in the RF transistor model.

- Step 8) Calculate the matrix D as follows:

$$D = -Y_{ei}(Y_{ii} + Y_{intr})^{-1}.$$

(3)

Convert the noise correlation matrix  $oldsymbol{C}_{oldsymbol{A} ext{dev}}$  to its Step 9) admittance form  $C_{Y

m dev}$  by using

$$C_{Y\text{dev}} = T_Y C_{A\text{dev}} T_Y^{\dagger} \tag{4}$$

where the  $\dagger$  in  $T_{oldsymbol{V}}^{\dagger}$  denotes Hermitian conjugation (transpose and complex conjugate) and the transformation matrix  $T_{\mathbf{V}}$  is given by

$$\boldsymbol{T_Y} = \begin{bmatrix} -Y_{11,\text{dev}} & 1\\ -Y_{21,\text{dev}} & 0 \end{bmatrix}. \tag{5}$$

Step 10) Calculate the admittance noise correlation matrix  $C_{Y\rm extr}$  of the extrinsic part by [11]

$$C_{Y \text{extr}} = kT(Y_{\text{extr}} + Y_{\text{extr}}^{\dagger})$$

(6)

or

$$C_{Y \text{extr}} = 2kT\Re(Y_{\text{extr}})$$

(7)

where T is the device temperature,  $\Re()$  denotes for the real part of the matrix elements and partition  $C_{oldsymbol{Y}_{ ext{extr}}}$  as

$$C_{Y\text{extr}} = \begin{bmatrix} C_{ee} & C_{ei} \\ C_{ie} & C_{ii} \end{bmatrix}$$

(8)

where the submatrixes  $m{C}_{ee}, m{C}_{ei}, m{C}_{ie},$  and  $m{C}_{ii}$  are  $2 \times 2$  matrixes.

Step 11) Calculate the admittance correlation matrix  $C_{Y\mathrm{intr}}$  of the intrinsic part in the RF transistor

$$C_{Y_{intr}} = D_i (C_{Y_{dev}} - C_{ee}) D_i^{\dagger}$$

$$- C_{ie} D_i^{\dagger} - D_i C_{ei} - C_{ii}$$

(9)

where  $D_i = D^{-1}$ .

- Step 12) Convert  $Y_{intr}$  to its chain representation  $A_{intr}$ using the conversion formula (10), shown at the bottom of the next page.

- Step 13) Convert  $C_{Y_{\mathrm{intr}}}$  to its chain matrix form  $C_{A_{\mathrm{intr}}}$

$$C_{A_{\text{intr}}} = T_A C_{V_{\text{intr}}} T_A^{\dagger}, \tag{11}$$

where  $T_A$  is given by

$$T_A = \begin{bmatrix} 0 & A_{12,\text{intr}} \\ 1 & A_{22,\text{intr}} \end{bmatrix}. \tag{12}$$

- Step 14) Calculate the noise parameters  $NF_{\min}$ ,  $Y_{\text{opt}}$ , and  $R_{\rm n}$  of the intrinsic part in the RF transistor model from the noise correlation matrix  $oldsymbol{C_{Aintr}}$  by using (13)–(15), shown at bottom of the next page, where  $\Im$ () stands for the imaginary part of elements and j is the imaginary unit.

- Step 15) Calculate the power spectral density of the channel noise  $\overline{i_d^2}$ , induced gate noise  $\overline{i_q^2}$ , and their correlation  $\overline{i_q i_d^*}$  from

$$\frac{\overline{|i_d|^2}}{\Delta f} = 4kT_oR_n|Y_{21,\text{intr}}|^2$$

$$\frac{\overline{|i_g|^2}}{\Delta f} = 4kT_oR_n$$

$$\times \left\{ |Y_{\text{opt}}|^2 - |Y_{11,\text{intr}}|^2 \right\}$$

(16)

$$+2\Re\left[(Y_{11,\text{intr}} - Y_{\text{cor}})Y_{11,\text{intr}}^*\right]$$

(17)

and

$$\frac{\overline{i_g i_d^*}}{\Delta f} = 4kT_o \left( Y_{11,\text{intr}} - Y_{\text{cor}} \right) R_n Y_{21,\text{intr}}^* \tag{18}$$

$$\boldsymbol{C_{A\text{dev}}} = 2kT_o \begin{bmatrix} R_{\text{n,dev}} & \frac{NF_{\text{min,dev}} - 1}{2} - R_{\text{n,dev}} (Y_{\text{opt,dev}})^* \\ \frac{NF_{\text{min,dev}} - 1}{2} - R_{\text{n,dev}} Y_{\text{opt,dev}} & R_{\text{n,dev}} |Y_{\text{opt,dev}}|^2 \end{bmatrix}$$

$$\frac{NF_{\text{min,dev}} - 1}{2} - R_{\text{n,dev}} (Y_{\text{opt,dev}})^*$$

$$R_{\text{n,dev}} |Y_{\text{opt,dev}}|^2$$

(1)

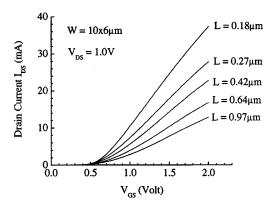

Fig. 2. Drain current ( $I_{\rm DS}$ ) versus gate voltage  $V_{\rm GS}$  characteristics for the n-type MOSFETs with channel width  $W=10\times6~\mu\mathrm{m}$  (10 fingers of width  $6 \,\mu\text{m}$ ) and lengths  $L = 0.97 \,\mu\text{m}$ , 0.64  $\mu\text{m}$ , 0.42  $\mu\text{m}$ , 0.27  $\mu\text{m}$  and 0.18  $\mu\text{m}$ , respectively, biased at a drain voltage  $V_{\rm DS}=1.0~{\rm V}.$

where

$$Y_{\rm cor}$$

is given by

$$Y_{\rm cor} = \frac{NF_{\rm min} - 1}{2R_{\rm n}} - Y_{\rm opt}.$$

(19)

### III. MEASUREMENTS AND DISCUSSIONS

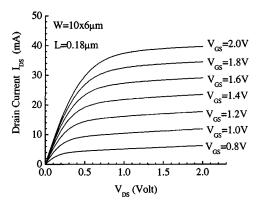

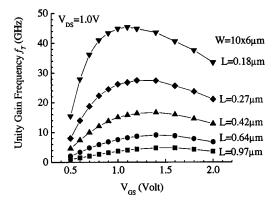

The devices-under-test (DUTs) are n-type MOSFETs with channel width  $W = 10 \times 6 \mu \text{m}$  (10 fingers) and lengths  $L = 0.97 \,\mu\text{m}, \, 0.64 \,\mu\text{m}, \, 0.42 \,\mu\text{m}, \, 0.27 \,\mu\text{m} \, \text{and} \, 0.18 \,\mu\text{m}, \, \text{respec-}$ tively, fabricated by Conexant Systems, Inc., Newport Beach, CA. Measured data were obtained by using an ATN NP5B Noise and S-Parameter Measurement Systems (0.3  $\sim$  6 GHz). All the parasitic effects from probe pads and interconnections were de-embedded from the measured s-parameters using the procedure described in [7], [8]. Figs. 2 and 3 show the measured  $I_{\rm DS}$  versus  $V_{\rm GS}$  and  $V_{\rm DS}$  characteristics to demonstrate the dc performance of the devices and Fig. 4 shows the unity gain frequency  $(f_T)$  versus bias characteristics for different channel lengths. The  $V_{\rm GS}$  bias at which the peak  $f_{\rm T}$  occurs reduces when the channel length reduces and this trend makes MOSFETs suitable for low power RF circuit designs. The measured peak  $f_{\rm T}$  of the 0.18  $\mu$ m devices is about 45 GHz.

Fig. 3. Drain current  $(I_{DS})$  versus drain voltage  $V_{DS}$  characteristics for the n-type MOSFETs with channel width  $W=10\times6~\mu\mathrm{m}$  (10 fingers of width 6  $\mu$ m) and lengths  $L=0.18~\mu$ m biased at gate voltage  $V_{\rm GS}=0.8~{\rm V},\,1.0~{\rm V},\,1.2$ V, 1.4 V, 1.6 V, 1.8 V, and 2.0 V, respectively.

Fig. 4. Unity gain frequency  $(f_T)$  versus  $V_{GS}$  characteristics from measured  $|h_{21}|$  for the n-type MOSFETs with channel width  $W=10\times6~\mu\mathrm{m}$  (ten fingers of width 6  $\mu$ m) and lengths  $L=0.97~\mu$ m, 0.64  $\mu$ m, 0.42  $\mu$ m, 0.27  $\mu$ m and 0.18  $\mu$ m, respectively, biased at  $V_{\rm DS}=1.0$  V.

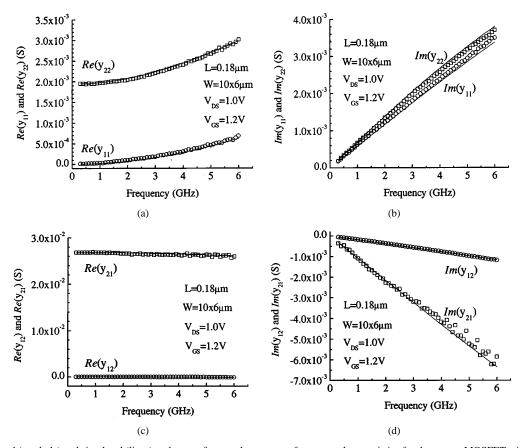

In the extraction procedure, the element values used in the RF noise model are crucial to obtain the power spectral density of the noise sources. They are directly obtained from the intrinsic y-parameters [9]. Fig. 5(a)–(d) show the measure (symbols) and simulated (lines) y-parameters of an n-type MOSFET with channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers) and length

$$A_{\text{intr}} = \frac{-1}{Y_{21,\text{intr}}} \begin{bmatrix} Y_{22,\text{intr}} & 1\\ Y_{11,\text{intr}} Y_{22,\text{intr}} - Y_{12,\text{intr}} Y_{21,\text{intr}} & Y_{11,\text{intr}} \end{bmatrix}.$$

(10)

$$NF_{\min} = 1 + \frac{1}{kT_o} \left( \Re \left( C_{12A, \text{intr}} \right) + \sqrt{C_{11A, \text{intr}} C_{22A, \text{intr}} - \left( \Im \left( C_{12A, \text{intr}} \right) \right)^2} \right)$$

(13)

$$NF_{\min} = 1 + \frac{1}{kT_o} \left( \Re(C_{12A, \text{intr}}) + \sqrt{C_{11A, \text{intr}} C_{22A, \text{intr}} - (\Im(C_{12A, \text{intr}}))^2} \right)$$

$$Y_{\text{opt}} = \frac{\sqrt{C_{11A, \text{intr}} C_{22A, \text{intr}} - (\Im(C_{12A, \text{intr}}))^2} + j\Im(C_{12A, \text{intr}})}{C_{11A, \text{intr}}}$$

and

$$(14)$$

$$R_{\rm n} = \frac{C_{11A,\rm intr}}{2kT_o} \tag{15}$$

Fig. 5. (a) Measured (symbols) and simulated (lines) real parts of  $y_{11}$  and  $y_{22}$  versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and length  $L=0.18~\mu\mathrm{m}$ , biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ , (b) measured (symbols) and simulated (lines) imaginary parts of  $y_{11}$  and  $y_{22}$  versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and length  $L=0.18~\mu\mathrm{m}$  biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ , (c) measured (symbols) and simulated (lines) real parts of  $y_{12}$  and  $y_{21}$  versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and length  $L=0.18~\mu\mathrm{m}$  biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$  and (d) measured (symbols) and simulated (lines) real parts of  $y_{11}$  and  $y_{22}$  versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu\mathrm{m}$  (10 fingers of width  $6~\mu\mathrm{m}$ ) and length  $L=0.18~\mu\mathrm{m}$  biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ .

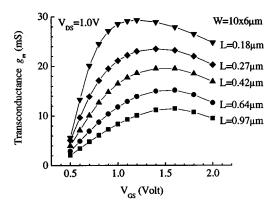

Fig. 6. Transconductance  $(g_m)$  versus  $V_{\rm GS}$  characteristics extracted from measured Re $(y_{21})$  for the n-type MOSFETs with channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width  $6~\mu{\rm m}$ ) and lengths  $L=0.97~\mu{\rm m}$ , 0.64  $\mu{\rm m}$ , 0.42  $\mu{\rm m}$ , 0.27  $\mu{\rm m}$  and 0.18  $\mu{\rm m}$ , respectively, biased at  $V_{\rm DS}=1.0~{\rm V}$ .

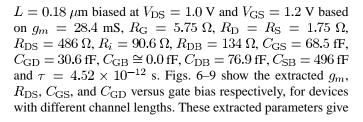

Fig. 7. Output resistance ( $R_{\rm DS}$ ) versus  $V_{\rm GS}$  characteristics extracted from measured Re( $y_{22}$ ) for the n-type MOSFETs with channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width 6  $\mu{\rm m}$ ) and lengths  $L=0.97~\mu{\rm m}$ , 0.64  $\mu{\rm m}$ , 0.42  $\mu{\rm m}$ , 0.27  $\mu{\rm m}$  and 0.18  $\mu{\rm m}$ , respectively, biased at  $V_{\rm DS}=1.0~{\rm V}$ .

similar fitting accuracies as that shown in Fig. 5(a)–(d) of the y-parameters versus frequencies at all the gate biases shown in Figs. 6–9.

The gate resistance  $(R_{\rm G})$  used in the simulation for different channel lengths is obtained by

$$R_{\rm G} = \frac{R_{\rm GSH} \cdot W}{3 \cdot n^2 \cdot L} \tag{20}$$

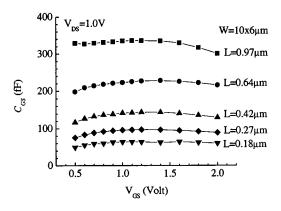

Fig. 8. Gate-to-source capacitances  $(C_{\rm GS})$  versus  $V_{\rm GS}$  characteristics extracted from measured Im $(y_{11})$  for the n-type MOSFETs with channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width  $6~\mu{\rm m}$ ) and lengths  $L=0.97~\mu{\rm m}$ , 0.64  $\mu{\rm m}$ , 0.42  $\mu{\rm m}$ , 0.27  $\mu{\rm m}$  and 0.18  $\mu{\rm m}$ , respectively, biased at  $V_{\rm DS}=1.0~{\rm V}$ .

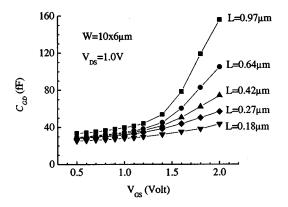

Fig. 9. Gate-to-drain capacitances ( $C_{\rm GD}$ ) versus  $V_{\rm GS}$  characteristics extracted from measured Im( $y_{12}$ ) for the n-type MOSFETs with channel  $W=10\times6~\mu{\rm m}$  (ten fingers of width 6  $\mu{\rm m}$ ) and lengths  $L=0.97~\mu{\rm m}$ , 0.64  $\mu{\rm m}$ , 0.42  $\mu{\rm m}$ , 0.27  $\mu{\rm m}$  and 0.18  $\mu{\rm m}$ , respectively, biased at  $V_{\rm DS}=1.0~{\rm V}$ .

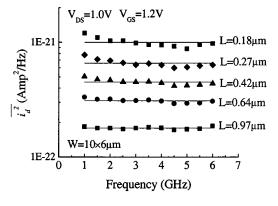

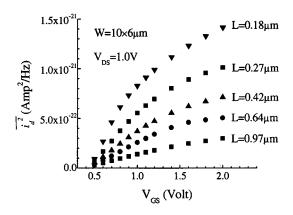

Fig. 10. Extracted channel noise  $(\overline{i_d^2})$  versus frequency characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and lengths  $L=0.97~\mu\mathrm{m}$ ,  $0.64~\mu\mathrm{m}$ ,  $0.42~\mu\mathrm{m}$ ,  $0.27~\mu\mathrm{m}$  and  $0.18~\mu\mathrm{m}$ , respectively, biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ . The solid lines are the extracted channel noise based on the method in [13].

where  $R_{\rm GSH}=5.17~\Omega$  and n is the number of fingers. In Fig. 6, the  $V_{\rm GS}$  bias at which the peak  $g_m$  occurs decreases as the channel length is reduced and this results in the shift of the peak  $f_{\rm T}$  shown in Fig. 4. Although the peak  $g_m$  increases when the channel length is reduced, the output resistance  $(R_{\rm DS})$  in Fig. 7 decreases at the same time and this results in the amplification

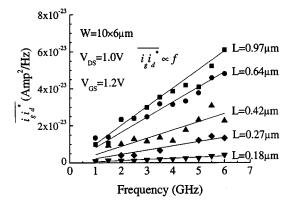

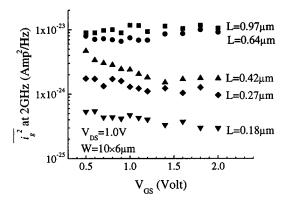

Fig. 11. Extracted induced gate noise  $(\overline{i_g^2})$  versus frequency characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width 6  $\mu{\rm m}$ ) and lengths  $L=0.97~\mu{\rm m},\,0.64~\mu{\rm m},\,0.42~\mu{\rm m},\,0.27~\mu{\rm m}$  and 0.18  $\mu{\rm m},\,$  respectively, biased at  $V_{\rm DS}=1.0~{\rm V}$  and  $V_{\rm GS}=1.2~{\rm V}.$

Fig. 12. Correlation between  $\overline{i_d^2}$  and  $\overline{i_d^2}$   $(\overline{i_g}i_d^*)$  versus frequency characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  ten fingers of width  $6~\mu\mathrm{m}$ ) and lengths  $L=0.97~\mu\mathrm{m}$ ,  $0.64~\mu\mathrm{m}$ ,  $0.42~\mu\mathrm{m}$ ,  $0.27~\mu\mathrm{m}$  and  $0.18~\mu\mathrm{m}$ , respectively, biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ .

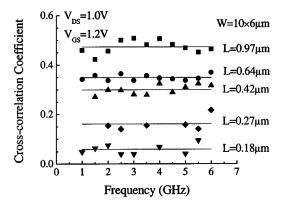

Fig. 13. Cross correlation coefficient c versus frequency characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width 6  $\mu\mathrm{m}$ ) and lengths  $L=0.97~\mu\mathrm{m}$ , 0.64  $\mu\mathrm{m}$ , 0.42  $\mu\mathrm{m}$ , 0.27  $\mu\mathrm{m}$  and 0.18  $\mu\mathrm{m}$ , respectively, biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ .

factor  $\mu_f$  ( $\mu_f = g_m \times R_{\rm DS}$ ) remains about the same at the  $V_{\rm GS}$  where the peak  $g_m$  occurs.

Based on the element values extracted from the y-parameters and the measured noise parameters, Fig. 10 shows the extracted channel noise versus frequency characteristics for n-type MOS-FETs with different channel lengths biased at  $V_{\rm DS}=1.0~{\rm V}$  and  $V_{\rm GS}=1.2~{\rm V}$ . It is shown that the channel noise, in general, is

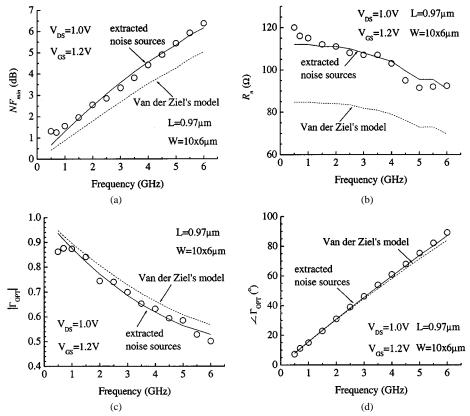

$Fig. \ 14. \quad (a) \ Measured \ (symbols) \ and \ simulated \ (lines) \ minimum \ noise \ figure \ (NF_{min}) \ versus \ frequency \ characteristics \ for \ the \ n-type \ MOSFET \ with \ the \ channel$ width  $W=10\times6~\mu\mathrm{m}$  (ten fingers of width 6  $\mu\mathrm{m}$ ) and length  $L=0.97~\mu\mathrm{m}$  biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ . The solid line is calculated with all the extracted noise sources and the dashed line is calculated using the Van der Ziel's model, (b) measured (symbols) and simulated (lines) equivalent noise resistance  $(R_{\rm n})$  versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width  $6~\mu{\rm m}$ ) and length  $L=0.97~\mu{\rm m}$ biased at  $V_{\rm DS}=1.0~{\rm V}$  and  $V_{\rm GS}=1.2~{\rm V}$ . The solid line is calculated with all the extracted noise sources and the dashed line is calculated using the Van der Ziel's model, (c) measured (symbols) and simulated (lines) magnitude of the optimized source reflection coefficient ( $|\Gamma_{\rm OPT}|$ ) versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and length  $L=0.97~\mu\mathrm{m}$  biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ . The solid line is calculated with all the extracted noise sources and the dashed line is calculated using the Van der Ziel's model and (d) measured (symbols) and simulated (lines) angle of the optimized source reflection coefficient ( $\angle\Gamma_{\mathrm{OPT}}$ ) versus frequency characteristics for the n-type MOSFET with the channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and length  $L=0.97~\mu\mathrm{m}$  biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$  and  $V_{\mathrm{GS}}=1.2~\mathrm{V}$ . The solid line is calculated with all the extracted noise sources and the dashed line is calculated using the Van der Ziel's model.

frequency independent and increases when the channel length decreases. The solid lines in Fig. 10 are the extracted channel noise based on the method in [13] which provides an alternative way to verify the channel noise extracted by the proposed method. The small increase in the channel noise at low frequencies for deep submicron devices might be caused by the inaccuracy of the measurement system at low frequencies.

Figs. 11 and 12 show that the induced gate noise and the correlation term are proportional to  $f^2$  and f, respectively where f is the operating frequency (solid lines in the figures). In addition, when channel length decreases, both the induced gate noise and the correlation term also decrease because of the decrease of  $C_{\rm GS}$ , as shown in Fig. 8. Another useful parameter that is used to describe the relationship between the channel noise, induced gate noise and their correlation is the cross correlation coefficient c which is defined as

$$c = \frac{\overline{i_g i_d^*}}{\sqrt{\overline{i_g^2} \, \overline{i_d^2}}}.\tag{21}$$

Fig. 13 shows the extracted cross correlation coefficient c versus frequency characteristics for the devices with different channel

lengths. In general, c is frequency independent and decreases when the channel length decreases. This is an opposite trend to the simulated results in [16], [17], but is in agreement with the theory in [2]. [3].

In order to verify the accuracy of the extracted noise sources and compare the simulation results against the measured data and those based on van der Ziel's model [14] which is suggested for long channel devices, Fig. 14(a)–(d) show the measured (symbol) and simulated (lines) noise parameters versus frequency characteristics by using the technique described in [5], [6] for the *n*-type MOSFET with the channel width W = $10 \times 6 \ \mu \text{m}$  and length  $L = 0.97 \ \mu \text{m}$  biased at  $V_{\rm DS} = 1.0 \ {\rm V}$ and  $V_{\rm GS}=1.2$  V. In these figures, the solid lines are the simulated results based on the extracted noise sources (solid lines in Figs. 10–12) and the dashed lines are the simulated results based on van der Ziel's model in which the spectral density of the noise sources are given by

$$\overline{i_d^2} = \gamma_{\text{satn}} 4kTq_{\text{do}} \tag{22}$$

$$\overline{i_d^2} = \gamma_{\text{satn}} 4kT g_{\text{do}} \tag{22}$$

$$\overline{i_g^2} = \delta_{\text{satn}} 4kT \frac{\omega^2 C_o^2}{g_{\text{do}}} \text{ and} \tag{23}$$

$$\overline{i_g} i_d^* = \varepsilon_{\text{satn}} 4kT j\omega C_o \tag{24}$$

$$\overline{i_q i_d^*} = \varepsilon_{\text{satn}} 4kT j \omega C_o \tag{24}$$

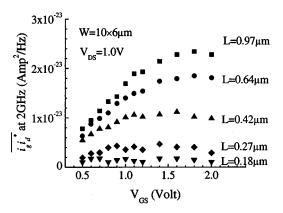

Fig. 15. Channel noise  $(\overline{i_d^2})$  versus bias characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width  $6~\mu\mathrm{m}$ ) and lengths  $L=0.97~\mu\mathrm{m}$ , 0.64  $\mu\mathrm{m}$ , 0.42  $\mu\mathrm{m}$ , 0.27  $\mu\mathrm{m}$  and 0.18  $\mu\mathrm{m}$ , respectively, biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$ .

Fig. 16. Induced gate noise  $(\overline{i_g^2})$  versus bias characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width 6  $\mu\mathrm{m}$ ) and lengths  $L=0.97~\mu\mathrm{m}$ , 0.64  $\mu\mathrm{m}$ , 0.42  $\mu\mathrm{m}$ , 0.27  $\mu\mathrm{m}$  and 0.18  $\mu\mathrm{m}$ , respectively, biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$ .

where  $g_{\rm do}=12.5\,{\rm mS},\,2/3,\,\delta_{\rm satn}=16/135,\,\varepsilon_{\rm satn}=1/9,\,C_o=C_o=3C_{\rm GS}/2$  and  $\omega=2\pi f.$  It is shown that the extracted noise sources, in general, give a good noise prediction. However, van der Ziel's model predicts lower  $NF_{\rm min}$  and  $R_{\rm n}$  and this might be caused by not including the channel noise and induced gate noise contributed from the velocity saturation region [3], [15] because of the assumption  $E_{\rm C}=\infty$  where  $E_{\rm C}$  is the critical field. This is currently being investigated.

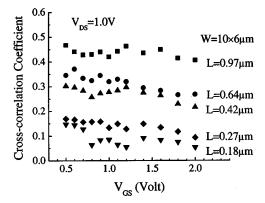

For the bias dependence of the extracted noise sources, Figs. 15–18 show the  $\overline{i_d^2}$ ,  $\overline{i_g^2}$ ,  $\overline{i_g i_d^*}$  and c versus bias characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  and lengths  $L=0.97~\mu\mathrm{m}$ , 0.64  $\mu\mathrm{m}$ , 0.42  $\mu\mathrm{m}$ , 0.27  $\mu\mathrm{m}$  and 0.18  $\mu\mathrm{m}$  respectively, biased at  $V_{\mathrm{DS}}=1.0~\mathrm{V}$ . It is shown that  $\overline{i_d^2}$  and  $\overline{i_g i_d^*}$  have a strong bias dependence and they increase the tend to saturate when  $V_{\mathrm{GS}}$  increases, but  $\overline{i_g^2}$  has a weak bias dependence. On the other hand, the cross-correlation coefficient c decreases when  $V_{\mathrm{GS}}$  increases and it follows the trend predicted in [2].

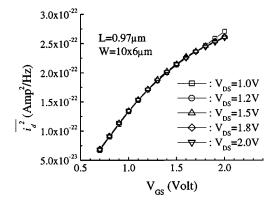

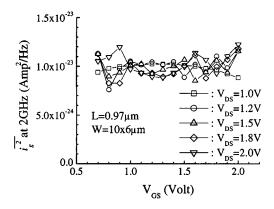

Finally, Figs. 19 and 20 show the extracted  $\overline{i_d^2}$  and  $\overline{i_g^2}$  versus  $V_{\rm GS}$  characteristics at  $V_{\rm DS}=1.0$  V, 1.2 V, 1.5 V, 1.8 V, and 2.0 V, respectively. It is shown that both of them have a weak  $V_{\rm DS}$  dependence in the  $V_{\rm DS}$  region discussed and this might be because the effect of the channel length modulation is not prominent in these devices, as shown in Fig. 3.

Fig. 17. Noise correlation between  $\overline{i_g^2}$  and  $\overline{i_d^2}$  ( $\overline{i_g}i_a^*$ ) versus bias characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width 6  $\mu{\rm m}$ ) and lengths  $L=0.97~\mu{\rm m},\,0.64~\mu{\rm m},\,0.42~\mu{\rm m},\,0.27~\mu{\rm m}$  and 0.18  $\mu{\rm m}$ , respectively, biased at  $V_{\rm DS}=1.0~{\rm V}.$

Fig. 18. Cross-correlation coefficient c versus bias characteristics for the n-type MOSFETs with channel width  $W=10\times 6~\mu\mathrm{m}$  (ten fingers of width 6  $\mu\mathrm{m}$ ) and lengths  $L=0.97~\mu\mathrm{m}$ , 0.64  $\mu\mathrm{m}$ , 0.42  $\mu\mathrm{m}$ , 0.27  $\mu\mathrm{m}$  and 0.18  $\mu\mathrm{m}$ , respectively, biased at  $V_\mathrm{DS}=1.0~\mathrm{V}$  and  $V_\mathrm{GS}=1.2~\mathrm{V}$ .

Fig. 19. Channel noise  $(\overline{i_d^2} \text{ versus } V_{\text{GS}} \text{ characteristics for the n-type MOSFET}$  with channel width  $W=10\times 6~\mu\text{m}$  (ten fingers of width  $6~\mu\text{m}$ ) and length  $L=0.97~\mu\text{m}$  biased at  $V_{\text{DS}}=1.0~\text{V}$ , 1.2 V, 1.5 V, 1.8 V, and 2.0 V, respectively.

# IV. CONCLUSIONS

A general direct extraction procedure of the induced gate noise, channel noise and their correlation in MOSFETs from the on-wafer scattering and noise measurements has been presented in detail and verified with measurements. In general, the channel noise  $\overline{i_d^2}$  is frequency independent and increases when the channel length decreases for all bias conditions at a fixed

Fig. 20. Induced gate noise  $(\overline{i_g^2})$  versus  $V_{\rm GS}$  characteristics for the n-type MOSFET with channel width  $W=10\times 6~\mu{\rm m}$  (ten fingers of width 6  $\mu{\rm m}$ ) and length  $L=0.97~\mu{\rm m}$  biased at  $V_{\rm DS}=1.0$  V, 1.2 V, 1.5 V, 1.8 V, and 2.0 V, respectively.

$V_{\mathrm{DS}}$ . However,  $\overline{i_g^2}$  and  $\overline{i_g i_d^*}$  are proportional to  $f^2$  and f, respectively, which agrees with the theoretical prediction and they both decrease when the channel length decreases because of the decrease of  $C_{\mathrm{GS}}$ . In the case of the cross correlation coefficient c, it is frequency independent and decreases when the channel length decreases. It was found that  $\overline{i_d^2}$  and  $\overline{i_g i_d^*}$  have a strong  $V_{\mathrm{GS}}$  bias dependence and they increase then tend to saturate when  $V_{\mathrm{GS}}$  increases, but  $\overline{i_g^2}$  has a weak  $V_{\mathrm{GS}}$  dependence. In addition, both  $\overline{i_d^2}$  and  $\overline{i_g^2}$  have weak  $V_{\mathrm{DS}}$  dependences for devices in which channel length modulation by the drain bias is weak. Also, van der Ziel's model predicts lower  $NF_{\mathrm{min}}$  and  $R_{\mathrm{n}}$  than the measurements. Finally, the extracted channel noise, induced gate noise and their correlation can be used as a direct target for the verification of the physics-based noise models of submicron MOSFETs.

# REFERENCES

- H. Samavati, H. R. Rategh, and T. H. Lee, "A 5-GHz CMOS wireless LAN receiver front end," *IEEE J. Solid-State Circuits*, vol. 35, pp. 765–772, May 2000.

- [2] A. van der Ziel, "Gate noise in field-effect transistors at moderately high frequencies," *Proc. IEEE*, vol. 51, pp. 461–467, 1963.

- [3] D. P. Triantis, A. N. Birbas, and S. E. Plevridis, "Induced gate noise in MOSFET's revised: The submicron case," *Solid-State Electron.*, vol. 41, no. 12, pp. 1937–1942, 1997.

- [4] H. Nah, M. S. Chae, H. S. Min, and Y. J. Park, "A general approach for calculation of thermal noise currents in semiconductor devices and its application to RF noise modeling of MOSFET's," in *Proc. 1999 Int. Semiconduct. Device Res. Symp.*, 1999, pp. 215–218.

[5] C. H. Chen and M. J. Deen, "High frequency noise of MOSFET's

- [5] C. H. Chen and M. J. Deen, "High frequency noise of MOSFET's I—modeling," *Solid-State Electron.*, vol. 42, pp. 2069–2081, November 1998.

- [6] —, "Direct calculation of the MOSFET high frequency noise parameters," J. Vac. Sci. Technol. A, vol. 16, no. 2, pp. 850–854, March/April 1998.

- [7] —, "A general noise and S-parameter de-embedding procedure for on-wafer high-frequency noise measurements of MOSFET's," *IEEE Trans. Microwave Theory Tech.*, vol. 49, pp. 1004–1005, May 2001.

- [8] —, "A general procedure for high-frequency noise parameter de-embedding of MOSFET's by taking the capacitive effects of metal interconnections into account," in *Proc. IEEE ICMTS 2001*, Kobe, Japan, March 19–22, 2001, pp. 109–114.

- [9] C. C. Enz and Y. Cheng, "MOS transistor modeling for RF IC design," IEEE Trans. Solid-State Circuits, vol. 35, pp. 186–201, February 2000.

- [10] R. A. Pucel et al., "A general noise de-embedding procedure for packaged two-port linear active devices," *IEEE Trans. Microwave Theory Tech.*, vol. 40, pp. 2013–2024, Nov. 1992.

- [11] R. Q. Twiss, "Nyquist's and Thevenin's theorems generalized for non-reciprocal linear networks," J. Appl. Phys., vol. 26, pp. 599–602, May 1955.

- [12] C. H. Chen, M. J. Deen, M. Matloubian, and Y. Cheng, "Extraction of the induced gate noise, channel thermal noise and their correlation in submicron MOSFET's from scattering and RF noise measurements," in *Proc. IEEE ICMTS 2001*, Kobe, Japan, March 19–22, pp. 131–135.

- [13] ——, "Extraction of the channel noise current in deep-submicron MOSFET's," in 30th ESSDERC'2000, Cork, Ireland, Sept. 11–13, pp. 508–511

- [14] A. van der Ziel, Noise in Solid State Devices and Circuits. New York: Wiley. 1986.

- [15] D. P. Triantis, A. N. Birbas, and D. Kondis, "Thermal noise modeling for short-channel MOSFET's," *IEEE Transn Electron Devices*, vol. 43, pp. 1950–1955, Nov. 1996.

- [16] S. Donati, M. A. Alam, K. S. Krisch, S. Martin, M. R. Pinto, and H. H. Vuong, "Physics-based RF noise modeling of submicron MOSFET's," in *IEDM Tech. Dig.*, 1998, pp. 81–84.

- [17] J.-S. Goo, C.-H. Choi, F. Danneville, E. Morifuji, H. S. Momose, Z. Yu, H. Iwai, T. H. Lee, and R. W. Dutton, "An accurate and efficient high frequency noise simulation technique for deep submicron MOSFET's," *IEEE Trans. Electron Devices*, vol. 47, pp. 2410–2419, Dec. 2000.

Chih-Hung Chen (S'95) was born in Tainan, Taiwan, R.O.C. in 1968. He received the B.S. degree in electrical engineering from National Central University, Chungli, Taiwan, in 1991 and the M.S. degree in engineering science from Simon Fraser University, Burnaby, BC, Canada, in 1997. He is currently pursuing the Ph.D. degree in the Department of Electrical and Computer Engineering, McMaster University, Hamilton, ON, Canada.

For three consecutive summers from 1998, he was with Conexant Systems, Inc., Newport Beach, CA,

where he was involved in the high-frequency noise characterization and modeling of MOSFETs and BJTs. His current research interests are in high-frequency noise characterization and modeling of MOSFETs and low noise and RF CMOS integrated circuit designs for wireless applications.

Mr. Chen was the recipient of a 2000–2001 Ontario Graduate Scholarship (OGS). He was also awarded a 2001–2002 Meena and Naresh Sinha Ontario Graduate Scholarship in Science and Technology (OGSST).

M. Jamal Deen (S'81–M'86–SM'92) was born in Georgetown, Guyana. He received the B.Sc. degree in physics and mathematics from the University of Guyana in 1978 and the M.S. and Ph.D. degrees in electrical engineering and applied physics from Case Western Reserve University (CWRU), Cleveland, OH, in 1982 and 1985, respectively.

From 1978 to 1980, he was an Instructor of physics at the University of Guyana and from 1980 to 1983, he was a Research Assistant at CWRU. He was a Research Engineer from 1983 to 1985 and an Assistant

Professor from 1985 to 1986 at Lehigh University, Bethlehem, PA. In 1986, he joined the School of Engineering Science, Simon Fraser University, Vancouver, BC, Canada, as an Assistant Professor and since 1993, he has been a Full Professor. In 1999, he became a Professor of electrical and computer engineering, McMaster University, Hamilton, ON.

Dr. Deen was awarded a Senior Canada Research Chair in 2001. He was a Visiting Scientist a the Herzberg Institute of Astrophysics, National Research Council, Ottawa, ON, in 1986, and spent his sabbatical leave as Visiting Scientist at Northern Telecom, Ottawa, in 1992–1993. He was also a Guest Professor in the Faculty of Electrical Engineering, Delft University of Technology, Delft, The Netherlands in summer 1997 and a CNRS scientist at the Physics of Semiconductor Devices Laboratory, Grenoble, France, in summer 1998. His current research interests include integrated devices and circuits, device physics, modeling and characterization, and low-power, low-noise, high-frequency circuits.

Dr. Deen is a member of Eta Kappa Nu, the American Physical Society, and the Electrochemical Society. He was a Fulbright–Laspau Scholar from 1980 to 1982, an American Vacuum Society Scholar from 1983 to 1984, and an NSERC Senior Industrial Fellow in 1993.

Yuhau Cheng (M'96–SM'99) received the B.S. degree in electrical engineering from Shandong Polytechnic University, Jinan, China, in 1982, the M.S. degree in electrical engineering from Tianjin University, Tianjin, China, in 1985 and the Ph.D. degree in electrical engineering from Tsinghna University, Beijing, China in 1989.

In 1990, he joined the Institute of Microelectronics (IME), Peking University, Beijing. From 1992 to 1996, he was an Associate Professor in the IME and the Department of Computer Science and

Technology. From 1994 to 1995, he was a Visiting Professor at the University of Trondheim, Norway, and a Research Fellow of the Norwegian Research Council. From 1995 to 1997, he was a Research Scientist in the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, where he was working on the BSIM3 model development and providing technical support to the BSIM3 users from both industry and academics. He was the Project Coordinator of the BSIM3v3 model development and was one of the prinicpal contributors of the BSIM3v3 model that has been chosen as an industry standard model for IC simulation by the Electronics Industry Association/Compact Model Council and given an R&D 100 Award in 1996. In 1997, he worked for Cadence Design Systems as a Member of the Consultant Staff. Since May of 1997, he has been with Conexant Systems (Formerly Rockwell Semiconductor Systems), Newport Beach, CA, where he is currently the Manager of the MS/RF device modeling team responsible for MS/HF (bipolar, CMOS, passive) device modeling and technical supports for various circuit designs. His research interests include high-speed bulk and silicon-on insulator (SOI) CMOS device, modeling, and MS/RF IC design. He has authored and co-authored over 60 research papers and the book MOSFET Modeling & BSIM3 User's Guide.

**Mishel Matloubian** (S'84–M'84) received the B.S., M.S., and Ph.D. degrees in electrical engineering from University of Southern California, Los Angeles, in 1979, 1980, and 1984, respectively.

He joined Texas Instruments, Dallas, working on CMOS/SOI technology development and characterization. He later worked at Samsung Semicondutor on BiCMOS, and at Hughes Aircraft on low-temperature rad-hard CMOS and BiCMOS technologies. He joined Rockwell Semiconductors, which later became Conexant Systems in 1994, and was manager of the Technology CAD Group responsible for Spice model generation and support. He is currently a Technical Director in Core Technology of Mindspeed Technologies, Newport Beach, CA, a Conexant company, with responsibilities for technology evaluation and device modeling.