## A COMPUTATIONAL APPROACH TO CUSTOM DATA REPRESENTATION FOR HARDWARE ACCELERATORS

## A COMPUTATIONAL APPROACH TO CUSTOM DATA REPRESENTATION FOR HARDWARE ACCELERATORS

BY ADAM B. KINSMAN, B.Eng., M.A.Sc. MAY 2010

A THESIS SUBMITTED TO THE SCHOOL OF GRADUATE STUDIES IN PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE DOCTOR OF PHILOSOPHY

McMaster University © Copyright 2010 by Adam B. Kinsman All Rights Reserved

## DOCTOR OF PHILOSOPHY (2010) (Electrical and Computer Engineering)

### MCMASTER UNIVERSITY Hamilton, Ontario, Canada

| TITLE:           | A Computational Approach to Custom Data Representation                                                                      |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|

|                  | for Hardware Accelerators                                                                                                   |

| AUTHOR:          | Adam B. Kinsman, B.Eng. Engineering Physics,<br>M.A.Sc. Electrical and Computer Engineering,<br>McMaster University, Canada |

| SUPERVISOR:      | Dr. Nicola Nicolici                                                                                                         |

| NUMBER OF PAGES: | xiv, 150                                                                                                                    |

## Abstract

This thesis details the application of computational methods to the problem of determining custom data representations when building hardware accelerators for numerical computations. A majority of scientific applications which require hardware acceleration are implemented in IEEE-754 double precision. However, in many cases the error tolerance requirements of the application are much less than the accuracy which IEEE-754 double precision provides. By leveraging custom data representations, a more resource efficient hardware implementation arises thereby enabling greater parallelism and thus higher performance of the accelerator.

The existing custom representation methods are unable to guarantee robust representations while at the same time adequately supporting ill-conditioned operators. Support for both of these scenarios is necessary for accelerating scientific calculations. To address this, we propose the use of a computational method based on Satisfiability-Modulo Theory (SMT). By capturing a calculation as a set of constraints, an SMT instance can be formulated which provides meaningful bounds even in the presence of ill-conditioned operators. At the same time, the analytical nature of SMT satisfies the need for robustness. Utilizing block vector arithmetic, our SMT approach is extended to provide scalability to large instances involving vector calculus which arise in scientific calculations. Atop this foundation, a unified error model is proposed which deals simultaneously with absolute and relative error, thereby providing the means of supporting both fixed-point and custom floating-point data types. Iterative algorithm analysis is leveraged to derive constraints for the SMT method. The application of the method to several scientific algorithms is discussed by way of case studies.

## Acknowledgements

As in any significant endeavour, to try to list all the people who in some way have impacted my life during the course of this undertaking would require far too many pages and surely still leave people out. At the same time, doubtless there are those whose effect in my life was un-mistakable, and they deserve special mention here.

I would like to express my thanks to the the administrative and technical staff of the ECE department at McMaster, who work hard to keep things running smoothly at a practical level, maintaining an environment which enables research to be done. I am appreciative also to the many faculty who influenced me during my time at McMaster in both personal and academic ways - in particular, Dr. Alex Jeremic and Dr. Shahin Sirouspour have given generously of themselves in serving on my supervisory committee, and have helped in identifying and defining the motivation for this work.

For sharing in both the joys and sorrows of this adventure, I am thankful to friends, both personal and professional. Special mention is surely deserved by former and current students in the Computer Aided Design and Test Research group of McMaster - Bai Hong Fang, Qiang Xu, David Lemstra, David Leung, Ehab Anis, Kaveh Elizeh, Mark Jobes, Roomi Sahi, Zahra Lak and Jason Thong - who have shared in countless hours of stimulating discussion, proofreading papers and coffee-break philosophizing. Among this group are also Henry Ko and Phil Kinsman, with whom the history goes back so far that I can say we've grown up together. I am also deeply indebted to my supervisor Dr. Nicola Nicolici for his unswerving commitment, inspiring vision and patient mentorship which have shaped me in a profound and lasting way. I cannot imagine this thesis being possible without his tireless efforts.

To my brothers Josh, Matt and Phil and my sisters-in-law Jenn, Beth, Alex and Amanda, I am thankful for constant emotional support and for many time-outs to relax and reconnect with the world. My father and mother in-law Bruce and Jane, and my dad and mom Bruce and Jan have also provided much support, and I am deeply grateful for their wisdom in helping me make tough decisions. To my wife Pamela for her patience, dedication, love and support I owe more than all the rest put together - I could not have done this without her. She has sustained me, and only through the joy that she and our children bring to my life, has my sanity been maintained.

Above all I praise God for placing in my life so many supportive people, for providing for me and for upholding me. Through Him, I have come to understand myself much better, for I am weak but He is strong.

# **List of Abbreviations**

| AA    | Affine Arithmetic,                       |

|-------|------------------------------------------|

| ASIC  | Application Specific Integrated Circuit, |

| CAD   | Computer-Aided Design,                   |

| CC    | Clock Cycle,                             |

| CG    | Conjugate Gradient,                      |

| CPU   | Central Processing Unit,                 |

| DFP   | Davidon-Fletcher-Powell,                 |

| DSP   | Digital Signal Processing,               |

| EDA   | Electronic Design Automation,            |

| ESD   | Energy Spectral Density,                 |

| FF    | Flip-flop,                               |

| FFT   | Fast Fourier Transform,                  |

| FLOPS | Floating-point Operations Per Second,    |

| FPGA  | Field Programmable Gate Array,           |

| GIA   | Generalized Interval Arithmetic,         |

| GPGPU | General-Purpose computation on GPUs,     |

| GPU   | Graphics Processing Unit,                |

| HDL   | Hardware Description Language,           |

| IA    | Interval Arithmetic,                     |

| ILP   | Integer-Linear Programming,              |

| IP    | Intellectual Property,                   |

| LTI   | Linear Time-Invariant,                   |

| LUT   | Look-Up Table,                           |

|       |                                          |

| NOC  | Network-On-Chip,                        |

|------|-----------------------------------------|

| NRE  | Non-Recurrent Engineering,              |

| OS   | Operating System,                       |

| PC   | Personal Computer,                      |

| RTL  | Register Transfer Level,                |

| SAT  | Boolean satisfiability problem,         |

| SMT  | Satisfiability-Modulo Theory,           |

| SVD  | Singular-Value Decomposition,           |

| VHDL | Very-high-speed-integrated-circuit HDL, |

| VLSI | Very Large Scale Integration,           |

|      |                                         |

# Contents

| A  | bstrac  | et      |                                           | iii |

|----|---------|---------|-------------------------------------------|-----|

| A  | cknow   | ledgem  | ients                                     | iv  |

| Li | st of A | Abbrevi | ations                                    | vii |

| 1  | Intr    | oductio | n                                         | 1   |

|    | 1.1     | Comp    | utation to solve problems                 | 1   |

|    |         | 1.1.1   | Computational effort and cost             | 2   |

|    | 1.2     | The ca  | ase for acceleration                      | 3   |

|    | 1.3     | The ne  | eed for custom representations            | 6   |

|    |         | 1.3.1   | Symbolic vs. numerical computing          | 6   |

|    |         | 1.3.2   | Representation of real numbers            | 7   |

|    |         | 1.3.3   | Standardization of floating-point support | 10  |

|    |         | 1.3.4   | Custom precision floating-point           | 11  |

|    | 1.4     | Cost re | eduction and performance gain             | 13  |

|    | 1.5     | Proble  | em statement                              | 16  |

|    |         | 1.5.1   | Robustness requirement                    | 16  |

|    |         | 1.5.2   | Ill-conditioned operator requirement      | 16  |

|    |         | 1.5.3   | Iterative method requirement              | 17  |

|    |         | 1.5.4   | Hardware efficiency requirement           | 17  |

|    |         | 1.5.5   | CAD methodology requirement               | 18  |

|    | 1.6     | Thesis  | organization                              | 18  |

| 2 | Bac  | kgroun    | d and prior work                        | 20 |

|---|------|-----------|-----------------------------------------|----|

|   | 2.1  | Accele    | eration through parallelism             | 20 |

|   |      | 2.1.1     | Parallelism via cluster computing       | 21 |

|   |      | 2.1.2     | Parallelism via multicore               | 23 |

|   |      | 2.1.3     | Parallelism via ASICs                   | 26 |

|   |      | 2.1.4     | Parallelism via FPGAs                   | 28 |

|   | 2.2  | CAD s     | support for FPGAs                       | 29 |

|   |      | 2.2.1     | Problem aspects                         | 30 |

|   |      | 2.2.2     | Existing approaches                     | 32 |

|   | 2.3  | Summ      | nary                                    | 42 |

| 3 | Sati | sfiabilit | y-Modulo Theories for the range problem | 43 |

|   | 3.1  | Motiva    | ation                                   | 43 |

|   | 3.2  | Funda     | mentals of SAT-Modulo Theories          | 44 |

|   |      | 3.2.1     | Boolean SAT refresher                   | 44 |

|   |      | 3.2.2     | Extending to other logics               | 46 |

|   |      | 3.2.3     | Solver operation                        | 46 |

|   | 3.3  | Range     | refinement using SMT                    | 53 |

|   |      | 3.3.1     | Dealing with division                   | 55 |

|   |      | 3.3.2     | Consideration of run-time               | 56 |

|   | 3.4  | Case s    | studies and results                     | 57 |

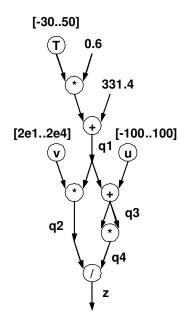

|   |      | 3.4.1     | Energy spectral density                 | 58 |

|   |      | 3.4.2     | Doppler effect                          | 59 |

|   |      | 3.4.3     | Analytic center                         | 61 |

|   |      | 3.4.4     | Euclidian projection                    | 62 |

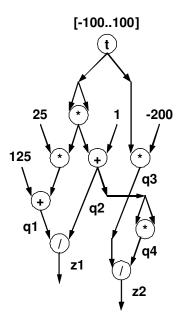

|   |      | 3.4.5     | A rational function                     | 64 |

|   |      | 3.4.6     | Newton's method                         | 66 |

|   |      | 3.4.7     | Key points of case studies              | 67 |

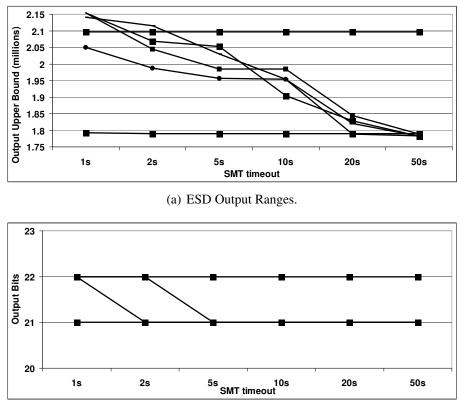

|   |      | 3.4.8     | Run-time/accuracy tradeoff              | 68 |

|   | 3.5  | Summ      | nary                                    | 68 |

| 4 | Scal | ability  | through block-vector formulations            | 70  |

|---|------|----------|----------------------------------------------|-----|

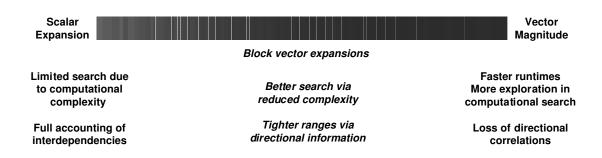

|   | 4.1  | Bit-wi   | dth allocation in vector calculus            | 70  |

|   |      | 4.1.1    | Uniform vector bit-width                     | 71  |

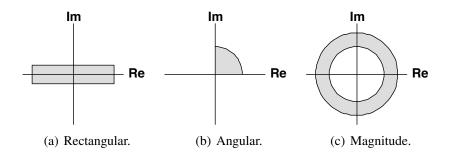

|   |      | 4.1.2    | Representation of complex numbers            | 71  |

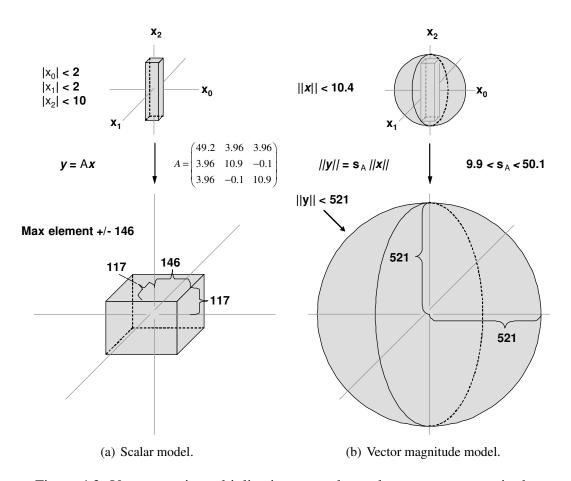

|   |      | 4.1.3    | Vector magnitudes                            | 73  |

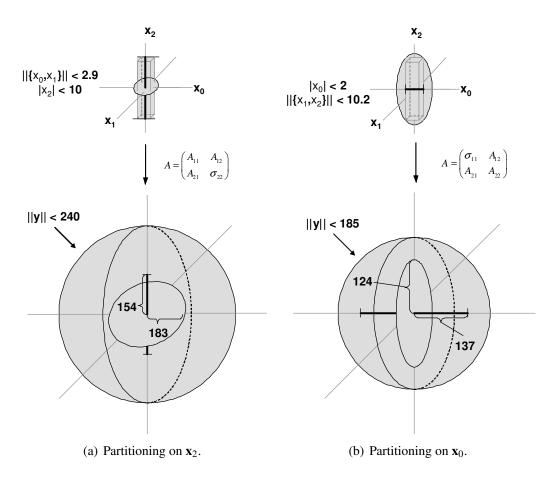

|   |      | 4.1.4    | Directionality via block vectors             | 75  |

|   |      | 4.1.5    | Partition selection                          | 79  |

|   | 4.2  | Case s   | studies                                      | 82  |

|   |      | 4.2.1    | Analytic center                              | 82  |

|   |      | 4.2.2    | Euclidian projection                         | 84  |

|   |      | 4.2.3    | Davidon-Fletcher-Powell formula              | 85  |

|   |      | 4.2.4    | Conjugate Gradient method                    | 88  |

|   |      | 4.2.5    | FFT based correlation                        | 90  |

|   | 4.3  | Summ     | nary                                         | 90  |

| 5 | Cus  | tom floa | ating-point for scientific calculations      | 93  |

|   | 5.1  | Metho    |                                              | 93  |

|   |      | 5.1.1    | Fixed/floating-point error model             | 94  |

|   |      | 5.1.2    | Forming precision constraints                | 96  |

|   |      | 5.1.3    | Iterative calculation partitioning           | 101 |

|   |      | 5.1.4    | Analysis for iterative calculations          | 103 |

|   |      | 5.1.5    | Direct calculation precision                 | 106 |

|   | 5.2  | Case s   | studies                                      | 107 |

|   |      | 5.2.1    | Two operand addition                         | 109 |

|   |      | 5.2.2    | Newton-Raphson division                      | 110 |

|   |      | 5.2.3    | Newton's method root finding                 | 113 |

|   | 5.3  | Conju    | gate Gradient case study                     | 115 |

|   |      | 5.3.1    | Summary of the application                   | 115 |

|   |      | 5.3.2    | Formal analysis and robust representations   | 117 |

|   |      | 5.3.3    | Perspective on formal and empirical findings | 124 |

|   | 5.4  | Summ     | ary                                          | 126 |

| 6  | Concluding remarks |         |                             |     |  |

|----|--------------------|---------|-----------------------------|-----|--|

|    | 6.1                | Future  | work                        | 128 |  |

|    |                    | 6.1.1   | SMT solver efficiency       | 128 |  |

|    |                    | 6.1.2   | Links to the application    | 129 |  |

|    |                    | 6.1.3   | Links to the implementation | 131 |  |

|    | 6.2                | Final r | emarks                      | 131 |  |

| Bi | bliogr             | aphy    |                             | 133 |  |

# **List of Tables**

| 1.1 | Comparing area/performance for floating vs. fixed-point [77]            |

|-----|-------------------------------------------------------------------------|

| 3.1 | Motivational example                                                    |

| 3.2 | Affine vs. SAT-Modulo for energy spectral density                       |

| 3.3 | Affine vs. SAT-Modulo for Doppler                                       |

| 3.4 | Affine vs. SAT-Modulo for analytic center                               |

| 3.5 | Affine vs. SAT-Modulo for Euclidian projection                          |

| 3.6 | Affine vs. SAT-Modulo for a rational function                           |

| 3.7 | Affine vs. SAT-Modulo for Newton's method                               |

| 4.1 | Magnitude bounding operations                                           |

| 4.2 | Affine vs. SAT-Modulo for vector and scalar analytic center 83          |

| 4.3 | Affine vs. SAT-Modulo for vector and scalar Euclidian projection 85     |

| 4.4 | Affine vs. SAT-Modulo for vector and scalar Davidon-Fletcher-Powell 87  |

| 4.5 | Affine vs. SAT-Modulo for vector and scalar Conjugate Gradient 89       |

| 4.6 | Affine vs. SAT-Modulo for vector and scalar FFT-based correlation 91    |

| 5.1 | Precision expression counterparts for common operators                  |

| 5.2 | Converting ranges to bit-widths for fixed and custom floating types 107 |

| 5.3 | Required bit-widths for Algorithm 5.1 as determined by [82]             |

| 5.4 | Bitwidths required for fixed-point intermediate variables               |

| 5.5 | Bitwidths required for floating-point intermediate variables            |

# **List of Figures**

| 1.1 | Computational thresholds for applications.                                | 4  |

|-----|---------------------------------------------------------------------------|----|

| 1.2 | Computational capacity/requirements and development time for state of the |    |

|     | art platforms/applications.                                               | 6  |

| 1.3 | Fixed and floating-point arithmetic operations                            | 12 |

| 1.4 | Contrasting standardized double vs. custom precision floating-point       | 15 |

| 2.1 | Parallelism via supercomputers and grid/cluster based computers           | 22 |

| 2.2 | Parallelism via multicore devices.                                        | 24 |

| 2.3 | Parallelism via customized ASICs                                          | 25 |

| 2.4 | Reduced design effort through better tool support                         | 29 |

| 2.5 | Summary of aspects which existing works address                           | 31 |

| 2.6 | Overview of approaches to bit-width allocation                            | 32 |

| 2.7 | Example of interval arithmetic (IA) operation.                            | 35 |

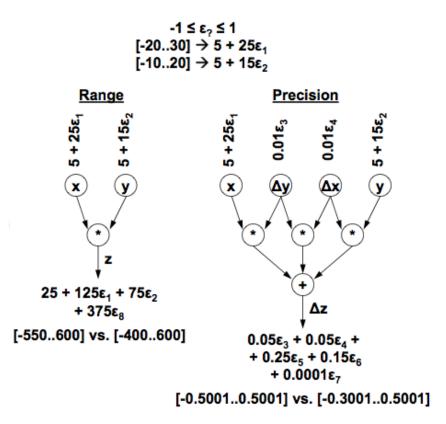

| 2.8 | Example of affine arithmetic (AA) operation.                              | 37 |

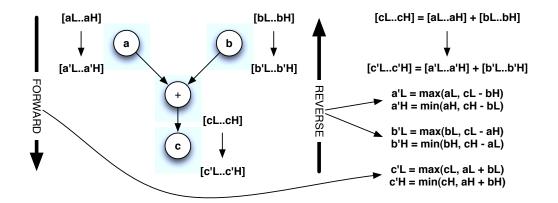

| 3.1 | Inferring intervals of variables for the addition operator                | 47 |

| 3.2 | Inferring intervals in a full dataflow.                                   | 48 |

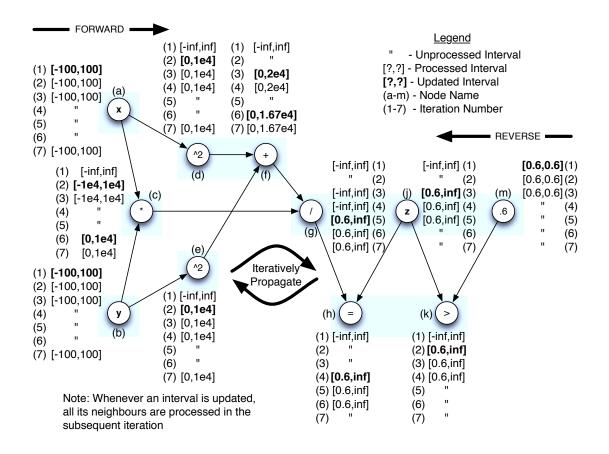

| 3.3 | SMT solver example.                                                       | 51 |

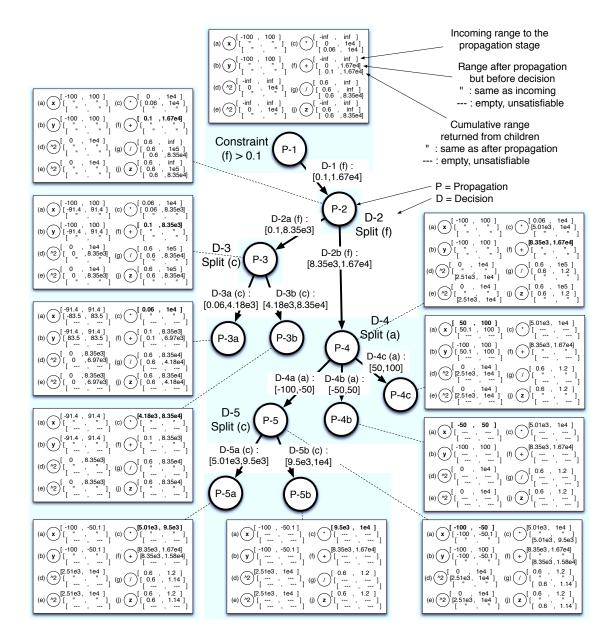

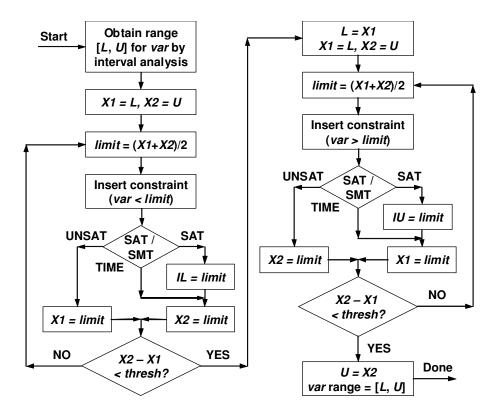

| 3.4 | SAT/SMT range refinement of <i>var</i>                                    | 54 |

| 3.5 | Data dependencies for Doppler effect case study.                          | 59 |

| 3.6 | Data dependencies for rational function case study.                       | 64 |

| 3.7 | Effect of timeout on range/bit-width                                      | 69 |

| 4.1 | Example bounding constraints put on complex numbers                       | 72 |

| 4.2 | Goal of block vector representations                                       | 75  |

|-----|----------------------------------------------------------------------------|-----|

| 4.3 | Vector matrix multiplication example: scalar vs. vector magnitude          | 77  |

| 4.4 | Effect of partitioning on range overestimation.                            | 79  |

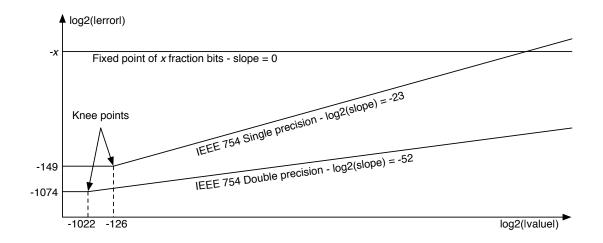

| 5.1 | Unified fixed/floating-point error model characterizing data type by knee  |     |

|     | and slope                                                                  | 95  |

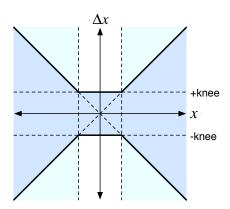

| 5.2 | Error region for a custom floating-point number                            | 99  |

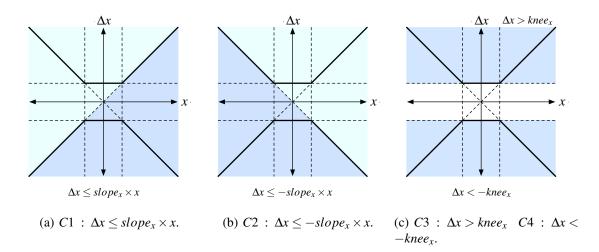

| 5.3 | Partial error regions and their associated constraints                     | 100 |

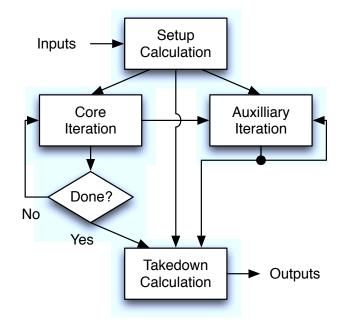

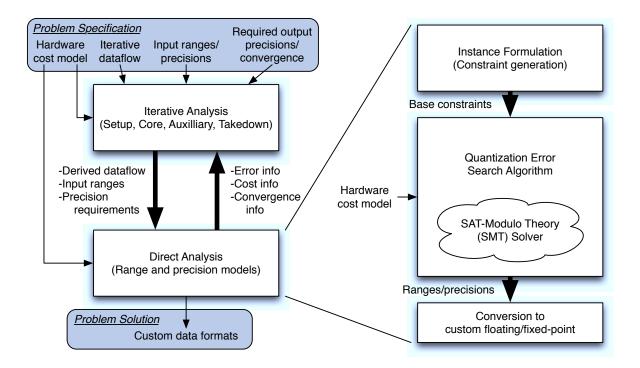

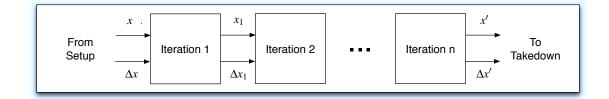

| 5.4 | A generalized view of the flow of data within an iterative calculation     | 102 |

| 5.5 | Conceptual flow for solving the bit-width allocation problem for iterative |     |

|     | numerical calculations.                                                    | 104 |

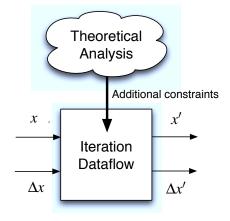

| 5.6 | Iterative analysis by iteration unrolling.                                 | 105 |

| 5.7 | Iterative analysis using information from theoretical analysis             | 105 |

## **Chapter 1**

## Introduction

Since the early days of the transistor roughly 60 years ago, exponential scaling has driven an increase in integration levels to enable modern circuits with billions of transistors in a single device, and operating frequencies in the low gigahertz (GHz) range [13]. To deal with the inherent complexity of designing such circuits, an entire ecosystem of computeraided design (CAD) tools and design intellectual property (IP) has evolved.

Over the same period, computers have been in a symbiotic relationship with applications growing similarly in complexity, enabling problems of growing difficulty and scale to be tackled by computers. In this chapter, discussion begins with a general description of how computers are employed for solving problems, eventually leading to the justification for this work in Section 1.5.

### **1.1** Computation to solve problems

One of the primary ways in which computers have improved our problem solving capacity is their ability to carry out with speed and precision tasks which human beings may find too repetitive, tedious, error prone or which involve overwhelming amounts of data. A straightforward example of this is the use of computers to sort, search and filter databases involving Terabytes (TB,  $= 10^{12}$  bytes) of information [17]. Going beyond mere record keeping, in general terms computers are used to solve problems by manipulating data according to a set of rules. In the physical sciences and engineering in particular, where analysis based

on mathematical theory has seen a great deal of success, computers have been extensively employed.

One explanation of the success of computers in science and engineering is the emphasis placed by those fields on creating models of the systems which they study. A reliable model of a system will enable one to reason about the system and make predictions about its behaviour. In this way, a model enables transference of some of the physical experimentation required to draw conclusions into the domain of abstract reasoning. The role of computers is to carry out in an automated way the reasoning related to the model, and once set up a computer can often be reused to perform many virtual experiments, providing more information at reduced cost compared to physical experimentation. Physical experimentation however will always be required to verify the conclusions drawn from the model and to inform/refine the model itself.

A poignant example of this virtualization of experimentation is the use of electronic analog computers for solving differential equations [72], a technique which was employed before programmable digital computers became ubiquitous. The equations which govern the behaviour of electronic circuit elements such as inductors, capacitors and resistors bear striking resemblance to equations which govern many physical phenomena e.g., massspring systems or fluid-flow systems. The similarity in the underlying mathematics enables a compact, inexpensive electronic system which models a bulky, costly physical system to replace it.

While virtual experiments can provide more information with less cost than physical ones, they do not come for free - there is a cost associated with creating a computer to reason about a given model, and the conclusions drawn are only as reliable as the models themselves. In general, more complex phenomena require more sophisticated models, which in general require more computational effort and/or setup cost. The next subsection examines these issues of computational effort and setup cost.

#### **1.1.1** Computational effort and cost

The inherent tradeoff between flexibility and cost exists in many avenues of life, and electronic systems are not excluded. When a dedicated electronic system is constructed to serve a solitary purpose, assumptions can be made about its task and environment leading to a simpler, more efficient implementation. Making a system more flexible often involves supporting scenarios which violate some assumptions, and as such any efficiency gains coming from those assumptions are lost. On the other hand what is gained from increased flexibility is reuse which impacts cost. While a dedicated system can be more efficient than a general purpose system at a particular task, usually it can do nothing but that task. A more flexible system will be less efficient for the same particular task but will be able to perform a number of tasks at similar efficiency.

In light of this tradeoff, the last few decades of evolution in electronics reveals a steady stream of applications implemented at first in dedicated electronic systems moving to ever more general and programmable platforms such as general purpose processors [64] - even as they are followed by applications of increasing complexity [31]. Seen from another point of view, applications emerge which seek electronic implementation, and the technology advancements arising during the course of that implementation have the two pronged effect of 1) enabling the same application to be solved on a more general platform and 2) extending the reach of dedicated systems to reach previously unsolvable problems. It is primarily through the first effect that cost is reduced, by moving to a general platform, the development and manufacturing costs of that platform are shared among all the applications which use that platform, and thus are lower than for a dedicated platform.

This pattern is exemplified particularly clearly in the transitioning of multimedia from analog to digital. Early electronic audio processing using dedicated analog systems gradually migrated to using dedicated digital signal processing circuitry, then to programmable digital systems as the capabilities of digital circuitry expanded thanks to Moore's law [90]. Today, audio processing in software is almost trivial even on commodity general purpose hardware. Similarly (but lagging by a number of years) was the transition for video, originally managed using analog circuitry, now processed on mainstream personal computers.

### **1.2** The case for acceleration

In addition to the migration from dedicated to general purpose platforms discussed in the previous section, what has also become clear over these few decades is the existence of

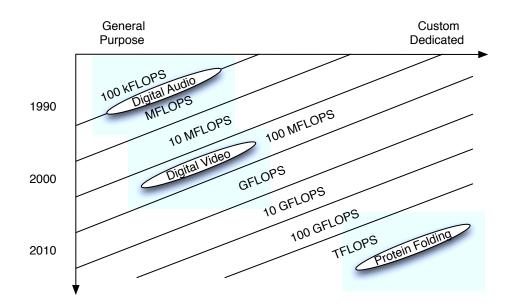

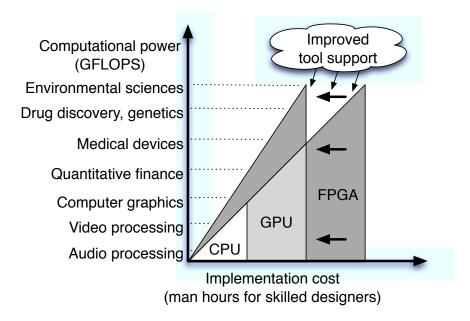

Figure 1.1: Computational thresholds for applications.

computational thresholds, i.e., barriers of complexity imposing limits on what problems are feasible with a certain capacity to carry out computations, commonly referred to as "compute power" (as distinct from power as it relates to energy consumption). These compute power thresholds are the reason for the lag in time between digitization of audio and of video, the computational threshold for video is higher than for audio. Figure 1.1 depicts in very general terms the evolution of compute power across the spectrum of platforms (from general purpose to dedicated), as well as computational requirements for some applications.

It is worth noting that the tasks in the upper-most computational capacity ranges (100 GFLOPS and TFLOPS), while being recognized today as important problems may not have even been conceived of in a similar graph from a decade ago. This carries the important point alluded to above that technology advancement with a specific application in mind has implications in other unanticipated applications. Furthermore, while Figure 1.1 focusses on the case where the higher efficiency of dedicated platforms is leveraged for the sole purpose of increased compute capacity, the efficiency may improve other aspects of performance.

Having established that more computational capacity can always be made use of, we must find ways of making this greater computational power available. Historically for general purpose computing, increased compute power came from two sources. On one hand, individual devices were capable of more operations per second through advancement in process technology (bringing higher clock rates), and architectural innovation (reducing execution overhead). On the other hand was parallelism, integrating many microprocessor devices into a much larger, more powerful supercomputer. While in the past the former has been the primary focus for increasing computational capacity, there has been a recent shift to relying on the latter to provide the compute power for the ever increasing complexity of applications [4].

The concept of parallelism for creating more powerful computers, and the means of implementing it will be discussed in more depth in Chapter 2, but are summarized here. Currently, there are three main directions: multi-core central processing units (CPUs), graphics processing units (GPUs) and field-programmable gate array (FPGA)-based hardware accelerators. In terms of integration levels, there are tens of processing engines in each multi-core CPU; hundreds of them in a GPU and thousands in each FPGA, as of today.

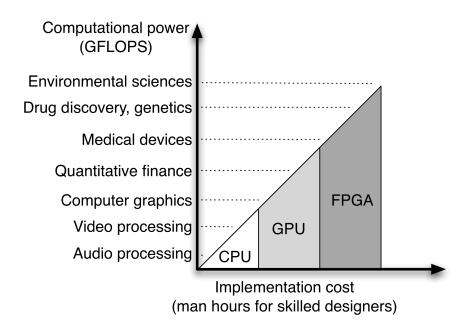

The differences between these three platforms lie in the amount of design effort required to map an application to each platform, and also the maximum achievable performance. Using the existing design methods and tools, implementing an application in FPGAs requires about three times more implementation effort than multi-core CPUs and about two times more effort than GPUs [92]. Figure 1.2 shows how FPGA-based acceleration can make a difference. Although in the audio/video processing fields, CPUs are sufficient today, there is a growing adoption of GPUs in the fields of computer graphics and quantitative finance, for example. There are however, fields such as biomedical sciences (medical equipment for remote surgery [81] or gene sequencing [50]) and environmental sciences (oil/gas exploration [34] or weather simulation [31]) where the added compute power brought by high-end FPGAs facilitates the much-needed acceleration.

In order to make this much-needed acceleration accessible, what is required is sophisticated computer-aided design (CAD) tool support. One problem which contributes to the higher design effort for FPGAs and as such needs to be addressed is the choice of a suitable numerical representation format as discussed in the next section.

Figure 1.2: Computational capacity/requirements and development time for state of the art platforms/applications.

### **1.3** The need for custom representations

While the previous sections have established the role of computers in problem solving and provided motivation for using accelerators to increase the problem solving capacity of computers, they have focussed primarily on the operational aspect of computer operation. This section examines another, equally important aspect of how the data on which the computer operates is represented.

#### **1.3.1** Symbolic vs. numerical computing

The representation of the data which computers are used to process generally exists under two main paradigms: symbolic and numerical computing. In symbolic computing, the data which is processed and rules by which it is processed are both abstract, and are derived from the theory governing the problem which the computer is working to solve. Numerical computing on the other hand, uses rules based on arithmetic to manipulate data which are quantities representing aspects of the problem under consideration.

To understand the difference between symbolic and numerical computing, consider a geometric series  $\sum_{j=0}^{j=n-1} ar^j$ . In symbolic computing the data would be the expression and its variables while the rules would be derived from algebra, application of which should lead eventually to the expression  $a\frac{1-r^n}{1-r}$ . In numerical computing however, the rules are derived from arithmetic, but the problem has no clear meaning without explicit numerical values for *a*, *r* and *n*. Once specified, application of the rules means performing the exponentiation, multiplication and summation over all *j* to produce the final result.

Due to key advantages (i.e., completeness, compactness, exactness) in some scenarios, symbolic computation packages have been developed such as computer algebra systems, e.g., Maple [85], Mathematica [128], and Maxima [97]. However, the majority of science/engineering problems today are solved using numerical techniques for two primary reasons. First, the precision of the input parameters to a problem as well as the required accuracy of the solution are typically limited. This is especially true in science and engineering which involve inexact measurements, and any uncertainty could frustrate the exactness, or complicate the analysis, of a symbolic solution. Second, although not the case in the geometric series example above, numerical representations may be more compact (efficient) for problems of current-day complexity, leading to reduced computation times especially in light of the tolerance created by inexactness.

#### **1.3.2** Representation of real numbers

Upon deciding to perform calculations numerically, the next decision is what format to use to describe numerical quantities. Since digital computers are discrete in nature, representation of discrete sets such as the integers is natural. The set of real numbers on the other hand is continuous and infinite, requiring approximation to be represented using the discrete, finite resources of the computer. A number of schemes have been devised to manage the error arising from this approximation as discussed next.

#### **Continued fractions**

One approach to approximating the real numbers within the finite, discrete scope of digital computers is the use of continued fractions [124]. A continued fraction representation for a number x is a sequence of integers  $a_i$  such that:

$$x = a_0 + \frac{1}{a_1 + \frac{1}{a_2 + \cdots}},$$

where the sequence  $a_i$  is finite for rational numbers and infinite for irrational numbers. While some of its mathematical properties (e.g. truncation yields best rational approximation) make it a favourable choice in theory, practical implementations encounter some difficulties. For one, human beings are not used to these representations so any user interaction with computers involves translation, at relatively high cost due to numerous divisions. Also, arithmetic operations on continued fractions are complex [124], and the varying representation length of different values can cause storage and manipulation complications.

#### **Rational representation**

Rational representations can be thought of as a simplified version of continued fraction, instead of a sequence with nested fractions, there is instead a pair of numbers (numerator and denominator) and a single fraction [87]. This solves some of the practical issues raised above, i.e., only a single division is required to convert to a human-readable format, and the size is more uniform over all representable numbers. However, manipulation can still cause problems in that straightforward operations could cause the numerator and denominator to grow without bound, but finding the best approximation with numerator and denominator within a certain range is by no means trivial (continued fractions provide such a means). At the same time this method has seen adoption, particularly in situations where the application can lend some insight to the ranges involved, and where values are primarily rational.

#### **Fixed-point**

Pushing the rational representation one step further, we can fix the denominator and consider only the numerator giving rise to a fixed-point representation [131]. In digital systems specifically, the choice of denominator is typically restricted to a power of 2, making conversion from one denominator to another (on a binary platform) the straightforward operation of shifting left or right. Consider the rational number 19/3, using denominator of  $8 = 2^3$ . This reduces to representing the integer nearest  $19/3 \times 2^3$ , which is  $51 = (1)2^5 + (1)2^4 + (0)2^3 + (0)2^2 + (1)2^1 + (1)2^0$  so the fixed-point representation would be 110011. Since the implicit denominator of  $2^3$  produces a shift so that  $19/3 \approx$  $(1)2^{2} + (1)2^{1} + (0)2^{0} + (0)2^{-1} + (1)2^{-2} + (1)2^{-3}$ , a "binary point" can be placed between the  $3^{rd}$  and  $4^{th}$  bits from the right with the number 110.011 resulting. This divides the representation into *I integer bits* on the left representing the part of the number (in absolute value)  $\geq 1$ , and F fraction bits on the right representing the part of the number (in absolute value) < 1. In essence, I limits the range of representable numbers and F limits the resolution. To extend the representation to negative numbers, 2's complement is used where -xis represented as  $2^{I} - x$ , and the range of representable numbers is  $-2^{I-1}$  to  $2^{I-1} - 2^{-F}$ . To summarize then, for a 16 bit fixed-point number with 5 integer bits and 11 fraction bits. the resolution is  $2^{-11} \approx 4.88 \times 10^{-4}$ , the range is -16 to 15.9995, and 19/3 would be represented 00110.01010101011, while -17/7 would be 11101.10010010010.

This format provides a bound on absolute error incurred at each operation, and as such is very attractive in terms of precision however, the dynamic range is severely limited. As a result, this method has received a great deal of attention in applications with well bounded numerical ranges (for example digital signal processing) and will be discussed in more depth in Chapter 2

#### **Floating-point**

While fixed-point representations are compelling in terms of precision, careful management of the implicit denominators is required to address the dynamic range limitations. Unfortunately, this can limit the flexibility and reuse of any platform which uses it. This accounts for its success in dedicated systems with well understood numerical patterns, and its shortcomings in more general purpose platforms. Expanding the dynamic range has involved the observation that bounding relative error rather than absolute error in calculations will often suffice, the reason for the emergence of scientific notation when doing calculations by hand. In this format a number x is commonly represented (or approximated) as *significant digits*×*base*<sup>exponent</sup>. The case of scientific notation uses 10 as the base, computers in general use base 2. The scaling by *base*<sup>exponent</sup> is analogous to moving the "point" of fixed-point giving rise to the name floating-point [41].

In the specific case of base 2, the significant digits (also called *significand* or *mantissa*) are scaled to between 1.0 inclusive and 2.0 exclusive, i.e. [1.0..2.0). For example, 19/3 as above can be represented as  $1.583... \times 2^2$ . If the exponent is represented on 4 bits we have 0010, and the mantissa on 11 bits we have (1.)1001010101011, where the (1.) is implicit (not stored). Extension to negative numbers is done through a sign bit indicating positive or negative, and for the case above of 1 sign, 4 exponent and 11 mantissa bits enables representation of numbers within the range  $\approx \pm [2.94 \times 10^{-39}, 6.80 \times 10^{38}]$  to within relative error of  $\approx 4.89 \times 10^{-4}$ .

The bounded relative error behaviour of floating-point numbers makes it particularly suitable for use as a representation format, especially for scientific applications. The convenience of relative error for measurement and control in the physical sciences and engineering also makes floating-point a natural choice. Moreover, the nature of many scientific applications provides contained output error for bounded input error. Finally, the dynamic range issue is addressed as resources for floating- vs. fixed-point to provide the same dynamic range are O(log(log(range))) vs. O(log(range)). These advantages have enabled floating-point arithmetic to be successfully deployed in computing machines.

#### **1.3.3** Standardization of floating-point support

As a result of the advantages of floating-point representation discussed above, it has been favoured for numerical computing applications, based primarily on software libraries (e.g., [36, 95]). In response, computer hardware makers (seeking competitive advantage) provided dedicated hardware supporting floating-point arithmetic to improve performance for numerical tasks. Independent hardware makers frequently adopted different choices for not

only size of exponent and mantissa fields, but even the base. In order to foster portability of software across hardware platforms, as well as consistency and reproducibility of results obtained from numerical programs, the need for a standard floating-point representation became clear [59].

The culmination of this need for a standard was the IEEE-754 [56] standard for floatingpoint representations, describing single precision (on 32 bits: 1 sign + 8 exponent + 23 mantissa) and double precision (on 64 bits: 1 sign + 11 exponent + 52 mantissa) formats. One important aspect arising from this standardization is the handling of corner cases, i.e. values or operations resulting in values outside or very nearly outside the set of numbers properly represented by the format. As [59] points out, this matter was largely ignored prior to standardization, with each hardware manufacturer making their own decisions. As also pointed out by [59], corner case control is imperative for maintaining portability of software and reliability of results obtained from software. For this reason, the standard provides options for a number of scenarios which are under programmer control (having defaults also assigned by the standard), so that a programmer with knowledge of the application may dictate the appropriate behaviour for a given corner case scenario.

#### **1.3.4** Custom precision floating-point

The previous section has shown that the capacity to manage a broad set of corner cases and the programmability to dictate behaviour are very important for general purpose hardware meant to execute a plethora of numerical programs requiring myriad features and behaviours. By contrast, an application-specific hardware solution needs only be concerned with the corner case behaviour relevant to the particular numerical task it implements. This important difference provides room for custom precision floating-point representations.

Most obviously, if an application of interest does not require the full dynamic range provided by IEEE-754, a custom representation may use smaller widths for the exponent and mantissa fields. More importantly however, support for the many modes dictated IEEE-754 take a significant toll when implemented in hardware, both in performance (maximum clock rate) and area, especially because of the programmability requirement. Simply freezing the corner case behaviour (removing the programmability requirement) would already

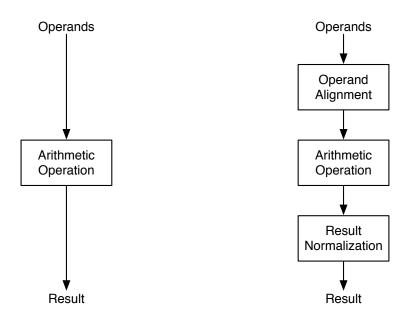

Figure 1.3: Fixed and floating-point arithmetic operations.

bring implementation cost reduction. Even more than this however is that for custom representations the boundaries marking regions of corner case behaviour are themselves flexible. For example, adding a single bit to the exponent field effectively squares the range of representable numbers to eliminate the need for any overflow handling whatsoever.

Leveraging this added degree of freedom, units tailored to the representation requirements of a given application can be designed to be smaller than fully standard compliant IEEE-754 arithmetic units. By tailoring representation requirements not only to the application as a whole, but even the specific stage of calculation, meaningful implementation cost and performance savings can be attained as discussed in the next section.

### **1.4** Cost reduction and performance gain

In order to understand how implementation cost and performance gain are affected by choice of representation, consider Figure 1.3 which shows in a very general sense arithmetic operations on fixed and floating-point operands. Since fixed-point numbers are essentially unencoded (they do not contain control information), arithmetic operations on them such as addition or multiplication are relatively direct (Figure 1.3(a)). For floating-point operations however, the exponents of the operands must be decoded, the two operands properly aligned, the operation performed, and the number re-encoded into a proper floating-point representation (Figure 1.3(b)).

The difference in terms of performance can be see more quantitatively in Table 1.1, based on data drawn from [77]. The table compares field-programmable gate-array (FPGA) implementations of multiplication and addition for 32-bit floating- and fixed-point operands (8 bits exponent and 23 bits mantissa for the floating-point). The comparison is made in terms of latency in clock cycles (CCs) and implementation cost in flip-flops (FFs) and lookup tables (LUTs) the basic implementation units which make up an FPGA. What differs between the two data types is that while fixed-point calculations use the data directly as operands, floating-point operations require the operands to be scaled before the operation can be performed, and the result must be normalized.

Observing the table, the impact of these differences can be seen. For multiplication, the variation between fixed- and floating-point is minimal. The mantissa of the result comes from the multiplication of the operand mantissas, and the exponent is essentially the sum of the operand exponents, with the smaller multiplication (23 vs 32 bits) balancing out the addition for the exponents. In light of Figure 1.3, the alignment and normalization units from 1.3(b) are relatively small compared to other operations, and are offset by how much smaller the operation unit is compared to 1.3(a) because of the 23 bit mantissa instead of the 32 bit fixed-point value.

For addition on the other hand, the differences are significant. In this case, the floatingpoint operation requires checking conditions on operand overlap, and a shift of anywhere between 0 and 22 positions may be required to align the operands. In contrast, for fixedpoint nothing more than a simple adder is required. In terms of latency, the case is similar.

|                | Area-LUTs     |               | Area-FFs       |               | Performance-CCs |              |

|----------------|---------------|---------------|----------------|---------------|-----------------|--------------|

| Operation      | Floating      | Fixed         | Floating       | Fixed         | Floating        | Fixed        |

| Multiplication | $\approx 750$ | $\approx 750$ | $\approx 1000$ | $\approx 750$ | $\approx 30$    | $\approx 30$ |

| Addition       | > 600         | < 40          | > 600          | < 40          | > 10            | = 1          |

Table 1.1: Comparing area/performance for floating vs. fixed-point [77].

For multiplication, the clock cycles required are essentially the same, while for addition more clock cycles are required for pipelining the large barrel shifters required to align the numbers before performing the addition. Referring again to Figure 1.3, in this case the alignment and normalization units are more costly to implement than for multiplication.

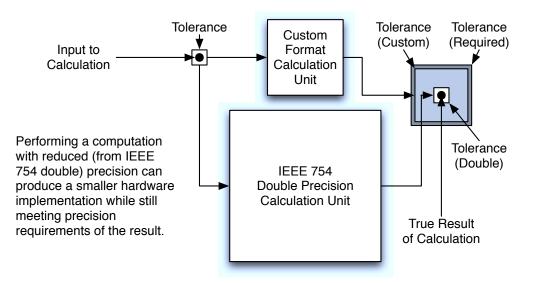

What is clear from this example is that representation can have a significant impact on area and performance of individual calculation units. This impact is amplified by as many calculation units as are employed together to achieve parallelism. In simple terms, if a calculation unit is smaller, more can be fit onto an acceleration platform (like an FPGA) thereby increasing the parallelism, and if it is faster the overall throughput is further increased. With this in mind, Figure 1.4 depicts in general terms the potential gains of moving away from the IEEE-754 double precision standard. By fully leveraging any slack in precision requirements, resource cost of arithmetic units can be reduced, leading in the end to greater parallelism and with it increased computational capacity.

What is also the case regarding representation impact on area and latency is that for a fixed choice of architecture and implementation technology, a direct relationship between representation and cost/latency can be identified. For example, the choice of a combinational multiplier vs. a sequential one for a given FPGA device family will yield a certain (complex) tradeoff between maximum clock frequency, number of clock cycles latency to the result and number of LUTs required. These choices are influenced by many factors which are independent from the representation choice, and can vary significantly from one application to another. Furthermore, they are usually settled (or very nearly) when custom

Figure 1.4: Contrasting standardized double vs. custom precision floating-point .

representations are derived. For this reason, cross platform and cross architecture applicability of a custom representation method must provide flexibility to deal with a wide array of design scenarios.

Support for these varying scenarios can be provided by making abstraction of the underlying implementation platform by use of models relating performance and cost to custom representation (bit-width). A simple example is a combinational multiplier with operands of size *n* bits exhibiting an approximate  $n^2$  area cost. Similarly, a ripple carry adder has a roughly linear relationship between operand size and delay. In a specific implementation technology, these numbers can be more precisely quantified. Aggregate cost models for full architectures can be formed by combining models for the functional units they contain, and greater accuracy of the model can be attained by adding more detail to the model.

Abstracting the implementation in this way brings flexibility to the custom representation approach, allowing the same methodology to be targeted toward different architectures and platforms. In this way, the improved performance which is the goal of custom representations transcends the implementation platform. Through this abstraction, custom representations are identified solely by architecture matched bit-widths, obtained with respect to architecture and platform specific cost models. That is, with a set of bit-widths relating to a defined architecture and platform, the hardware implementation follows directly. It is the burden of determining these parameters (bit-widths) that is focus of this thesis.

### **1.5 Problem statement**

In this chapter, we have established the motivation for accelerating scientific application and identified the key role to this played by custom data representations. In this section, the necessary features for deriving custom numerical representations for applications in the scientific computing domain are described and the organization of the remainder of the thesis is summarized.

#### **1.5.1** Robustness requirement

A fundamental requirement of any representation which is to be used for scientific computing is robustness - how far the correctness of the results can be trusted. Evidence for the need for this feature can be seen in the lengths which IEEE-754 goes to in providing support for indicating when a numerical problem arises (e.g. division by zero) and to correct for such problems if possible. While in some application domains even catastrophic numerical errors have little impact in terms of real repercussions, this cannot be taken for granted in scientific applications. For example, a multimedia decoding system having nonrobust numerical support may lead to a corrupted media stream which, although potentially diminishing overall user experience, is of far less consequence than a virtual surgery system where numerical mistakes may translate to loss of human life.

#### **1.5.2** Ill-conditioned operator requirement

The second feature which must be supported is the ability to deal with potentially illconditioned operators and/or singularities during numerical processing. As will be detailed in Chapter 2, many existing approaches to custom representation deal only with linear, time-invariant (LTI) systems having favourable numerical properties. When such methods are applied to scientific applications involving division (even potentially by zero) for example, the representations determined are likely to not bring any resource savings at all, if a representation can even be conclusively derived. Given that singularities arising from calculations such as division and trigonometric functions, ill-conditioned operators are a reality in many scientific computing, support for such situations must be present.

#### **1.5.3** Iterative method requirement

Many scientific applications - especially in the state of the art - rely on iterative procedures such as Newton's method [12] for root finding to reach a result. In particular, a large class of applications which solve discretized partial differential equations create large sparse linear systems, which are commonly solved iteratively using the Conjugate Gradient algorithm [113]. Examples of domains and applications include: in medicine for virtual surgery simulation with haptic feedback [81], in aerospace for non-destructive testing using computational fluid dynamics [46] and in nuclear physics for fusion reactors [22]. As Chapter 2 will discuss, many existing works like those mentioned above deal only with non-iterative applications. Because iterative procedures may involve a large and varied number of iterations, scalable support must be provided to draw conclusions about their numerical representation requirements.

#### **1.5.4 Hardware efficiency requirement**

Addressing the above requirements would not be of much use if the performance gains sought in developing custom representations are lost due to poor pairing with the implementation technology which is utilized. The impact on overall system performance that choice of custom representation will have is tightly coupled to architecture and implementation technology, and these factors will vary significantly between applications. Influencing factors can include types and constraints for memory and dedicated processing units (e.g. embedded multipliers in FPGAs), as well as choice of sequential or combinational implementation of calculation units. The result is that custom representations which are favourable to one architecture/implementation technology may be inefficient under another.

As such, an effective custom representation methodology should be sufficiently modular that it can make abstraction of these details. It should support external feedback on the performance vs. area cost vs. representation choice tradeoff and user definable objectives related to performance, area and error tolerance.

#### 1.5.5 CAD methodology requirement

Even while supporting all the above requirements, a methodology for determining custom data representations is of little use if it cannot be effectively accessed by designers as a part of a larger CAD tool flow. In light of this, some CAD methodology requirements arise. In order to facilitate seamless integration, designer intervention should be minimized. In the ideal case, the entire process which the designer would undertake manually to derive custom representations should be automated.

To accomplish this, plug-and-play interfaces for all interactions with the rest of the tool flow are necessary. Specifically, a front end which supports languages in wide use for scientific computing software (e.g., MATLAB, C) is needed. A back end which generates automatically hardware descriptions for the custom calculation units in a variety of hardware description language (HDL) formats (e.g., Verilog, VHDL) would also be needed to maintain implementation technology independence. Further required to abstract from implementation technology is an interface for integrating hardware cost models (as discussed in Section 1.5.4).

### **1.6** Thesis organization

The remainder of the thesis is organized as follows. Chapter 2 provides a survey of the existing methods for automated data representation in light of the requirements discussed above. Following this, Chapter 3 deals with Satisfiability-Modulo Theories (SMT), the underlying computational framework we use to address the data representation problem. The concepts needed to comprehend SMT solvers are introduced, and a range refinement

algorithm [65, 68] is proposed to address the range aspect of bit-width allocation. Improvements over existing techniques are demonstrated through application of the method to case studies characteristic to scientific computing.

With this computational technique in place, Chapter 4 builds upon it, adding support for dealing with large abstract data types (e.g., vectors and matrices) to provide scalability to large problems [66]. Vectors are initially represented in terms of their magnitude accompanied by a loss of directional correlation information. This loss of information is addressed through the use of block vectors which enable a smoother tradeoff between problem complexity and bounds quality. An algorithm is proposed for navigating this tradeoff, and the method is applied to the computational method of Chapter 3 as well as existing techniques and demonstrated on a set of case studies.

Built atop this scalable computational framework, Chapter 5 describes the full application of the method for determining custom representation for an iterative scientific application [67]. After dealing with formation of constraints for precision expressions (as opposed to just range in Chapters 3 and 4), an analysis methodology for iterative algorithms is presented. The proposed analysis techniques are applied to iterative case studies with scientific calculation characteristics. Finally, Chapter 6 provides concluding remarks and avenues of future work.

## Chapter 2

## **Background and prior work**

In this chapter, the various approaches to delivering acceleration as discussed in Section 1.2 will be discussed, leading eventually to the adoption of field-programmable gate array (FPGA) based accelerators. Building on this, existing CAD support for FPGAs is discussed with a particular focus on numerical representation and in light of the requirements set up in Section 1.5.

## 2.1 Acceleration through parallelism

As mentioned in Section 1.2, a direct means of extending the problem-solving reach of computers is to perform more computations at a time (instead of just reducing the time per computation) by coordinating a number of individual computers so they work together. In such a setup, connections between individual processors allow them to share data and results, and a small piece of the overall compute task is tackled by each processor which works in parallel with all other processors giving rise to the term *parallelism*. Overall performance depends in general upon the processing power of the individual processors vs. complexity of the individual subtasks, as well as the communication capacity of the interconnections vs. the amount of data which must be passed between processors [30].

As it turns out, aside from a relatively small class of problems known as "embarrassingly parallel", partitioning a large problem so as to attain the best performance on a given supercomputer is far from trivial [30]. This arises from data dependencies within applications, causing one step in the computation to block others. While much research has been done on automatic parallelization, results obtained manually which leverage an understanding of the data dependencies specific to an application are almost universally superior [3].

#### 2.1.1 Parallelism via cluster computing

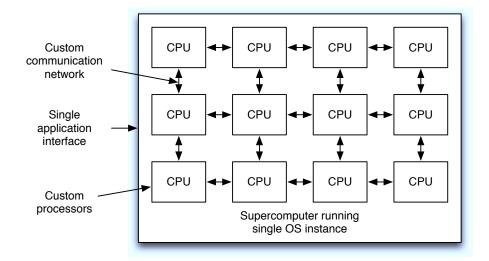

The obvious approach to parallelism of simply connecting numerous individual computer devices together is probably one of the earliest ways in which supercomputers were constructed. Beginning with early dedicated supercomputers, for example *IBM 7030 Stretch* [55] and *Cray-1* [70], management of resources was typically under a single application instance paradigm, using a centralized interface as depicted in Figure 2.1(a). With Moore's law [90] driving evolution in process technology, personal desktop machine compute power rose accordingly, typically providing equivalent computing power to decade earlier supercomputers. Adoption of each generation of personal desktop machine brings cost reduction through economies of scale, reducing desktop computer power to a commodity.

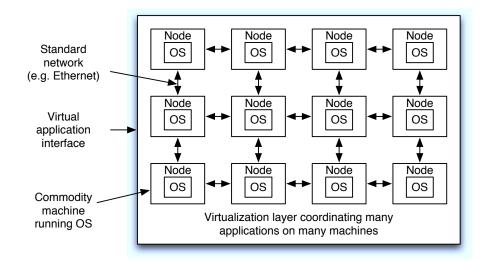

This commoditization of desktop computing power, along with advancement and standardization of computer network technology and protocols, has led to the more modern variant of distributed computing in grids (Beowulf cluster [40], IBM Roadrunner [6]). In such a setup, many individual standalone machines (called nodes), each running an operating system instance, are networked (usually densely) together, enabling all the machines to collaborate on one or many problems at once, a scenario shown in Figure 2.1(b). One advantage of this type of platform comes through abstraction of the node hardware. Since each node's OS instance can take care of local system tasks, a virtualization layer can be created for the application, which can handle issues such as heterogeneity of the nodes or fault tolerance/load balancing. Node hardware can range from server machines (IBM Roadrunner [6]) to low cost personal computer (PC) hardware running Linux (Beowulf cluster [40]) to even gaming consoles [76, 78] or personal computers of volunteers connected through the Internet such as in the SETI@Home [123] and Folding@Home [117] projects.

(a) Supercomputer (custom processors and network, single operating system instance and application interface).

(b) Cluster computer (virtualization software on commodity machines with separate operating system instances).

Figure 2.1: Parallelism via supercomputers and grid/cluster based computers.

Despite the benefits and past successes of cluster/grid computing, it does suffer some shortcomings. One drawback of escalating concern is cooling requirements and power consumption for large clusters made up of hundreds of thousands of nodes, which easily reach into the range of tens to hundreds of kilowatts. Size and setup cost for such a system are prohibitive for small organizations having only occasional needs for extensive compute power, and leasing time on supercomputers can also be expensive and unacceptably non-deterministic. Such organizations are also unlikely to benefit from volunteered compute power such as in SETI@Home or Folding@Home, both because of lack of participant goodwill and because of sensitivity of data.

Combined with the drawbacks above, the desire to bring greater amounts of compute power in-field (e.g., arctic seismic analysis [71]) leaves cluster/grid computing at a loss. Likewise, applications with form-factor (real-time, energy, weight, size) constraints such as deployed/embedded systems pose similar challenges with examples being real-time signal capture and processing for communications (e.g. mobile phones [127]) and diagnostics/visualization (e.g., medicine [121]). One answer to this problem follows the historically successful strategy of further integration as discussed next.

### 2.1.2 Parallelism via multicore

The cluster based approach to parallelism has played out relatively successfully over the last decade or so largely by riding Moore's law, whereby each new generation of commodity processor was able to operate at a faster clock speed, as well more memory could be integrated per device and network speeds were increasing. As such, clusters with more, faster nodes could be built, bringing higher computational throughput. Recently however, the escalating capabilities of single processors have begun to wane because of diminishing returns on three fronts: memory, instruction level parallelism and power [4]. In answer, microprocessor vendors have for the last 5 years (at least) pursued *multicore processors*.

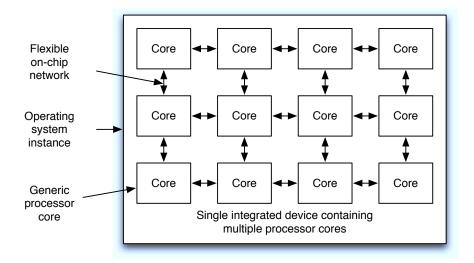

Figure 2.2 illustrates the multicore concept, note the resemblance to Figure 2.1(a) if the custom processors are replaced with general processor cores, the custom communication network is replaced by an on-chip communication network, and the entire system is integrated onto a single device as opposed to being built out of individual components. In

Figure 2.2: Parallelism via multicore devices.

addition, the role of the single (OS) instance of Figure 2.1(a) can in theory be filled by a traditional OS ported to run on such a multicore architecture. The network carries data and directives between the processors thereby enabling them to collaborate and choices range from dedicated custom bus architectures [69] to general network-on-a-chip (NOC) [39]. The processors themselves carry out tasks on the data, and can be special purpose or general, even on the same chip as for the Cell Broadband Engine [44].

What is attractive about this model of computation is the resemblance it bears to both the supercomputer model and at the same time traditional single processor machines, but with the advantages of power, latency and physical space savings brought by the integration. However, what does not carry over is the performance gains which traditionally came for free due to higher clock rates in each new processor generation. Challenges which face multicore integrated devices are presented in [4], with the central ones being related to power, memory and instruction level parallelism. In terms of power, the number of devices which can now be integrated into a single device coupled with the high switching

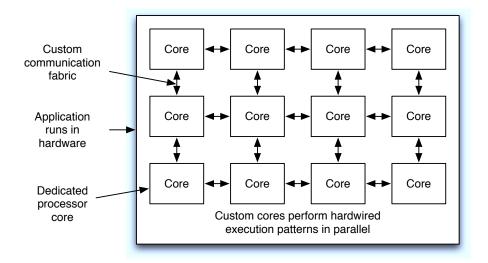

Figure 2.3: Parallelism via customized ASICs.

frequency results in difficulties both in getting sufficient power on to the chip, as well dissipating heat out of the chip. In terms of memory, with limited bandwidth for moving data on/off of chip keeping a growing number of increasingly more powerful processing units busy presents challenges [130]. Finally in terms of instruction level (fine-grained) parallelism, the majority has been exploited already through the evolution of microprocessor architectural innovations (e.g. branch prediction, out-of-order execution, speculation) [51]. New avenues of instruction level parallelism come with diminishing returns, and coarsegrained parallelism in applications must now be found and exploited. *This important shift in the source of performance gain has reopened interest in customization of the engines which are placed in parallel, a topic highlighted in the next section.*

### 2.1.3 Parallelism via ASICs

Alongside the evolution in general purpose processors based systems from custom platforms to grids to multicore, some isolated application domains have pursued greater computational power by custom-designing individual processor hardware. Such custom-designed hardware is implemented as application specific integrated circuits (ASICs). Taking this approach, the speedup comes from crafting the processor to be particularly efficient for the (usually narrow) set of execution patterns specific to that application domain.

This strategy has been particularly successful in the graphics processing application domain, largely as a result of two factors. First, the highly data-intensive nature of graphics processing relieves some of the hardware design complexity thus lending feasibility to the prospect of building dedicated accelerators. Second, the significant non-recurrent engineering (NRE) costs were financed relatively early on by consumers with high-end gaming interest who were willing to pay a premium for performance, catalyzing the cycle of increasing adoption and reducing cost. The culmination of this cycle over the last couple decades is the relegation of graphics processing units (GPUs) to the realm of commodity hardware.

A similar phenomenon has occurred in the digital signal processing (DSP) domain which, on the design side, shares the data-intensive nature of graphics processing. The economic motivation however came primarily from the embedded systems domain, specifically mobile multimedia where power efficiency was the important objective. Reducing computational effort wasted on execution overhead provides greater energy efficiency and thus longer battery life. Similarly to GPUs, consumer adoption led to large manufacturing volumes driving device cost down.

Aside from the decades old graphics and digital signal processing domains, this strategy is still in use today. A notable example is the development of a molecular dynamics supercomputer known as Anton [112]. This platform consists of dedicated chips specifically designed to be efficient for performing molecular dynamics calculations, joined by a custom connection infrastructure designed to be most efficient for the data traffic patterns exhibited in molecular dynamics calculations.

While the potential of application specific supercomputers stands well above anything

achievable with general purpose supercomputing platforms, the obvious drawback is the significant cost to develop such a machine. While custom processor design improves performance, it reduces flexibility which narrows the scope of applicability, and eliminates the opportunity to amortize the design cost over many applications. As technology advancements allow new generations of general purpose platforms to match older generation dedicated hardware, custom platforms representing significant investments can be obsoleted perhaps before even recovering their NRE costs.

It is on this point that the importance of the recent shift to performance through parallelism over performance through clock speed mentioned in the previous section hinges. In the past, the performance gains from adopting a new generation processor came so cheaply that the enormous (by contrast) development costs of dedicated hardware could not be justified despite substantially better performance. The increased design effort required for software on multicore vs. traditional CPUs has closed the development cost gap between general purpose software and dedicated hardware platforms, making custom hardware worth considering in light of the potential performance benefit.

On a related note, there has been recent interest in repurposing GPUs as a multicore platform, in order to leverage the maturity of the hardware, a movement known as "general purpose computing on GPUs" (GPGPU) [84]. The maturity of the technology has produced current day GPUs with hundreds of cores capable of performing IEEE-754 compliant floating-point operations at high rates (GHz) and, while lacking the sophisticated control features of modern day microprocessors, can often deliver higher performance by virtue of the parallelism. Recognizing that many scientific computations can be broken down into calculations which GPUs can handle very quickly, significant effort has been invested both to 1) directly map applications to GPUs ([18, 20, 79]) and 2) develop tools/compilers to assist/automate the mapping process ([29, 57]).

Despite this interest in reusing GPUs, the fact remains that GPUs are domain specific and while they perform excellently for calculations which can be made to resemble graphics processing, they cannot compete (performance wise) in domains where the calculations look very different. In such domains, application specific hardware will tend to provide better performance (in terms of both computational throughput and power efficiency, e.g. [45]), but with higher development cost which has been some of the motivation for using GPUs. The next section looks at a trend which significantly closes the development cost gap, significantly raising the viability of application specific hardware processors.

### 2.1.4 Parallelism via FPGAs

It has been shown in the previous sections that a paradigm shift has occurred where performance gains are now derived from increased parallelism rather than from increased clock speed. Furthermore we have seen that dedicated hardware systems deliver higher performance than reconfigurable software platforms but at increased cost. While the shift from clock speed to parallelism driven performance gains has closed the gap in development cost between multicore software and dedicated hardware. At the same time, in the last decade field-programmable gate-array (FPGA) technology advancements have significantly reduced the performance gap to ASICs. The reduction of this gap on both sides has created an opportunity for research into *reconfigurable computing platforms* [122] particularly those based on FPGAs.

The attraction of FPGA-based reconfigurable computing platforms is their ability to provide "not-much-less-than" ASIC performance for "not-much-more-than" multicore development effort. While FPGAs have higher logic delays and lower integration capacities than ASICs (accounting for the lower performance), the physical platform can be reconfigured and therefore used over many applications better amortizing the already lower NRE costs. At the same time, while architecture design requires more effort than software design as for GPUs and multicore, maturity of FPGA tool support makes the development cost gap smaller than for ASICs.

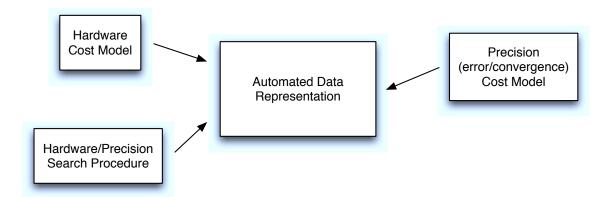

While the superior performance potential of FPGA-based platforms has been recognized, so too has the fact that development cost remains a roadblock to adoption [45]. To address this, much investigation has been done as of late into improving tool support to further reduce development effort. Figure 2.4 (an extension of Figure 1.2) illustrates the aim of such research, to bring the higher performance gains associated with FPGAs at the lower development cost associated with GPUs. It is this broad category to which this thesis belongs, providing automation support for reducing the design effort of mapping applications onto FPGAs, and the next section looks more in depth at existing tool support.

Figure 2.4: Reduced design effort through better tool support.

# 2.2 CAD support for FPGAs

The previous section has discussed the acceleration benefits of dedicated hardware which are made cost feasible through FPGA platforms. In order to leverage this acceleration while not suffering an inordinate increase in development cost (also discussed in the previous section), substantial research has been done in providing CAD support to lower development complexity for said platforms. In particular, a fair amount of effort has surrounded raising the abstraction of design entry, through so called behavioural synthesis [115]. Direct synthesis of hardware from a behavioural model in C or SystemVerilog relegates the difficult control intensive state machine design tasks to the CAD tool, thereby improving designer productivity. However, state of the art behavioural synthesis tools are still unable to produce designs as efficient as those created by a skilled designer implementing a design at the register transfer level (RTL) [9, 110].

Behavioural synthesis tools have found greatest acceptance in application domains and environments where design is feature driven rather than performance driven, such as multimedia. In feature driven design, competitive advantage comes from feature set and quick time to market, with efficiency being a secondary concern. On the other hand, in performance driven design, efficiency is the primary concern, for example in many embedded systems, which have form factor constraints. In this case, tool support still exists but the focus is different, with the tool being operated by a skilled designer working at the RTL.

As identified in Chapter 1, choice of numerical representation is a problem of significance for more efficiently using resources for better performance. Manual solution to this problem has been estimated to account for 25-50% of the design time in some scenarios [88]. Thus, to improve productivity tool support is necessary, forming the motivation for this thesis. In this section an overview of the problem is provided, as well as existing approaches which have been applied to address this problem.

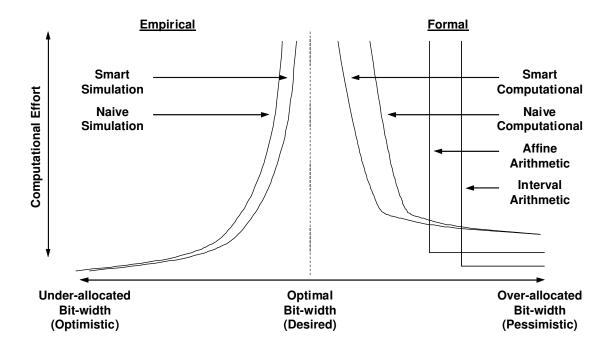

### 2.2.1 **Problem aspects**

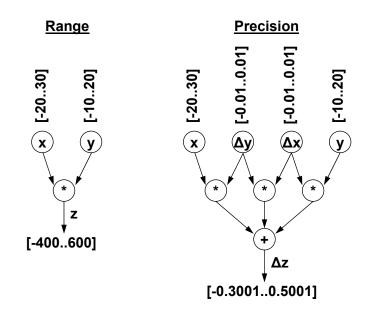

Before discussing specific approaches to solving the bit-width allocation problem, this section summarizes the aspects of the problem which various approaches seek to address. The first aspect involves the fact that discovering the minimum number of bits necessary to accurately represent an intermediate variable from a calculation is a two part problem. Both the range and precision required must be determined, from which can be inferred the required number of *exponent* and *mantissa* bits in floating-point, or *integer* and *fraction* bits in fixed-point.

The second aspect deals with cost models for both error and hardware. The goal of works in this category is to provide easily calculable yet reasonably accurate estimates of impact on numerical quality and resource requirements for a given choice of representation scheme. Put another way, such approaches provide the means to make a statement such as: for a choice of representations for the intermediate variables in a dataflow, here is the numerical deviation from infinite precision (true value) and the hardware resources required to implement the dataflow. The need for reasonable accuracy and easy calculation involves the third aspect described in the next paragraph.

Figure 2.5: Summary of aspects which existing works address.

The final aspect involves search procedures and metrics for navigating the solution space of possible representation choices across all intermediate variables. Using the models from the previous paragraph at the core of the search, these procedures will propose a representation scheme, evaluate the error/hardware cost (through the models) and update the representation scheme in order to improve a metric which reflects the overall goal of the search (i.e. error optimization, hardware optimization or a hybrid).

While the first aspect is independent of the latter two (meaning that models and searches can apply to range and/or precision), the latter two are related, but essentially orthogonal (meaning that an improved cost model brings benefit to essentially any search procedure). Many works contribute to one or multiple of these aspects, which are summarized in Figure 2.5. Apart from the aspects of the problem however, there are also requirements which solutions must satisfy to be useful in the context of scientific computing. Existing approaches to solving the problem in light of these requirements (identified in Section 1.5) are discussed next.