# FPGA Acceleration of Decision-Based Problems using Heterogeneous Computing

## FPGA ACCELERATION OF DECISION-BASED PROBLEMS USING HETEROGENEOUS COMPUTING

BY

JASON THONG, M.A.Sc.

A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

AND THE SCHOOL OF GRADUATE STUDIES

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

© Copyright by Jason Thong, 2014

All Rights Reserved

| Doctor of Philosophy (2014)         |

|-------------------------------------|

| (Electrical & Computer Engineering) |

| TITLE:      | FPGA Acceleration of Decision-Based Problems using |

|-------------|----------------------------------------------------|

|             | Heterogeneous Computing                            |

|             |                                                    |

| AUTHOR:     | Jason Thong                                        |

|             | M.A.Sc. (Computer Engineering),                    |

|             | McMaster University, Hamilton, Ontario, Canada     |

|             |                                                    |

| SUPERVISOR: | Dr. Nicola Nicolici                                |

|             |                                                    |

NUMBER OF PAGES: xxiv, 274

## Abstract

The Boolean satisfiability (SAT) problem is central to many applications involving the verification and optimization of digital systems. These combinatorial problems are typically solved by using a decision-based approach, however the lengthy compute time of SAT can make it prohibitively impractical for some applications.

We discuss how the underlying physical characteristics of various technologies affect the practicality of SAT solvers. Power dissipation and other physical limitations are increasingly restricting the improvement in performance of conventional software on CPUs. We use heterogeneous computing to maximize the strengths of different underlying technologies as well as different computing architectures.

In this thesis, we present a custom hardware architecture for accelerating the common computation within a SAT solver. Algorithms and data structures must be fundamentally redesigned in order to maximize the strengths of customized computing. Generalizable optimizations are proposed to maximize the throughput, minimize communication latencies, and aggressively compact the memory. We tightly integrate as well as jointly optimize the hardware accelerator and the software host.

Our fully implemented system is significantly faster than pure software on real-life SAT problems. Due to our insights and optimizations, we are able to benchmark SAT in uncharted territory.

## Acknowledgements

I am very grateful to those around me who have contributed to my development, both professionally and personally. I have been fortunate to experience and engage in many constructive environments where talent as well as perseverance are rewarded.

Firstly, I would like to acknowledge my academic colleagues. Many productive brainstorming sessions have and continue to happen in the Computer-Aided Design and Test group at McMaster. I wish to thank past and present members who have shaped my technical skills and provided valuable feedback. These include: Henry Ko, Adam Kinsman, Zahra Lak, Phil Kinsman, Amin Vali, Pouya Taatizadeh, Xiaobing Shi, and Peter Bergstra. I admire as well as thank my supervisor Nicola Nicolici for his no nonsense approach in challenging me to improve while sharing his sense of humor. I would also like to thank the examining committee for their efforts (Nicola Nicolici, Aleksandar Jeremic, Shahin Sirouspour, and Dejan Markovic).

I would like to acknowledge my colleagues from industry. I have had a wonderful experience working at Altera and Microsoft Research. This provided valuable insights on the development of CAD for FPGAs as well as FPGA applications, which has greatly furthered my own academic work. Special thanks goes to my supervisors John Freeman (Altera), Dmitry Denisenko (Altera), and Andrew Putnam (Microsoft) for giving me the opportunity to grow. I also wish to acknowledge Microsoft Research for the equipment loan (Stratix V FPGA), without which my results would not have been as elaborate.

Finally, I am sincerely grateful for my loving and supportive family. My parents (Bruce Thong and Liza Thong) and girlfriend (Lisha Wang) provide an atmosphere of stability, where triumph and failure can be genuinely shared. Your commitment inspires me to keep on learning and improving.

## Glossary

- **Abstraction** A less detailed perspective of a complex problem which is often an approximation.

- **ASIC** Application-specific integrated circuit.

- **Boolean** A data type that can only be true or false.

- **BCP** Boolean constraint propagation.

- **Cache** A faster but smaller memory, provides faster access to commonly used data than main memory.

- CAD Computer-aided design.

- Clause A constraint that must be satisfied in Boolean SAT.

- **DMA** Direct memory access, use of a dedicated memory controller to efficiently transfer large amounts of data.

- **DPLL** The Davis-Putnam-Logemann-Loveland algorithm for solving SAT.

- **DRAM** Dynamic random access memory.

- EDA Electronic design automation.

- Enhanced BCP The use of non-Boolean clauses for lossless compression.

- **Floorplan** An overview of the physical placement of major functional blocks on the integrated circuit.

**FPGA** Field-programmable gate array.

- Heterogeneous computing The use of more than one type of processor in a system.

- **Literal** Either the positive occurrence or the negative occurrence of a variable in Boolean SAT.

- **Logic resources** An abstraction of the amount of silicon required to implement a logic function.

- Logical constructs The building blocks to describe the behavior of a digital system.

- **Macro clauses** Multiply packed clauses, which facilitate better hardware memory utilization.

- **Multithreading** The use of multiple execution threads, which is one technique to facilitate concurrent computation.

- NOC Network-on-chip.

- **PCIe** Peripheral component interconnect express, a high-speed hardware/software communication protocol.

- **Pipelining** Insertion of registers to reduce the worst case propagation delay through combinational logic, thereby enabling a faster clock frequency.

- **Preprocessing** Transformations applied to a problem which are expected to make it easier to solve but without affecting its solution.

- **Random access** The ability to access data at any memory location in any order.

- **SAT** Abbreviation for the satisfiability problem.

**Search space** The set of all possible solutions that can be examined by an algorithm.

- **SMT** Satisfiability modulo theory, an extension or generalization of SAT.

- **SRAM** Static random access memory.

# Contents

| A            | bstra          | nct    |                                              | iii          |  |

|--------------|----------------|--------|----------------------------------------------|--------------|--|

| $\mathbf{A}$ | ckno           | wledge | ments                                        | $\mathbf{v}$ |  |

| G            | lossa          | ry     |                                              | vii          |  |

| 1            | 1 Introduction |        |                                              |              |  |

|              | 1.1            | An Int | roduction to SAT                             | 3            |  |

|              |                | 1.1.1  | An Intuitive Example of Boolean SAT          | 3            |  |

|              |                | 1.1.2  | Variations of Boolean SAT                    | 5            |  |

|              |                | 1.1.3  | Definitions and Terminology                  | 6            |  |

|              | 1.2            | Thesis | Organization                                 | 7            |  |

|              | 1.3            | The Se | cope of Our Contributions                    | 7            |  |

| <b>2</b>     | SAT            | Г Appl | ications and Algorithms                      | 9            |  |

|              | 2.1            | Applic | ations of SAT                                | 9            |  |

|              |                | 2.1.1  | NP-Completeness and a Historical Perspective | 9            |  |

|              |                | 2.1.2  | Survey of SAT Applications                   | 11           |  |

|              | 2.2            | Mappi  | ng Logical Constructs to SAT                 | 13           |  |

|   |     | 2.2.1   | Logical Construct Encoding                          | 13 |

|---|-----|---------|-----------------------------------------------------|----|

|   |     | 2.2.2   | A Demonstration of Equivalence Checking             | 15 |

|   |     | 2.2.3   | Using Integers in Boolean SAT                       | 17 |

|   | 2.3 | Local   | Search SAT Algorithms                               | 18 |

|   | 2.4 | Unsat   | isfiable-Based SAT Algorithms                       | 19 |

|   | 2.5 | The D   | PLL Algorithm and its Enhancements                  | 21 |

|   |     | 2.5.1   | The Basics of DPLL                                  | 21 |

|   |     | 2.5.2   | Key Enhancements to DPLL                            | 25 |

|   |     | 2.5.3   | Modern Enhancements to DPLL                         | 29 |

|   | 2.6 | Prepro  | ocessing                                            | 31 |

|   |     | 2.6.1   | Simplification                                      | 31 |

|   |     | 2.6.2   | Assisting the SAT Solver                            | 32 |

|   |     | 2.6.3   | Regulation of Clause Size and Variable Occurrence   | 33 |

|   | 2.7 | Our C   | Context of SAT Algorithms                           | 34 |

| 3 | Mo  | tivatio | ns and Prior Work in Relation to Current Technology | 35 |

|   | 3.1 | Motiv   | ation for Hardware-Accelerated SAT                  | 35 |

|   |     | 3.1.1   | Moore's Law and its Complications                   | 36 |

|   |     | 3.1.2   | The Suitability of FPGAs for SAT                    | 40 |

|   | 3.2 | Unsca   | lable Hardware SAT Designs                          | 42 |

|   |     | 3.2.1   | Instance-Specific Designs on FPGAs                  | 42 |

|   |     | 3.2.2   | Other Unscalable Designs                            | 43 |

|   | 3.3 | The I   | mportance of Hardware Memory Types                  | 44 |

|   |     | 3.3.1   | The Computation Pattern of BCP                      | 44 |

|   |     | 3.3.2   | Memory Speed Versus Capacity                        | 46 |

|   | 3.4 | Hetero | ogeneous Computing                                  | 49 |

|---|-----|--------|-----------------------------------------------------|----|

|   |     | 3.4.1  | Challenges of Hardware Support for Non-BCP Tasks    | 50 |

|   |     | 3.4.2  | Prior Works with Entire SAT Solvers in Hardware     | 51 |

|   |     | 3.4.3  | Motivation for Heterogeneous Computing              | 52 |

|   | 3.5 | Multit | threaded SAT                                        | 53 |

|   |     | 3.5.1  | Multithreaded Software SAT                          | 53 |

|   |     | 3.5.2  | Multithreaded Hardware SAT                          | 55 |

|   |     | 3.5.3  | Most Relevant Prior Work                            | 57 |

|   | 3.6 | Summ   | nary of Our Design Decisions                        | 60 |

| 4 | Har | dware  | Memory Layout and BCP Engine                        | 61 |

|   | 4.1 | Variał | ble Occurrence Lists                                | 61 |

|   | 4.2 | Key In | nsights for Compacting SAT                          | 64 |

|   |     | 4.2.1  | Implicit Representations                            | 64 |

|   |     | 4.2.2  | Fast BCP                                            | 67 |

|   |     | 4.2.3  | Lossless Compression and Partitioning               | 70 |

|   | 4.3 | Hardw  | vare BCP Memory Layout                              | 73 |

|   |     | 4.3.1  | Specification to Visit One Clause                   | 73 |

|   |     | 4.3.2  | Variable Assignments and Constraint Propagation     | 77 |

|   |     | 4.3.3  | Incremental Update to Assignment                    | 79 |

|   | 4.4 | Concu  | urrency Analysis                                    | 81 |

|   |     | 4.4.1  | Synchronization of Distributed Variable Assignments | 81 |

|   |     | 4.4.2  | Distribution of Work Between Processors             | 85 |

|   | 4.5 | Clause | e Traversal State Machine                           | 87 |

|   | 4.6 | Summ   | nary of Hardware BCP                                | 90 |

| <b>5</b> | Har  | dware   | Communication and Integration                        | 91  |

|----------|------|---------|------------------------------------------------------|-----|

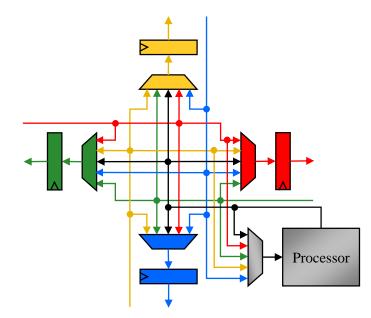

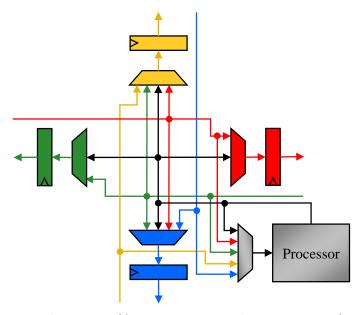

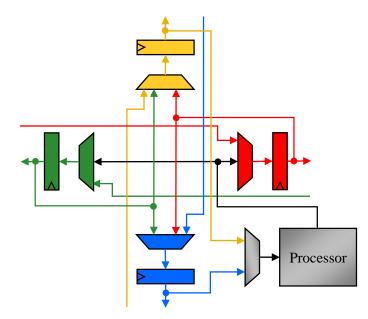

|          | 5.1  | System  | n Overview                                           | 91  |

|          | 5.2  | Classif | fication of On-Chip Communication                    | 94  |

|          | 5.3  | Netwo   | rk Design Guidelines                                 | 96  |

|          | 5.4  | Separa  | ation of Traffic Classes                             | 96  |

|          | 5.5  | Distrib | outed Shift Register Networks                        | 99  |

|          |      | 5.5.1   | The Offload Network Structure                        | 99  |

|          |      | 5.5.2   | The Reload Network Structure                         | 103 |

|          |      | 5.5.3   | Reusing the Offload Network for BCP Collection       | 104 |

|          |      | 5.5.4   | Reusing the Reload Network for Memory Initialization | 106 |

|          | 5.6  | Synchi  | ronization Networks                                  | 107 |

|          |      | 5.6.1   | Detecting the Completion of BCP                      | 107 |

|          |      | 5.6.2   | Ensuring Software Receives Every BCP                 | 111 |

|          |      | 5.6.3   | Conflict Detection and Reporting                     | 112 |

|          | 5.7  | Rando   | m Access Network                                     | 113 |

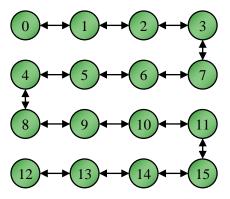

|          |      | 5.7.1   | 2-Dimensional Grid Network Topology                  | 114 |

|          |      | 5.7.2   | Network Design Guidelines and Simplifications        | 118 |

|          | 5.8  | Summ    | ary of the On-Chip Networks                          | 121 |

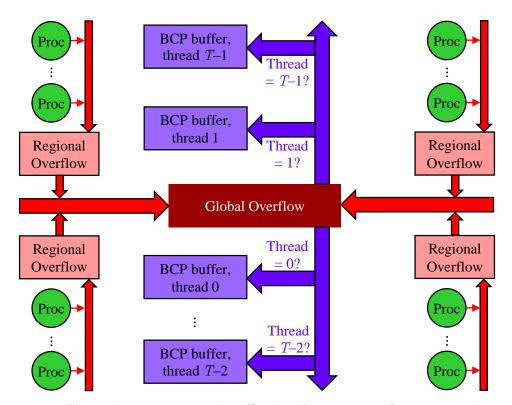

|          | 5.9  | BCP (   | Central Buffers                                      | 123 |

|          | 5.10 | Proces  | sor Interface                                        | 127 |

|          | 5.11 | High-I  | Level Floorplanning                                  | 129 |

|          | 5.12 | Summ    | ary of Hardware Communication                        | 133 |

| 6        | Adv  | anced   | Hardware Optimizations                               | 135 |

|          | 6.1  |         | ced BCP                                              | 135 |

|          |      |         |                                                      |     |

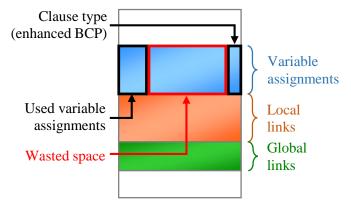

|   | 6.2  | Ultra   | Compact Variable Assignments                           | 1 |

|---|------|---------|--------------------------------------------------------|---|

|   |      | 6.2.1   | Identification of Unused Memory 14                     | 1 |

|   |      | 6.2.2   | Double Packed Clauses                                  | 2 |

|   |      | 6.2.3   | Creating Space for Extra Clause Information            | 4 |

|   |      | 6.2.4   | Variable Assignment Compression                        | 7 |

|   |      | 6.2.5   | Elimination of Most Small Clauses                      | 9 |

|   |      | 6.2.6   | Macro Clauses                                          | 9 |

|   | 6.3  | Distril | buted Encoding of Local Length                         | 3 |

|   | 6.4  | Summ    | ary of Hardware Optimizations                          | 8 |

| 7 | Soft | tware S | SAT Solver Integration 159                             | 9 |

|   | 7.1  | Syster  | n Flow                                                 | 9 |

|   | 7.2  | Hardw   | vare/Software PCI Express Interface                    | 2 |

|   |      | 7.2.1   | Hardware/Software Interactions                         | 2 |

|   |      | 7.2.2   | Software Interfacing                                   | 5 |

|   |      | 7.2.3   | Same Thread Hardware/Software Concurrency              | 6 |

|   | 7.3  | Confli  | ct Analysis for Enhanced BCP                           | 7 |

|   |      | 7.3.1   | A Review of Boolean Conflict Analysis                  | 7 |

|   |      | 7.3.2   | Integration of Hardware BCP into Conflict Analysis 176 | 0 |

|   |      | 7.3.3   | Enhanced BCP Conflict Analysis                         | 0 |

|   | 7.4  | The H   | lardware BCP Reordering Problem                        | 3 |

|   |      | 7.4.1   | Motivation for Timestamp-Based Conflict Analysis 178   | 5 |

|   |      | 7.4.2   | Adding Timestamps to Hardware BCP                      | 6 |

|   |      | 7.4.3   | Dynamic Ordering During Conflict Analysis              | 9 |

|   | 7.5  | Manag   | gement of Learnt Clauses                               | 0 |

|   |     | 7.5.1   | Adding Learnt Clauses into Hardware Memory       | 181 |

|---|-----|---------|--------------------------------------------------|-----|

|   |     | 7.5.2   | Maintaining Learnt Clauses for Conflict Analysis | 184 |

|   | 7.6 | Softwa  | are Memory Minimization                          | 186 |

|   |     | 7.6.1   | Bit Manipulations                                | 186 |

|   |     | 7.6.2   | Variable Activity Heap Restructuring             | 187 |

|   | 7.7 | Summ    | ary of Software Integration                      | 190 |

| 8 | SAT | Γ Parti | itioning and Preprocessing in Software           | 191 |

|   | 8.1 | Clause  | e Partitioning Algorithm                         | 191 |

|   |     | 8.1.1   | Motivating the Use of a Bottom-Up Heuristic      | 192 |

|   |     | 8.1.2   | Description of Our Bottom-Up Heuristic           | 193 |

|   |     | 8.1.3   | Speeding Up the Heuristic                        | 197 |

|   |     | 8.1.4   | Clause Packing                                   | 199 |

|   |     | 8.1.5   | Partition Size Regulation                        | 201 |

|   | 8.2 | Prepro  | ocessing for SAT Problem Compaction              | 202 |

|   |     | 8.2.1   | Description of Our Five Preprocessor Stages      | 202 |

|   |     | 8.2.2   | Customizing the Preprocessor Flow                | 208 |

|   | 8.3 | Summ    | ary of Software Compaction                       | 210 |

| 9 | Exp | oerime  | ntal Results                                     | 211 |

|   | 9.1 | Testin  | g Methodology                                    | 212 |

|   | 9.2 | Syster  | n Specification                                  | 214 |

|   |     | 9.2.1   | FPGA Resource Utilization                        | 214 |

|   | 9.3 | Perfor  | mance Metric                                     | 217 |

|   | 9.4 | Comp    | arison with Prior Hardware SAT Work              | 217 |

| 9.5    | 6 Rando  | omized Boolean 3-SAT Benchmark                | 220         |

|--------|----------|-----------------------------------------------|-------------|

|        | 9.5.1    | Limitations of Accelerating Easy SAT Problems | 220         |

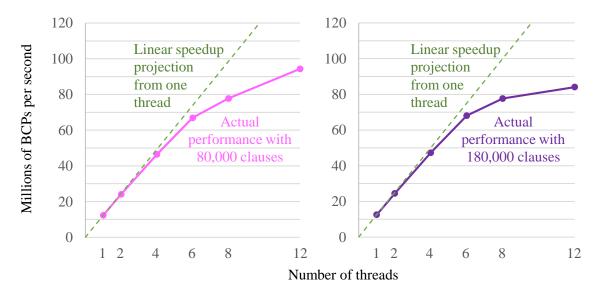

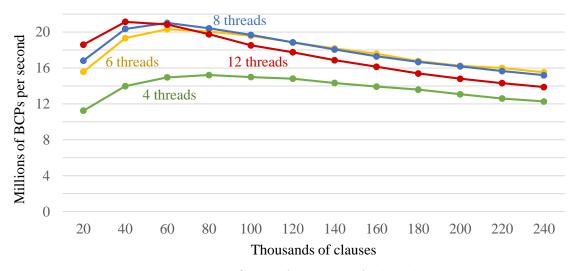

|        | 9.5.2    | Performance Analysis of Our System            | 222         |

|        | 9.5.3    | Comparison Against Multithreaded Software     | 230         |

| 9.6    | 6 Rando  | omized Enhanced BCP Benchmark                 | 234         |

|        | 9.6.1    | Benchmark Description                         | 234         |

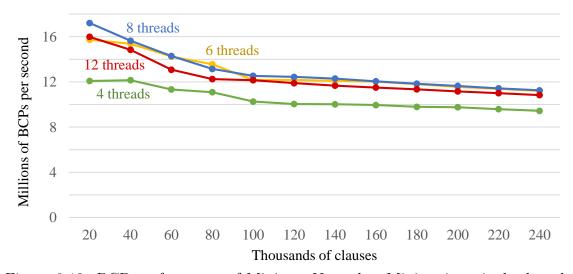

|        | 9.6.2    | Performance Analysis of Enhanced BCP          | 238         |

|        | 9.6.3    | Comparison With Multithreaded Software        | 243         |

| 9.7    | SAT C    | Competition 2013 Applications Benchmark       | 245         |

|        | 9.7.1    | Fitting into Hardware Memory                  | 245         |

|        | 9.7.2    | Estimation of Memory Compaction Performance   | 247         |

|        | 9.7.3    | BCP Performance Versus Multithreaded Software | 252         |

| 9.8    | 8 Iterat | ive Refinement with Future Benchmarks         | 254         |

| 10 Cc  | onclusio | n                                             | 257         |

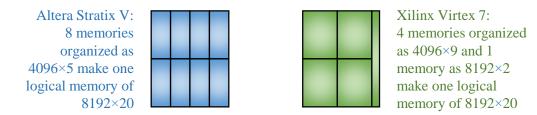

|        |          | atibility with Alternative Technology         | <b>2</b> 57 |

| 10     |          | Xilinx FPGAs                                  | 257         |

|        |          | 3D Silicon Die Stacking                       | 259         |

| 10     |          | sibility of Our Design                        | 260         |

|        |          | nary of Our Contributions                     | 261         |

|        |          | uding Remarks                                 | 261         |

| 10.    |          |                                               | 202         |

| Biblio | ography  |                                               | 263         |

| Index  | ζ        |                                               | 273         |

# List of Figures

| 2.1  | The Tseitin encoding for an AND gate and an XOR gate                                              | 13 |

|------|---------------------------------------------------------------------------------------------------|----|

| 2.2  | Mapping an OR gate into AND to reuse the Tseitin encoding                                         | 14 |

| 2.3  | Loop unrolling enables the tracking of values over time                                           | 14 |

| 2.4  | A miter circuit tests if the outputs can ever be different. $\ldots$ .                            | 15 |

| 2.5  | A miter to test two implementations of the majority function                                      | 16 |

| 2.6  | The search space for a subset of variables is significantly smaller                               | 20 |

| 2.7  | The search on the tree of all possible variable assignments                                       | 21 |

| 2.8  | Under the partial assignment $a = 0$ and $b = 1$ , the clause $(a + \overline{b} + \overline{c})$ |    |

|      | implies $c = 0$ which cuts the $c = 1$ subtree                                                    | 22 |

| 2.9  | Backtracking, as a result of a conflict, helps to prune the search space.                         | 23 |

| 2.10 | Reaching a leaf node means a satisfying assignment has been found                                 | 24 |

| 2.11 | Variables can be assigned in any order so long as the entire space is                             |    |

|      | enumerated                                                                                        | 24 |

| 2.12 | A conflict can be root-caused by analyzing the dependencies                                       | 26 |

| 2.13 | As we assign variables in the clause without satisfying it, we either find                        |    |

|      | a new watcher or there is none left so we must imply a variable. $\ . \ .$                        | 28 |

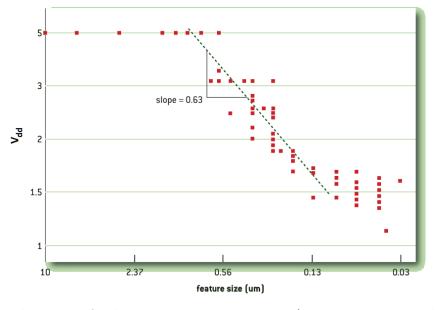

| 3.1  | The trend of voltage versus transistor size                                                       | 37 |

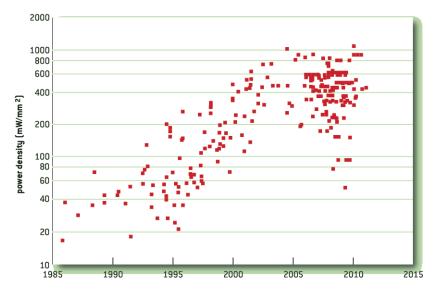

| 3.2  | The trend of power density over time                                                              | 38 |

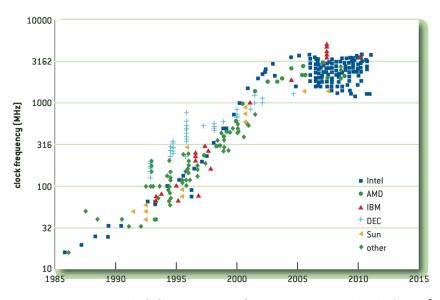

| 3.3  | The trend of CPU speeds                                                       | 39 |

|------|-------------------------------------------------------------------------------|----|

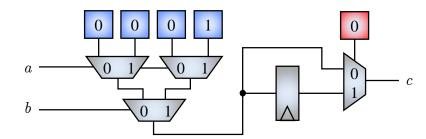

| 3.4  | SRAM memory enables one to change the logic function implemented.             | 42 |

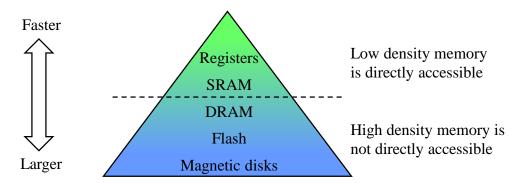

| 3.5  | Different types of memory offer a tradeoff between speed and capacity.        | 46 |

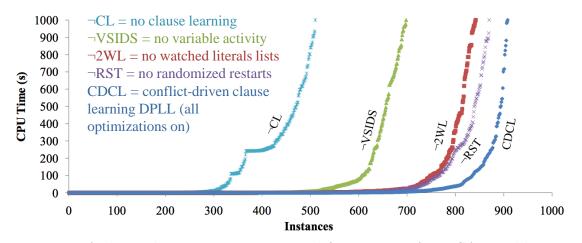

| 3.6  | As key enhancements are removed from DPLL, fewer SAT problems                 |    |

|      | are solvable within the same amount of time                                   | 50 |

| 3.7  | Without multithreading, there are idle times for both hardware and            |    |

|      | software.                                                                     | 56 |

| 3.8  | By running three threads, we can fully utilize the CPU and the FPGA.          | 56 |

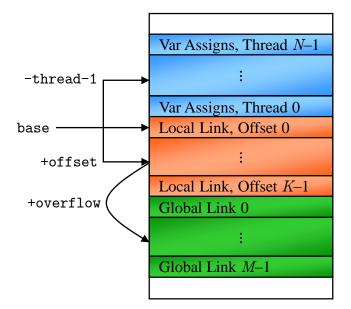

| 4.1  | Watched literals lists must be replicated per thread                          | 62 |

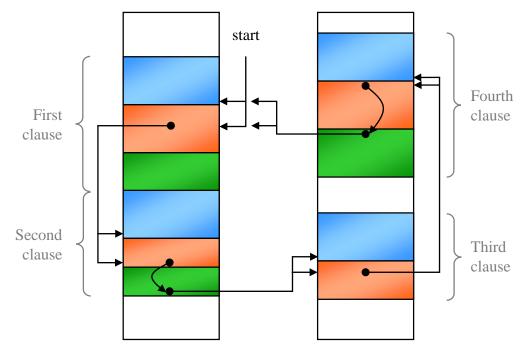

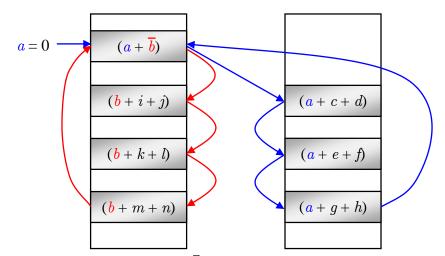

| 4.2  | Two memory layouts for the same SAT problem                                   | 65 |

| 4.3  | Two pointers are placed in each memory location used by the link list.        | 68 |

| 4.4  | Separating communication from computation enables a seamless transfer         |    |

|      | of link list traversal tasks between processors                               | 72 |

| 4.5  | The detailed memory layout for one clause                                     | 73 |

| 4.6  | By dynamically updating assignment as we visit each clause, the original      |    |

|      | clauses can be modified to have only positive variables                       | 80 |

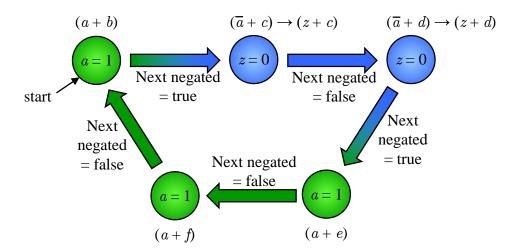

| 4.7  | An example traversal of four clauses                                          | 81 |

| 4.8  | Concurrent traversal of a cyclic link list.                                   | 84 |

| 4.9  | The link list traversal for $a$ is passed to another processor, hence $a$ and |    |

|      | b can be visited concurrently                                                 | 86 |

| 4.10 | A long feedback path can limit the clock speed of the state machine           | 87 |

| 4.11 | Timing of our state machine for traversing link lists to visit clauses        | 89 |

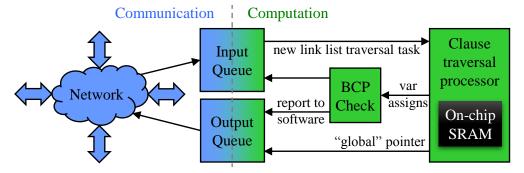

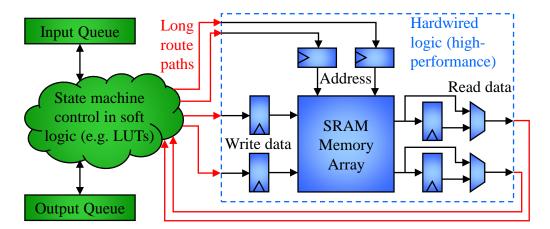

| 5.1  | Our SAT system accelerates only BCP in custom hardware with multiple          |    |

|      | processors that connect using an on-chip network                              | 92 |

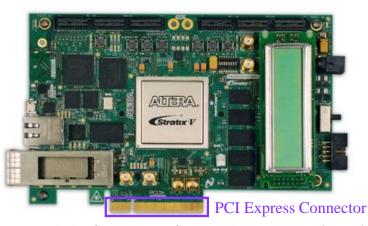

| 5.2  | We used the Stratix V DSP Development Kit from Altera                        | 92  |

|------|------------------------------------------------------------------------------|-----|

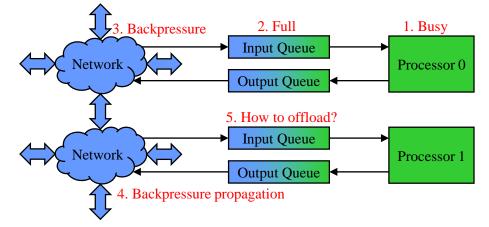

| 5.3  | Backpressure can propagate through the network                               | 97  |

| 5.4  | Using separate paths to offload and reload tasks can hide the small          |     |

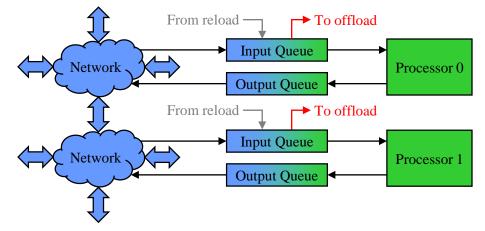

|      | capacity of the input queue from the network on the left                     | 98  |

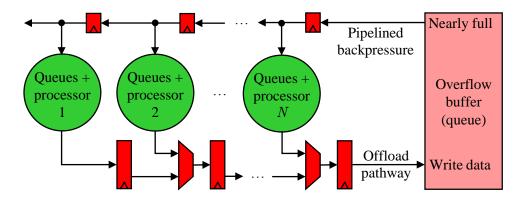

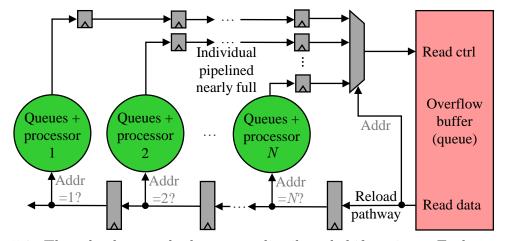

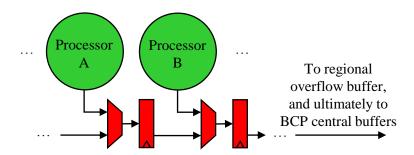

| 5.5  | The offload pathway uses a distributed shift register                        | 100 |

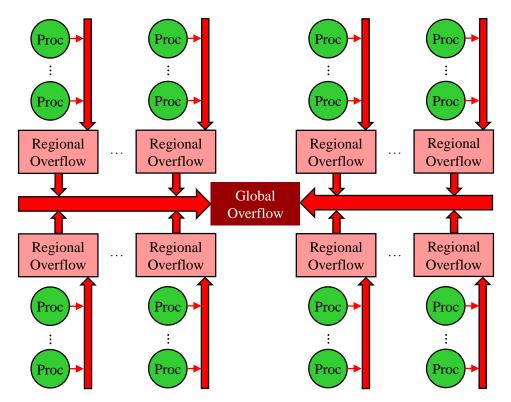

| 5.6  | Processors offload to regional overflow buffers.                             | 101 |

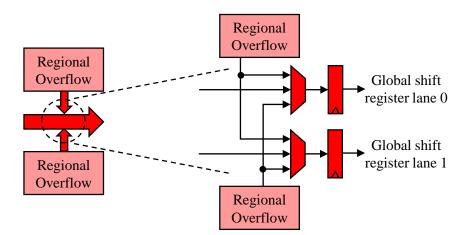

| 5.7  | The global offload shift register has two lanes for increased bandwidth.     | 102 |

| 5.8  | The reload network also uses a distributed shift register                    | 103 |

| 5.9  | BCP collection reuses the offload infrastructure.                            | 105 |

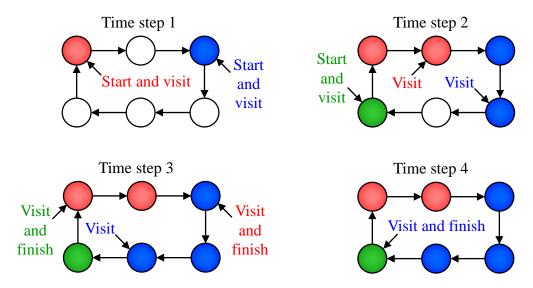

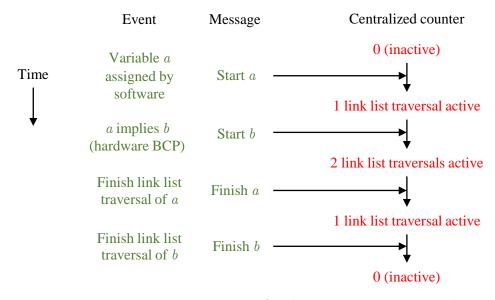

| 5.10 | By counting start and finish messages at a centralized place, we can         |     |

|      | detect when BCP is finished                                                  | 107 |

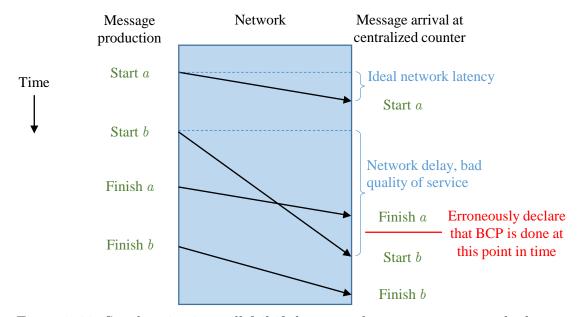

| 5.11 | Synchronization will fail if the network cannot guarantee the latency.       | 108 |

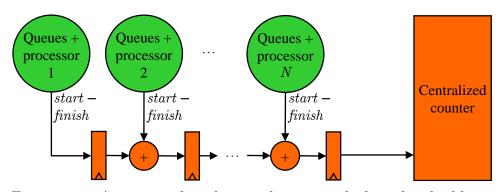

| 5.12 | A counting-based network composed of pipelined adders                        | 109 |

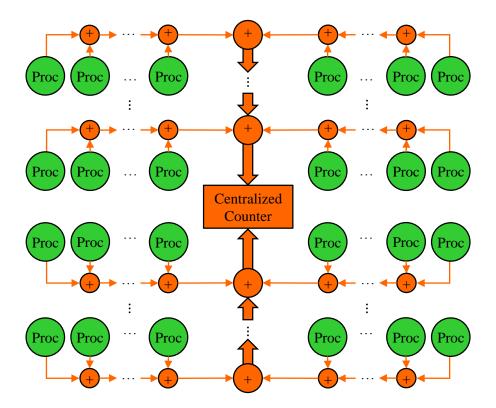

| 5.13 | Using a 2D topology reduces the network latency.                             | 110 |

| 5.14 | To send data from processor 0 to processor 3, it physically has to pass      |     |

|      | through the area occupied by processors 1 and 2                              | 114 |

| 5.15 | A 2-dimensional layout unrolled into a 1-dimensional topology                | 115 |

| 5.16 | A generalized 2-dimensional network switch.                                  | 116 |

| 5.17 | Dimensional routing (first route in $x$ , then route in $y$ ) and removal of |     |

|      | turn-around pathways simplifies the network arbitration                      | 116 |

| 5.18 | Using the outputs of the network ports to drive the inputs of the next       |     |

|      | stage of routing further simplifies the network arbitration. $\ldots$ .      | 117 |

| 5.19 | As BCPs are produced in hardware (new variables are assigned), older         |     |

|      | variables are flushed to software before being overwritten in hardware.      | 124 |

| 5.20 | As variables are deassigned (following a conflict), we may need to        |     |

|------|---------------------------------------------------------------------------|-----|

|      | retrieve older variables from software's memory                           | 125 |

| 5.21 | The components in one processor as well as network connectivity           | 127 |

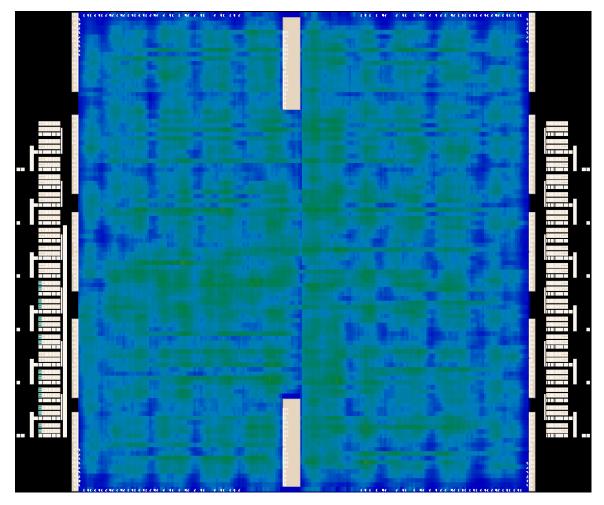

| 5.22 | Where processing blocks should be physically placed on the FPGA           | 129 |

| 5.23 | The floorplan of our final implementation.                                | 130 |

| 5.24 | Routing usage tends to be concentrated within each processing block.      | 132 |

| 6.1  | A hardware multiplexer and a software if-else assignment share the        |     |

|      | same SAT encoding.                                                        | 136 |

| 6.2  | Enhanced BCP enables new propagations not immediately visible from        |     |

|      | the Boolean domain.                                                       | 138 |

| 6.3  | If a clause has few variables, much of the space for the variable assign- |     |

|      | ments is unused.                                                          | 142 |

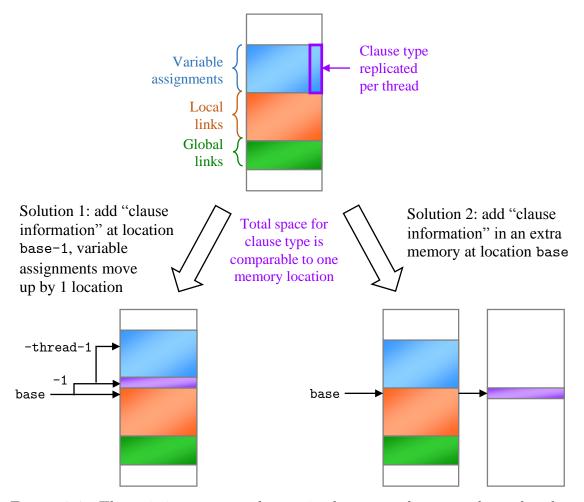

| 6.4  | The clause type replaces one variable assignment                          | 145 |

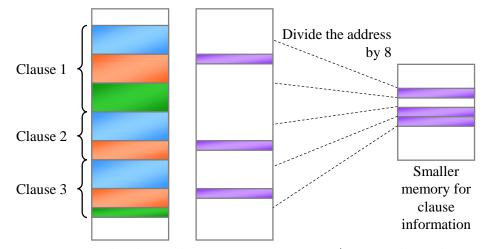

| 6.5  | Because the clauses have minimum spacing (e.g. no closer than 8           |     |

|      | addresses apart), we can compact the clause information memory. $\ . \ .$ | 146 |

| 6.6  | Clause information specifies the packing with a prefix code as well as    |     |

|      | each clause type.                                                         | 151 |

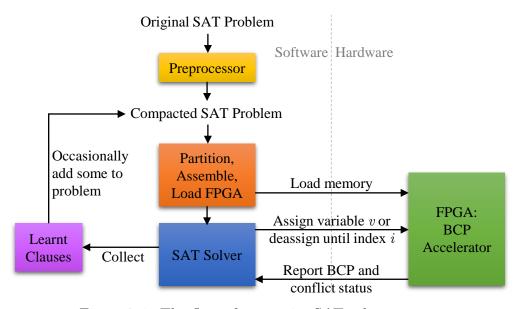

| 7.1  | The flow of our entire SAT solver system                                  | 160 |

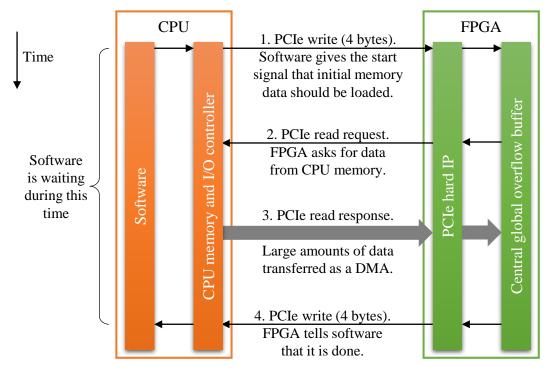

| 7.2  | Loading initial memory data into the FPGA's memory via PCI<br>e           | 163 |

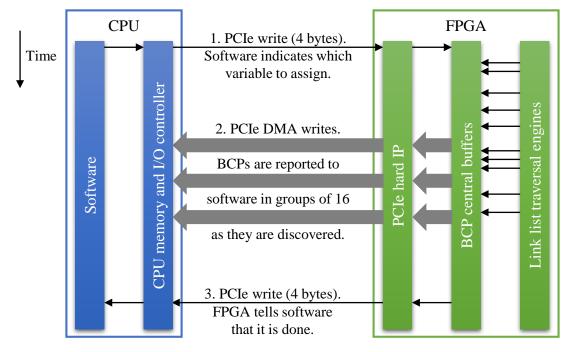

| 7.3  | Hardware BCP starts by software indicating which variable to assign.      | 164 |

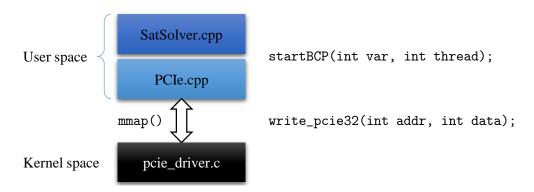

| 7.4  | PCIe access is passed through the hierarchy of our software. $\hdots$     | 165 |

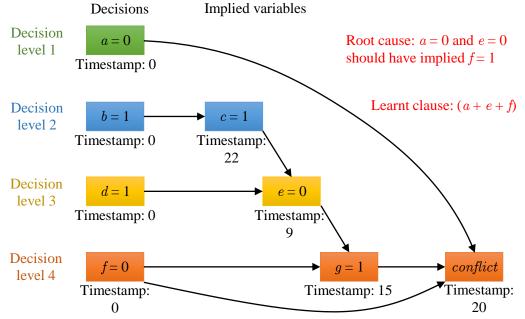

| 7.5  | Conflict analysis sweeps backwards from the conflict. $\ldots$            | 168 |

| 7.6  | Different clauses are used to produce the same conflict                   | 171 |

| 7.7  | Hardware processors report BCPs via the offload network                   | 173 |

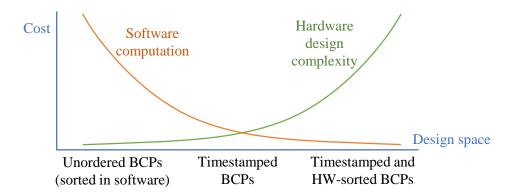

| 7.8  | Complexity of the reordering problem in software versus hardware          | 176 |

|------|---------------------------------------------------------------------------|-----|

| 7.9  | Timestamps on different decision levels are independent of each other.    | 178 |

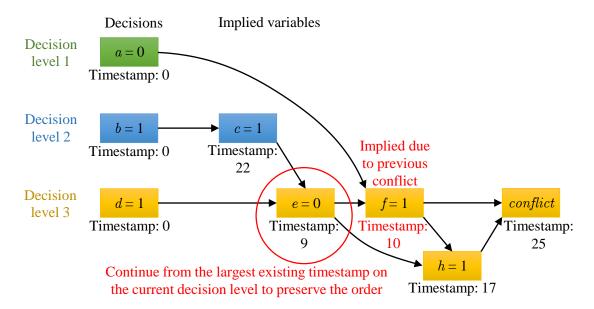

| 7.10 | We need to bias the starting timestamp of $f$ in order to ensure the      |     |

|      | correct ordering for conflict analysis                                    | 178 |

| 7.11 | This conflict creates a learnt clause                                     | 185 |

| 7.12 | Upon encountering a second conflict, the learnt clause is needed in       |     |

|      | order to know the dependencies of $f$ during backtracking                 | 185 |

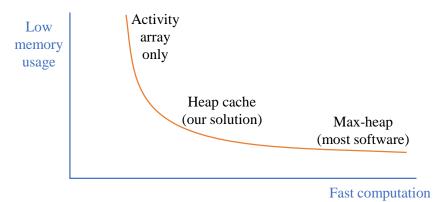

| 7.13 | Fast computation and low memory usage can be traded of<br>f               | 188 |

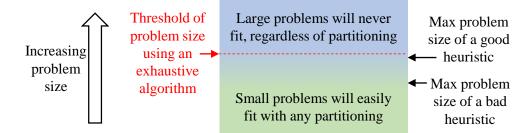

| 8.1  | Better partitioning allows larger SAT problems to fit in memory           | 193 |

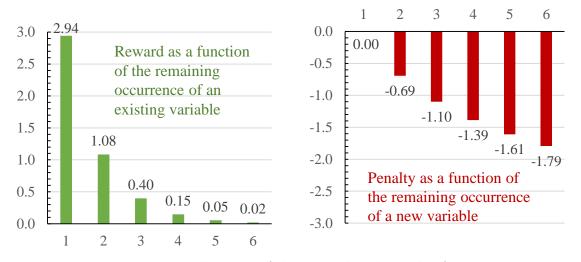

| 8.2  | Visualization of the reward and penalty functions                         | 196 |

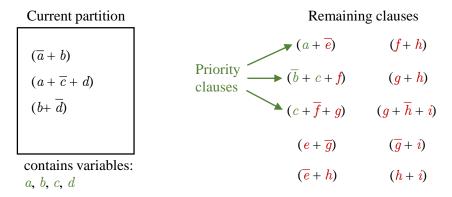

| 8.3  | Priority clauses have some common variable with the current partition.    | 197 |

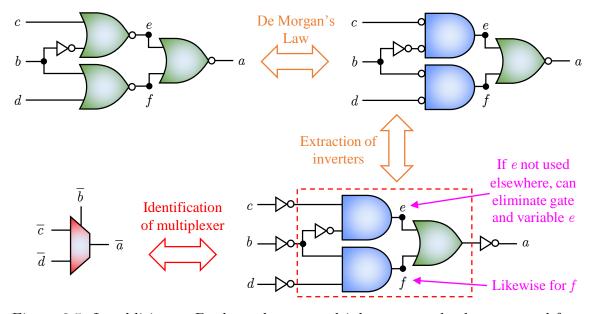

| 8.4  | We can extract Boolean SAT encodings of complex logic structures          | 204 |

| 8.5  | Multiplexers can also be extracted from NOR gates                         | 205 |

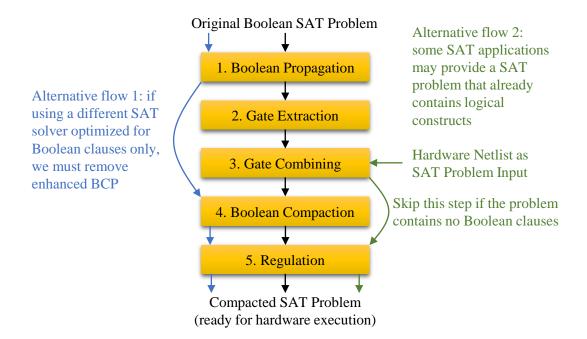

| 8.6  | The flow of our SAT preprocessor can be customized                        | 209 |

| 9.1  | The results from Davis <i>et al.</i>                                      | 218 |

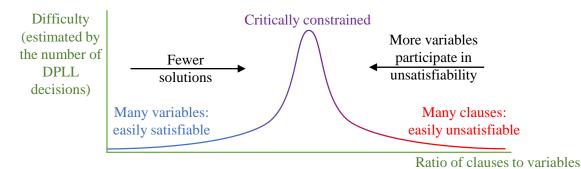

| 9.2  | The ratio of clauses to variables affects the difficulty of SAT problems. | 221 |

| 9.3  | Maximum problem size our hardware supports for Boolean 3-SAT              | 223 |

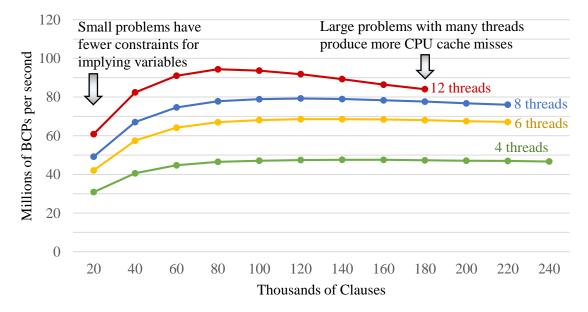

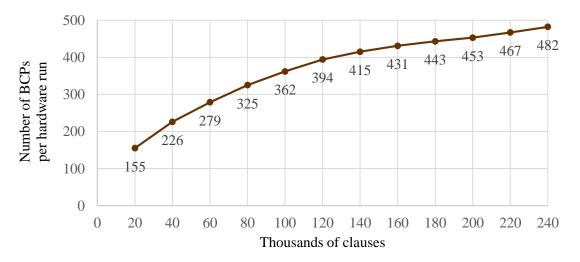

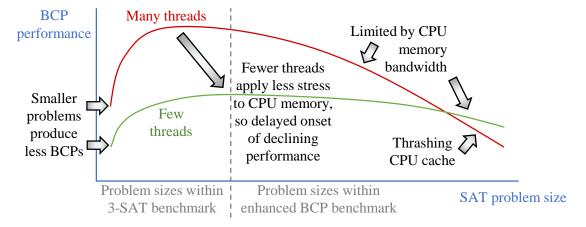

| 9.4  | BCP Performance versus problem size                                       | 224 |

| 9.5  | Average number of BCPs discovered on each round                           | 224 |

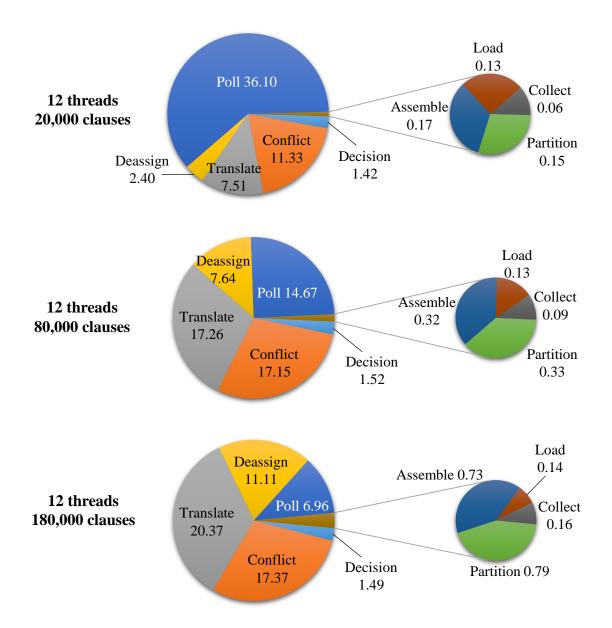

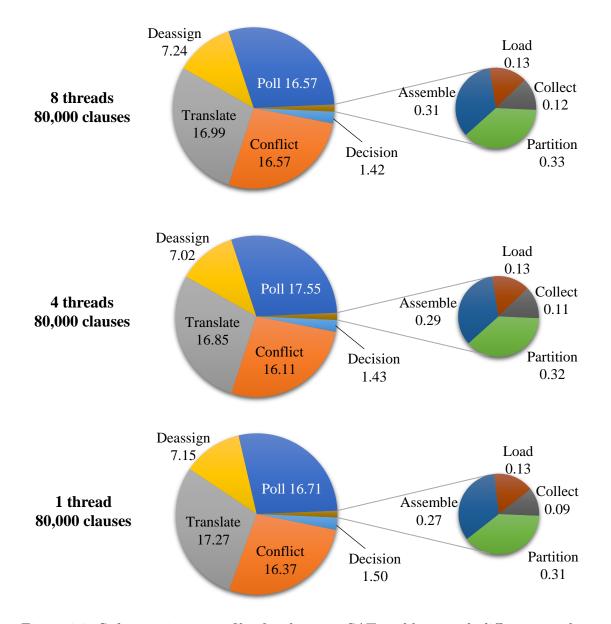

| 9.6  | Software timing profiles for different Boolean 3-SAT problem sizes        | 226 |

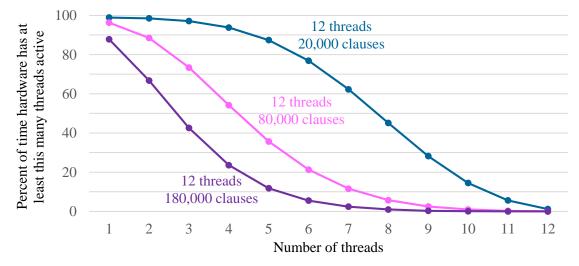

| 9.7  | Thread occupancy of hardware with 12 threads                              | 227 |

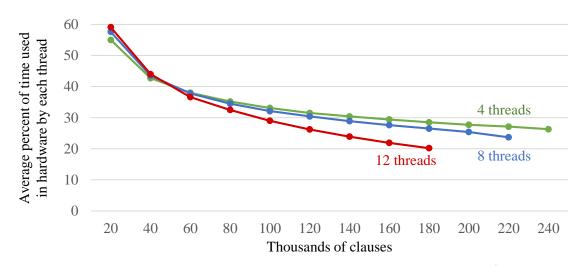

| 9.8  | Average amount of time that each thread uses in hardware                  | 228 |

| 9.9  | Software timing profiles for different numbers of threads                 | 229 |

|      | Software thining promos for different numbers of threads                  | 220 |

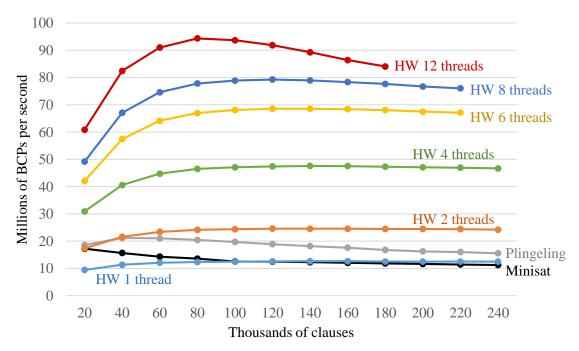

| 9.11 | BCP performance of Plingeling                                      | 231 |

|------|--------------------------------------------------------------------|-----|

| 9.12 | BCP performance of Minisat.                                        | 232 |

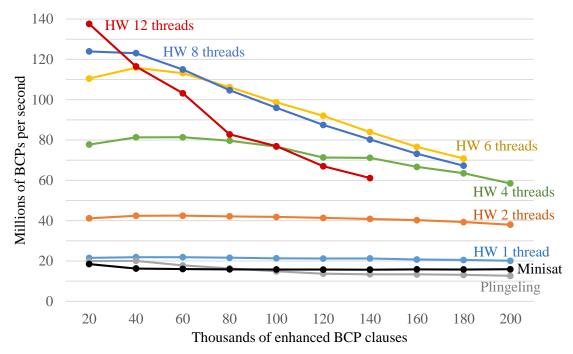

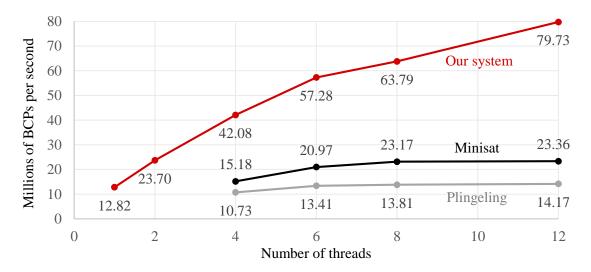

| 9.13 | Our hardware BCP performance versus multithreaded software         | 233 |

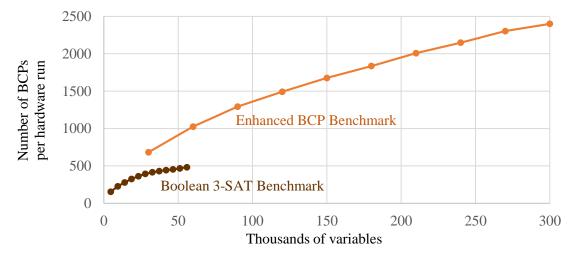

| 9.14 | With enhanced BCP, we support significantly larger SAT problems    | 235 |

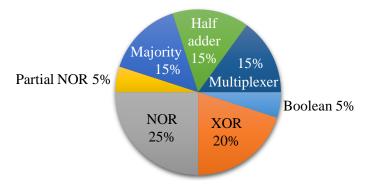

| 9.15 | Distribution of the enhanced BCP clause types                      | 235 |

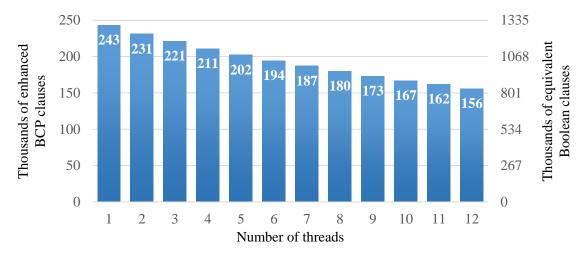

| 9.16 | Maximum problem size our hardware supports for enhanced BCP        | 236 |

| 9.17 | Amalgamation of trends between the Boolean 3-SAT and enhanced      |     |

|      | BCP benchmarks                                                     | 239 |

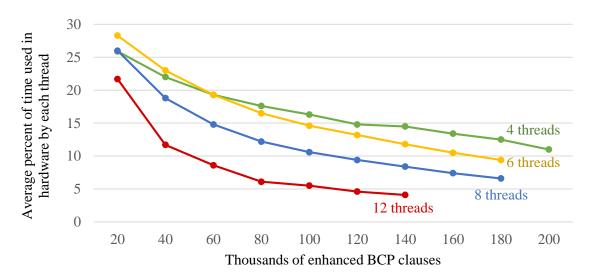

| 9.18 | Average amount of time that each thread uses in hardware           | 240 |

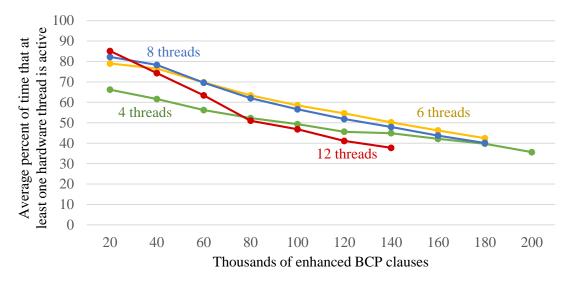

| 9.19 | Average amount of time that at least one hardware thread is active | 240 |

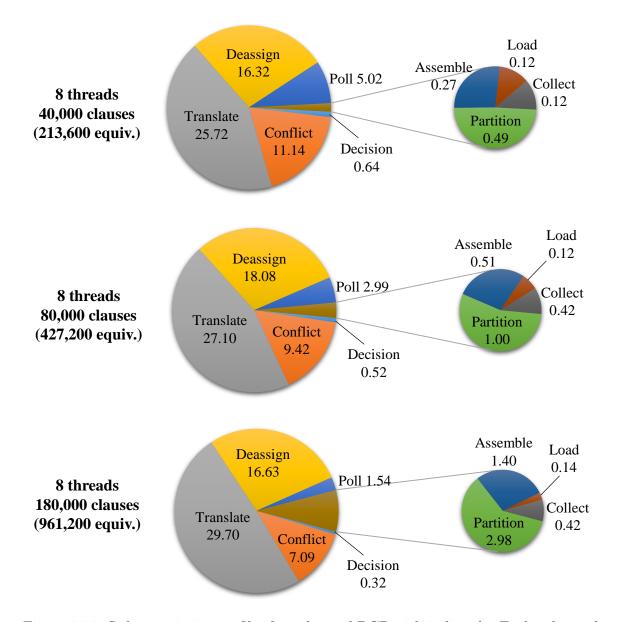

| 9.20 | Software timing profiles for enhanced BCP with 8 threads           | 241 |

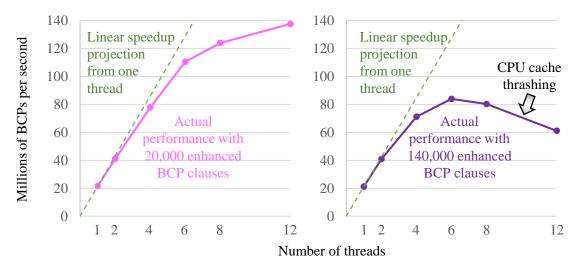

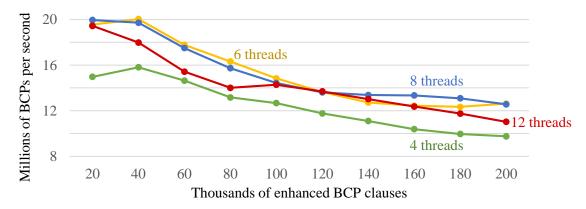

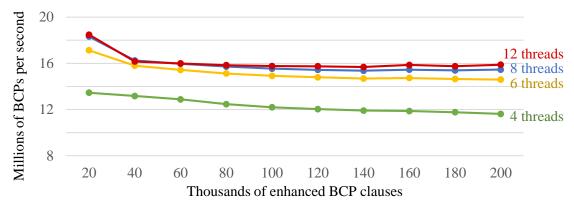

| 9.21 | BCP rate on the same problems with varying number of threads       | 242 |

| 9.22 | BCP performance of Plingeling                                      | 243 |

| 9.23 | BCP performance of Minisat.                                        | 243 |

| 9.24 | Our hardware BCP performance versus multithreaded software         | 244 |

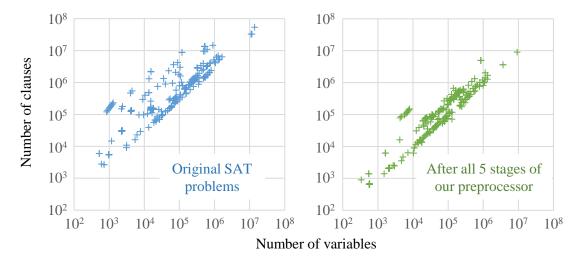

| 9.25 | Problem sizes in the SAT Competition 2013 applications benchmark.  | 246 |

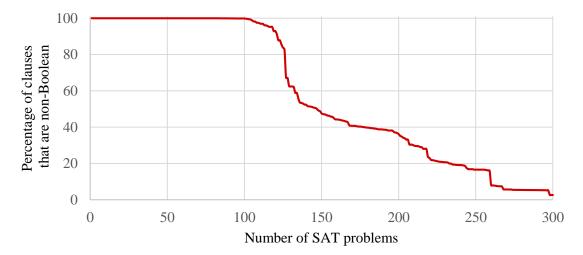

| 9.26 | Utilization of enhanced BCP.                                       | 248 |

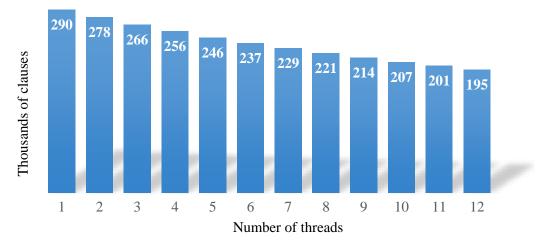

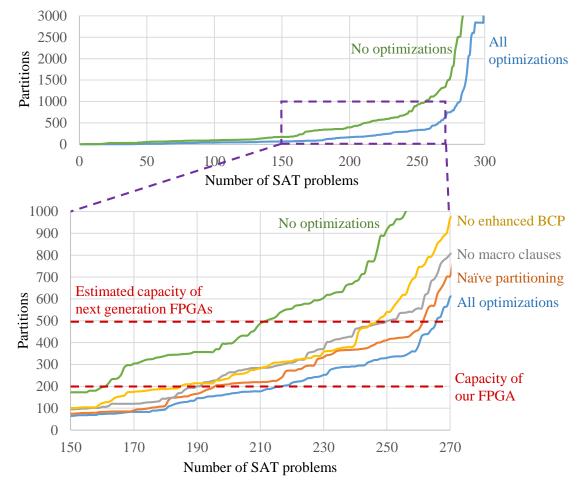

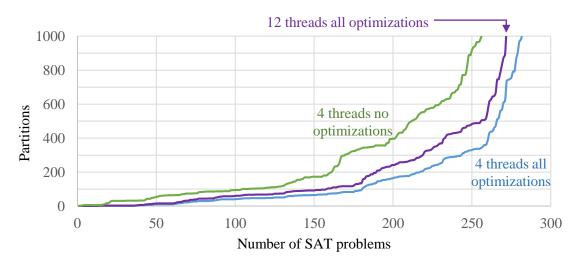

| 9.27 | Number of partitions needed for 4 threads                          | 249 |

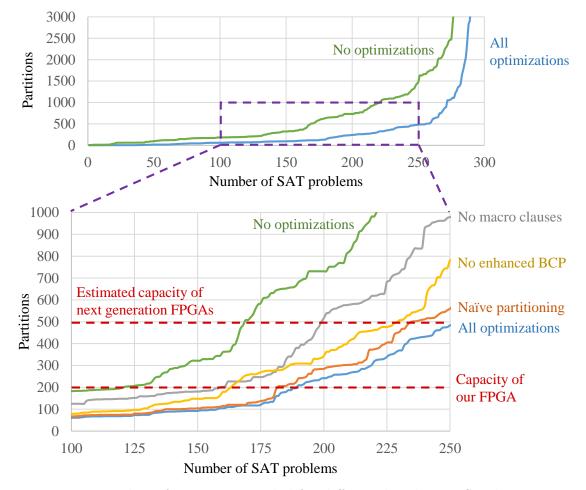

| 9.28 | Number of partitions needed for 12 threads                         | 250 |

| 9.29 | Number of partitions needed for 4 threads versus 12 threads        | 251 |

| 9.30 | Average BCP performance on the SAT Competition 2013 applications   |     |

|      | benchmark.                                                         | 252 |

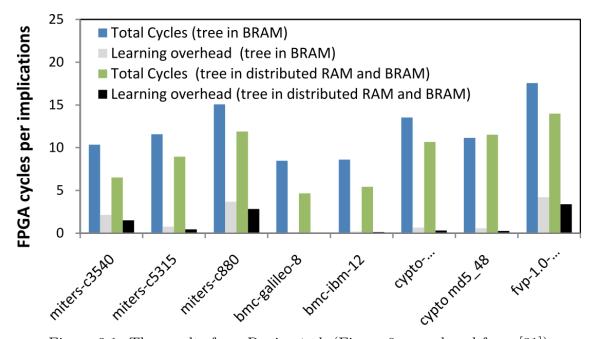

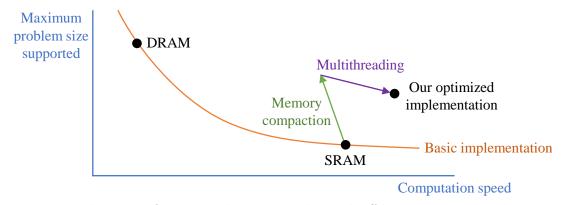

| 9.31 | The type of memory determines the tradeoff between speed and size. | 254 |

| 10.1 | Different physical memories can construct the same logical memory  | 258 |

# List of Tables

| 2.1 | The clauses for the SAT problem corresponding to Figure 2.5          | 16  |

|-----|----------------------------------------------------------------------|-----|

| 3.1 | Transistor scaling                                                   | 36  |

| 3.2 | Maximum capabilities of modern FPGAs.                                | 41  |

| 3.3 | DRAM random access is about $6\%$ of achievable performance and is   |     |

|     | comparable with software BCP                                         | 47  |

| 3.4 | A summary of the suitability for SAT for various memory types        | 49  |

| 3.5 | An example partitioning of a SAT problem.                            | 54  |

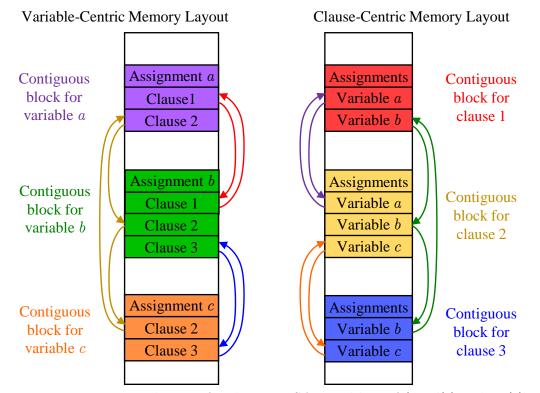

| 4.1 | Description of the two candidate memory layouts                      | 65  |

| 4.2 | Comparison of the two memory layouts.                                | 66  |

| 5.1 | Summary of the on-chip networks                                      | 121 |

| 5.2 | Comparison of the features of the on-chip networks                   | 122 |

| 6.1 | Summary of all enhanced BCP clause types currently supported in      |     |

|     | hardware                                                             | 139 |

| 6.2 | Summary of all of the supported clause packings                      | 150 |

| 6.3 | Encodings for link lists of length 2 to 24 inclusive                 | 157 |

| 9.1 | Resource utilization of our entire FPGA design in relation to device |     |

|     | capacity                                                             | 215 |

| 9.2 | Top level distribution of resources.                                 | 215 |

| 9.3  | Average resource utilization for one processor                         | 216 |

|------|------------------------------------------------------------------------|-----|

| 9.4  | Sizes of the SAT problems benchmarked in Figure 9.1                    | 219 |

| 9.5  | Millions of BCPs per second for the problems that were actually avail- |     |

|      | able from Table 9.4                                                    | 219 |

| 9.6  | Detailed performance of our system on the Boolean 3-SAT problems.      | 222 |

| 9.7  | BCP speedup over the best performance of multithreaded software for    |     |

|      | a varying number of hardware threads                                   | 233 |

| 9.8  | Distribution of the enhanced BCP clause sizes                          | 235 |

| 9.9  | Number of SAT problems with 20,000 clauses solved within 1 minute.     | 237 |

| 9.10 | Detailed performance of our system on the enhanced BCP benchmark.      | 238 |

| 9.11 | BCP speedup over the best performance of multithreaded software for    |     |

|      | a varying number of hardware threads                                   | 244 |

| 9.12 | Statistics for the problems from the SAT Competition 2013 applications |     |

|      | benchmark that we were able to fit into hardware memory                | 247 |

| 9.13 | Number of partitions used                                              | 247 |

| 9.14 | Average number of clauses per partition                                | 250 |

| 9.15 | Statistics from all SAT Competition 2013 applications problems that    |     |

|      | fit in hardware at each number of threads                              | 253 |

| 9.16 | Millions of BCPs per second in the SAT Competition 2013 applications   |     |

|      | benchmark.                                                             | 255 |

## Chapter 1

## Introduction

The ability to efficiently compute solutions for discrete problems has many practical implications. Many real-world problems are inherently discrete or combinatorial. For example, suppose we are driving a car on streets organized in a two dimensional grid, e.g. running north-south and east-west. If we are currently driving north and want to go somewhere north-west of the current location, it is physically impossible to turn two-thirds to the left, for instance. The discreteness of the problem dictates that we must perform a combination of driving some distance north as well as some distance west in order to arrive at the desired location.

Combinatorial problems commonly exist in two forms: as a *satisfiability* problem or as an *optimization* problem. Continuing with examples, suppose some streets have construction which completely blocks vehicles from driving. We may be interested in solving a feasibility problem, e.g. a tour company may want to know if it is possible to visit every street intersection exactly once without reusing any section of any street. We may be interested in solving an optimization problem, e.g. knowing how long it takes to drive down any given street, what is the fastest way to make such a tour? Whether we are optimizing the driving time of vehicles on the road or optimizing packets through a telecommunications network, the approach to solving such combinatorial problems tends to be similar.

Discrete problems are often solved using a *decision-based* approach. Returning to our first example, if we are currently driving north, at the next street intersection we must choose whether to keep driving north or turn left to the west. The structure of the problem determines which decisions are valid, and may also guide the decision procedure (e.g. we want to avoid construction which blocks certain streets).

For some discrete problems, the only guaranteed way to find a solution is with an exhaustive search. This results in an extremely large computational complexity. We discuss NP-completeness in section 2.1.1.

The lengthy compute time needed to solve some discrete problems can make them prohibitively impractical. This is presently one of the major challenges facing combinatorial problems. Some optimization problems use heuristics to reduce the compute time, however there is no substitute when using satisfiability for verification, e.g. does there exist a counter-example that causes the system to behave incorrectly?

Much of the research community has focused on developing new search strategies. This thesis addresses an orthogonal issue: we explore how different implementation technologies can increase the computational throughput. An efficient design requires an insightful remapping of the problem to maximize the strengths of each underlying technology. Algorithms and data structures have to be fundamentally rethought.

This chapter introduces the Boolean satisfiability problem (SAT) with a simple and intuitive example. The organization of the thesis is presented before we conclude this chapter with the scope of our contributions.

### 1.1 An Introduction to SAT

In general, a satisfiability problem consists of some *given* constraints which contain variables, and one must *find* an assignment to those variables to satisfy all constraints or prove that no such assignment exists. As an example, suppose we must satisfy:

$$x + 2y \le 4$$

$$2x + y \ge 5$$

where x and y are the variables. One solution to this is x = 2 and y = 1.

In Boolean SAT, each variable can only be assigned true or false. Constraints are also referred to as "clauses". A clause must be satisfied by satisfying at least one of the variables, thus we OR the variables. For example, to satisfy the clause  $(a + \overline{b})$ , we can assign a = true or b = false, or both. All clauses in the SAT problem must be satisfied, hence we AND the clauses together. Conclusively, one example of a Boolean SAT problem could be:

$$(a+\overline{b})(\overline{a}+\overline{c}+d)(b+\overline{d})$$

One solution is a = 1, b = 1, c = 0, and d = 1 (0 means false and 1 means true).

#### 1.1.1 An Intuitive Example of Boolean SAT

We now present an example to provide an intuitive perspective of Boolean SAT. Suppose there are three friends Alice, Bob, and Charlie who want to buy some icecream. The store where they buy it from only sells 3 flavors: mint, strawberry, and chocolate. We can use Boolean variables m, s, and c to indicate whether or not they will buy each respective flavor. Now let us introduce the constraints. Suppose Alice does not care for mint, but she will accept it if chocolate is purchased. Thus the first clause is:

$$(\overline{m}+c)$$

.

The SAT interpretation is that if m = 1 (mint was purchased), the only remaining way to satisfy the clause is to assign c = 1 (chocolate must also be purchased). This is the premise of Boolean constraint propagation, as examined in section 2.5.1.

Bob wants one of mint or strawberry but not both. In other words, if and only if mint is purchased, then strawberry should not be purchased. The example with Alice illustrated how to encode just a simple "if", so now we use two clauses to cover both halves of the "if and only if":

$$(m+s)(\overline{m}+\overline{s}).$$

Notice that the first clause is not satisfied if neither are purchased and the last clause is not satisfied if both are purchased.

Charlie is hungry and wants at least two flavors. This can be represented with three clauses:

$$(m+s)(m+c)(s+c).$$

If only one flavor is purchased (only one variable is assigned as true), then only two out of the three clauses will be satisfied. At least one more variable must be assigned as true in order to satisfy all three clauses.

Finally, we ask the question: is there a combination of ice-cream flavors that Alice, Bob, and Charlie can buy to satisfy their requirements? Removing the duplicate clause (m + s), the corresponding SAT problem to solve is:

$$(\overline{m}+c)(m+s)(\overline{m}+\overline{s})(m+c)(s+c).$$

One solution is m = 1, s = 0, c = 1. For each flavor, the corresponding variable indicates whether or not to purchase it.

#### 1.1.2 Variations of Boolean SAT

Continuing the previous example, now suppose that one unit of ice-cream has a different cost depending on the flavor, e.g. mint costs \$3, strawberry costs \$4, and chocolate costs \$5. We could instead solve an optimization problem: what is the specific combination of ice-cream flavors that Alice, Bob, and Charlie should buy to minimize the cost while satisfying their requirements?

For applications that operate primarily on integers instead of Boolean variables, one may encode the problem to preserve the high-level semantics. For example, we could instead represent that Charlie wants at least two flavors with:

$$(m+s+c \ge 2)$$

where m, s, and c are now integers in the range of 0 to 1. Integer linear programming is a close cousin of Boolean SAT, as both are based on discrete constraints.

Moving back to satisfiability (no optimization), suppose a problem is unsatisfiable. Some applications may be interested in extracting more information, such as what is the maximum number of clauses that can be satisfied (this count must be strictly less than the total number of clauses). Alternatively, one may be interested in which subset of clauses participated in causing the unsatisfiability.

#### **1.1.3** Definitions and Terminology

To formalize SAT from our previously intuitive example, we now briefly provide some definitions to commonly used terminology in the satisfiability research community.

**Definition 1.** A "clause" is a constraint describing a relationship among several variables that must be satisfied.

In Boolean SAT, each clause takes the form  $(x_1 + x_2 + x_3 + \ldots + x_n)$ , where each  $x_i$  is a Boolean variable which may be assigned only true or false. To satisfy a clause, at least one *literal* must be satisfied. For example, to satisfy the clause  $(x_1 + \overline{x}_2)$ , we could assign  $x_1 =$  true or  $x_2 =$  false, or both.

**Definition 2.** A "literal" is a variable with a particular sign.

For example,  $x_1$  and  $\overline{x}_1$  are instances of the *same* variable  $x_1$ . Conversely, the positive literal  $x_1$  and the negative literal  $\overline{x}_1$  are *different* literals.

**Definition 3.** A "satisfiability problem" consists of several clauses. For a <u>given</u> satisfiability problem, the objective is to <u>find</u> an assignment to the variables that satisfies every clause, or prove that no such assignment exists.

For example, given the Boolean SAT problem  $(x_1 + \overline{x}_2)(x_2 + \overline{x}_3 + x_4)(x_1 + \overline{x}_3 + \overline{x}_4)$ , one solution is to assign all four variables as true. Conversely, the Boolean SAT problem  $(\overline{x}_1 + \overline{x}_2)(\overline{x}_1 + x_2)(x_1 + \overline{x}_2)(x_1 + x_2)$  has no solution.

Definition 4. The "clause size" refers to how many variables it contains.

Intuitively, a larger Boolean clause is easier to satisfy. Smaller clauses typically participate in Boolean constraint propagation more frequently (see section 2.5.1).

### 1.2 Thesis Organization

Chapter 2 discusses the applications of SAT as well as software algorithms for solving SAT. We also present concrete examples which illustrate how some applications are mapped into SAT. In chapter 3, we examine current technology trends in detail. This motivates the use of hardware accelerated SAT and also identifies the limitations of most prior works on SAT in hardware.

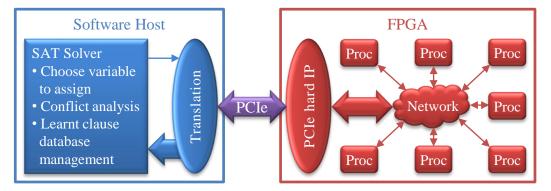

We use technology trends to guide our design decisions, which are summarized in section 3.6. We only accelerate part of the SAT solver in hardware. Some types of computation are ideal for custom hardware while others are better suited for a CPU (software). Heterogeneous computing enables us to maximize the benefit of each.

We present our hardware processor in chapter 4. Chapter 5 then illustrates how these communicate with each other and with software. Chapter 6 examines advanced optimizations in hardware. Software integration is discussed in chapter 7 (SAT solver integration) and chapter 8 (additional software, such as SAT preprocessing).

Experimental results of our entire system are finally presented in chapter 9. A massive implementation effort was required to evaluate our ideas. Concluding remarks are summarized in chapter 10.

### **1.3** The Scope of Our Contributions

Many discrete or combinatorial problems are solved using a decision-based approach. This class of problems is typically difficult to accelerate due to the complex control flow. Our acceleration of SAT addresses many of these complexities as well as physical aspects which can no longer be ignored in the design of digital circuits. Our contributions are manifested in the insightful restructuring of computation and data structures, as well as resolving several of the ensuing complications. The concepts, designs, and techniques used to solve these problems have generalizable properties. For example, chapter 4 demonstrates several ways to facilitate faster computation while also minimizing the amount of memory needed to represent SAT in hardware. Implicit representations and lossless compression are powerful tools, and these will be useful in other memory bound problems. In chapter 5, we classify different types of on-chip communication so that we can exploit the different properties of each class to obtain efficient implementations. In general, some applications can benefit from separating synchronization networks from data.

We make no claim of improving SAT algorithms, as surveyed in chapter 2. This is *orthogonal* to our acceleration of Boolean constraint propagation (BCP), which is the dominant computation within a SAT solver (see section 2.5.1). BCP is a fundamental part of all DPLL-based SAT solvers, so by implementing the remainder of our SAT solver in software, we facilitate an easy integration of *any* future DPLL enhancement.

Finally, our extensive use of lossless compression enables us to benchmark SAT problems in uncharted territory. We are significantly faster than software on real-life SAT problem sizes, unlike many existing hardware SAT designs which only support problem sizes too small to be of much practical interest. We are also the first to introduce multithreading into hardware SAT. Using a real implementation (not simulation), for the first time we are able to accurately observe system limitations such as thrashing the CPU's shared cache with numerous threads. Such factors are no longer trivial for highly accelerated computation. We have extensively designed our computing platform to mitigate these wherever it is practically possible.

## Chapter 2

## SAT Applications and Algorithms

This chapter begins by surveying the numerous applications of SAT. We then illustrate how some applications are mapped into SAT using concrete examples. The remainder of the chapter examines the basic approaches used in several different types of SAT algorithms. We also discuss many of the newer optimizations for DPLL, which is arguably the most common SAT algorithm used. Finally, we discuss preprocessing techniques, which simplify a SAT problem without changing its satisfiability.

## 2.1 Applications of SAT

#### 2.1.1 NP-Completeness and a Historical Perspective

Boolean SAT was the first NP-complete problem, as proved by Cook [1] in 1971. NP stands for "non-deterministic polynomial". These problems must be deterministically verifiable and non-deterministically solvable (e.g. with the luckiest possible guess), both within polynomial time. NP does *not* mean "non-polynomial". This misconception often arises since there are currently no known algorithms to deterministically solve

NP-complete problems in polynomial time. Presently there is also no proof that such algorithms cannot exist. This is the famous P = NP problem. We refer the reader to [2] for more details on the theory and proofs of NP-completeness.

In 1972, Karp [3] demonstrated that 21 other problems were also NP-complete since there exists a polynomial time many-one reduction from Boolean SAT to each of the 21 problems. The solution to any NP-complete problem can be obtained by instead solving any other NP-complete problem and then applying a polynomial time transformation to obtain the solution to the original problem.

Prior to the 1990s, NP-complete problems were arguably mostly a theoretical interest and primarily used to demonstrate the intractability of new problems. In other words, it was a strong motivator for heuristics or approximate algorithms.

Complete algorithms for solving SAT date back as far as the 1960s, e.g. DPLL [4]. However, much of the smartness in "modern" SAT solvers was developed in the late 1990s and early 2000s. As the computing power grew over the decades, in the 1990s it eventually reached a threshold where solving SAT became practical. This instilled lots of research on ways to solve SAT more efficiently.

Modern SAT solvers have radically changed the picture for NP-complete problems. They can learn the internal structure of a SAT problem and aggressively prune the search space. Because of this smartness, the worst case exponential run time of a SAT solver is often not exposed by many real-world SAT problems.

Presently there are many efficient SAT solvers, so it is now common for one to solve a hard combinatorial problem by instead converting it to Boolean SAT. Using this approach, SAT has found itself at the core of many applications (an extensive survey is provided in [5]). SAT has therefore become an enabling technology.

#### 2.1.2 Survey of SAT Applications

Throughout this section, we briefly discuss some common applications of SAT. New applications are emerging and thus it is impossible to provide an exhaustive list.

SAT plays a major role in Electronic Design Automation (EDA), which uses computer-aided design (CAD) tools to verify or optimize problems that are inherently discrete. On the verification side of EDA, SAT can be used for equivalence checking [6,7]. When a compiler performs optimizations, the functionality of the optimized implementation should still exactly match the behavior as specified in the source code. A detailed example is demonstrated in section 2.2.2.

SAT can be used for hardware verification [8] and software verification [9], typically through model checking [10,11]. For example, we may want to ensure a hardware state machine always finishes its computation within 8 clock cycles. In software, we could ensure that we never access out-of-bounds memory or perform undefined computation, such as dividing by zero. Run-time assertions that simply *check* this, for example:

```

x = 0;

for (i=0; i<10; i++) {

j = permute_function(i);

assert(j>=0 && j<5); //array was allocated for 5 items

x = x + array[j];

}

assert(x != 0);

y = z / x;

```

may not be particularly useful in safety-critical systems. Verification either proves we can avoid bad states by construction or it produces an actual counter-example.

On the optimization side of EDA, SAT can be used for logic synthesis. A fieldprogrammable gate array (FPGA) typically implements combinational logic using lookup tables (LUTs), thus SAT can be used to decompose the logic from a given hardware design to best utilize the LUTs [12]. SAT can also be used to solve routing (how to wire logic gates together) for both FPGAs [13] and standard cells [14].

Automatic test pattern generation (ATPG) screens logic circuits for manufacturing defects. SAT can be used to design ATPG test sequences that either maximize the coverage (how much of the circuit gets tested) for a limited number of test sequences, or minimize the number of test sequences (reduce testing time and costs) to achieve at least some threshold of coverage. Examples of SAT-based ATPG include [15, 16].

Cryptography is another major application of SAT [17]. For example, for all y with a Hamming distance of 1 from x, we could ensure that  $encrypt(x) \neq encrypt(y)$ .

SAT plays a major role in scheduling problems [18]. SAT is good at capturing constraints such as: any two tasks that require a shared resource cannot run in the same time interval. Graph coloring also captures this well, and it is one of the 21 problems proven NP-complete by Karp [3]. Many similar problems exist in artificial intelligence, especially for planning-based problems [19]. For example, knowing which moves a robot can make, find a legitimate plan of motion to reach the goal state.

As computation power continues to grow and SAT solvers become increasingly efficient, SAT could become an enabling technology for completely new applications. Recently, SAT has found itself in applications such as bioinformatics. A SAT-based approach to characterizing single nucleotide mutations in DNA is presented in [20]. Protein design can be assisted by SAT, which finds the lowest energy states to predict how a sequence of amino acids will fold into a protein [21].

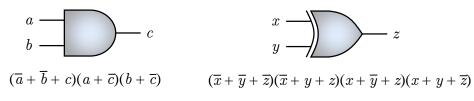

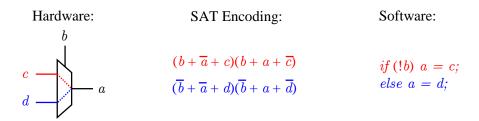

Figure 2.1: The Tseitin encoding for an AND gate and an XOR gate.

# 2.2 Mapping Logical Constructs to SAT

#### 2.2.1 Logical Construct Encoding

We begin by illustrating how logical constructs are mapped to SAT. This serves as a precursor before we demonstrate the mapping of real applications to SAT.

Logical constructs are the building blocks of digital systems. When describing the behavior of a digital system, there is no need to differentiate between a multiplexer in hardware or a software assignment made using an if-else statement.

Logical constructs are commonly mapped to Boolean SAT using the Tseitin encoding [22]. For example, the encodings of an AND gate and an XOR gate are shown in Figure 2.1. The clauses in the encoding have an intuitive explanation. For the AND gate:

- (\$\overline{a} + \overline{b} + c\$) indicates that if \$a = 1\$ and \$b = 1\$, then we must have \$c = 1\$ (this is the only *remaining* way to satisfy the clause, Boolean constraint propagation is discussed in section 2.5.1).

- $(a + \overline{c})$  indicates that if a = 0, then we must have c = 0. Alternatively, the contrapositive is that if c = 1, then we must have a = 1.

- By symmetry, the same idea applies to  $(b + \overline{c})$  as it did to  $(a + \overline{c})$ .

$(a + b + \overline{c})(\overline{a} + c)(\overline{b} + c)$

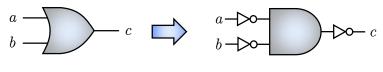

Figure 2.2: Mapping an OR gate into AND to reuse the Tseitin encoding.

d \_\_\_\_\_ q

Unroll over *n* clocks:  $(d_0 + \overline{q}_1)(\overline{d}_0 + q_1)\dots(d_{n-1} + \overline{q}_n)(\overline{d}_{n-1} + q_n)$

Figure 2.3: Loop unrolling enables the tracking of values over time.

For the XOR gate, all possible combinations of signs for the first two variables xand y are considered, as shown below in blue:

$$(\overline{x} + \overline{y} + \overline{z})(\overline{x} + y + z)(x + \overline{y} + z)(x + y + \overline{z})$$

Once both x and y are assigned, exactly one of the four possible cases will require the last variable z (shown above in red) to take a certain value in order to satisfy that clause. For example, if x = 1 and y = 0, the second clause requires z = 1 to be satisfied. There is a symmetry between the variables, so if any two variables are assigned, the third variable can be implied.

Inversion comes for free in SAT by simply exchanging x and  $\overline{x}$ . Figure 2.2 shows the encoding of an OR gate. Using De Morgan's Law, we can reuse the Tseitin encoding of an AND gate.

Figure 2.3 illustrates how software loops or hardware state information can be unrolled to track how values will evolve over iterations or time, respectively. Model

Figure 2.4: A miter circuit tests if the outputs can ever be different.

checking applications use a bounded model to avoid an infinite number of states. More recent work on unbounded model checking typically uses SAT to produce a proof (e.g. by induction) that certain behavior will be maintained in the steady state.

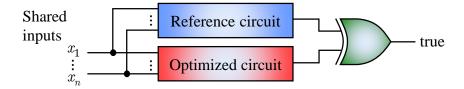

#### 2.2.2 A Demonstration of Equivalence Checking

Equivalence checking can be used to verify the correctness of optimizations. For example, the behavior of a system optimized by a compiler should still match the reference source code. Figure 2.4 illustrates the "miter" circuit for verifying this. By constraining the XOR output to true, we are looking for a counter-example. Solving the corresponding SAT problem either produces one or guarantees that none exist.

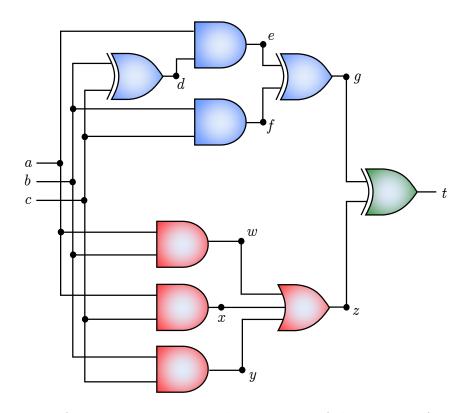

As an example, in Figure 2.5 we illustrate two implementations of the majority function, which is true if at least two out of the three inputs are true. This arises in adders (specifically it is the carry logic for a 1-bit full adder). The blue subcircuit is the implementation that arises from cascading two half adders in order to create one full adder. The red subcircuit could be a speed optimization, as the longest combinational path has improved from 3 gates to 2 gates. The green XOR serves as the miter. We can force the output t to true by using a clause with only one variable. The only way to satisfy the clause (t) is by assigning t = 1. The derivation of the corresponding SAT problem is summarized in Table 2.1, which has a total of 32 clauses.

| Table $2.1$ : | The clauses : | for the | SAT | problem | correspon | nding to | o Figure 2.5. |

|---------------|---------------|---------|-----|---------|-----------|----------|---------------|

|               |               |         |     |         |           |          |               |

| Description         | Clauses                                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------------------|

| d = b  XOR  c       | $(\overline{b} + \overline{c} + \overline{d})(\overline{b} + c + d)(b + \overline{c} + d)(b + c + \overline{d})$ |

| e = a AND $d$       | $(\overline{a} + \overline{d} + e)(a + \overline{e})(d + \overline{e})$                                          |

| f = b AND $c$       | $(\overline{b} + \overline{c} + f)(b + \overline{f})(c + \overline{f})$                                          |

| g = e  XOR  f       | $(\overline{e} + \overline{f} + \overline{g})(\overline{e} + f + g)(e + \overline{f} + g)(e + f + \overline{g})$ |

| w = a AND $b$       | $(\overline{a} + \overline{b} + w)(a + \overline{w})(b + \overline{w})$                                          |

| x = a  AND  c       | $(\overline{a} + \overline{c} + x)(a + \overline{x})(c + \overline{x})$                                          |

| y = b AND $c$       | $(\overline{b} + \overline{c} + y)(b + \overline{y})(c + \overline{y})$                                          |

| z = w  OR  x  OR  y | $(w+x+y+\overline{z})(\overline{w}+z)(\overline{x}+z)(\overline{y}+z)$                                           |

| t = g  XOR  z       | $(\overline{g} + \overline{z} + \overline{t})(\overline{g} + z + t)(g + \overline{z} + t)(g + z + \overline{t})$ |

| t = true            | (t)                                                                                                              |

Figure 2.5: A miter to test two implementations of the majority function.

#### 2.2.3 Using Integers in Boolean SAT

Most digital systems use integers which each have multiple bits. Conversely, SAT is limited to Boolean variables. The technique of "bit-blasting" can be used to represent one integer with several Boolean variables. For example, consider this Verilog code which describes a 4-bit adder in hardware:

module adder(a, b, s); input [3:0] a; input [3:0] b; output [3:0] s; assign s = a + b; endmodule

We can introduce Boolean variables  $a_3, a_2, a_1, a_0$  for a, and likewise for b and s. For simplicity, assume this is implemented as a ripple-carry adder. We will also need Boolean variables  $c_4, c_3, c_2, c_1, c_0$  to represent the value of each intermediate carry signal. The logic for a ripple-carry adder is as follows. For n = 0, 1, 2, 3:

- Sum bit:  $s_n = a_n$  XOR  $b_n$  XOR  $c_n$ .

- Carry bit:  $c_{n+1} = \text{majority}(a_n, b_n, c_n)$ .

We assign the initial carry  $c_0 =$  false, and  $c_4$  is not computed since it is not used. The logic for the majority function was shown in the example from section 2.2.2.

By using bit blasting, Boolean SAT can be used to find a feasible point in an integer linear programming problem, for example. Extensions of SAT into higher-level logic are known as Satisfiability Modulo Theories (SMT). SMT solvers typically follow one of two strategies: so-called "eager" SMT solvers use bit blasting to obtain an equivalent Boolean SAT problem whereas "lazy" SMT solvers will internally use a "theory solver" to try to solve the problem in its high-level format (without bit blasting). The extensions that SMT provide over SAT are *orthogonal* to the contributions from this thesis. We refer the reader to [23, 24] for a comprehensive analysis of SMT.

# 2.3 Local Search SAT Algorithms

One way to solve SAT is to simply take a guess at how the variables should be assigned and then check if it satisfies the problem. If not then make another guess, and keep repeating until a solution is found. This is the basic strategy used in local search SAT algorithms, such as GSAT [25] and WalkSAT [26].

After a random assignment to all variables is initialized, typically local search algorithms iteratively flip the assignment of one variable (true becomes false and vice versa) until the variable assignments satisfy all clauses. Algorithms differ in how they choose which variable assignment to flip. GSAT flips the variable which minimizes the number of unsatisfied clauses using the new assignment. WalkSAT uses a similar strategy, but it first randomly chooses one unsatisfied clause to narrow the candidates of which variable may flip. Randomized restarts are also used, which is analogous to simulated annealing. A survey of more recent techniques is provided in [27].

Local search SAT algorithms are often referred to as *incomplete* SAT algorithms since they cannot prove a problem is unsatisfiable. Guaranteeing coverage of the entire search space requires storing an exponential number of previous assignments or using of a pre-defined variable order. Either would result in poor algorithm performance. Even so, not being able to prove unsatisfiability can be irrelevant for some applications. Constrained random generation [28] is one such example. Suppose one wants to stress test a network card with random data. Arbitrary random data may not form legal network packets. To test it properly, one must ensure that the random data is conformant, e.g. certain fields in the network packet header must be set to certain legal values. In order to provide enough test coverage, the corresponding SAT problems must inherently be loosely constrained (and therefore easily satisfiable).

## 2.4 Unsatisfiable-Based SAT Algorithms

Goldberg introduced the stable set of points (SSP) method [29], which can prove a SAT problem is unsatisfiable by induction. The premise for this algorithm is that if a modern SAT solver is able to prove a problem with millions of variables is unsatisfiable within a reasonable amount of time, typically this is due to only a *small fraction* of the variables that actually participate in the conflict (e.g. a few thousand variables).

As a contrived example (the color scheme matches Figure 2.6):

$$(a+b)(a+\overline{b})(\overline{a}+b)(\overline{a}+\overline{b})(a+c+d)(\overline{b}+e)(f+\overline{g}+h)\dots(x+y+z)$$

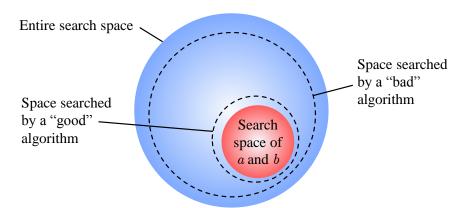

is unsatisfiable because of only the first four (red) clauses. Additional (blue) clauses may expand the search space since they contain more variables, however they do not influence the unsatisfiability (which only variables a and b affect). The search space of this problem is illustrated in Figure 2.6. If we could direct the SAT solver to stay within the search space of only a and b (the red region of Figure 2.6), we could obtain a minimalistic proof that the problem is unsatisfiable. Naturally we would expect such an algorithm to run faster than if it also had to visit much of the blue region.

Figure 2.6: The search space for a subset of variables is significantly smaller.

Notice that local search algorithms (section 2.3) explore over unsatisfiable points since they terminate as soon as a satisfying variable assignment is found. However, if we can prove that these unsatisfiable points form a closed (self-containing) set, then problem is necessarily unsatisfiable. This is the main idea of SSP.

Continuing the above example, suppose we start a search with all variables assigned false. The first clause (a + b) would not be satisfied. To fix this, we must flip the assignment of a or b. In general, by recursively looking at all possible updates that a local search algorithm could make (in this example, this would include flipping both a and b), we try to show that we can never escape the unsatisfiability. Like local search, we can also stop as soon as a satisfying variable assignment is found.

To improve the efficiency, the stable set can be searched in clusters [30] by using partial variable assignments (only some variables are assigned, the others are in a "don't care" state). Continuing the above example, assigning a = 0, b = 0, and leaving all other variables unassigned is still unsatisfiable. In other words, no matter how we assign the remaining variables, it is impossible to produce a satisfying assignment. However, it is unclear exactly how the clusters are represented and we think that the memory complexity could be exponential with respect to the number of variables.

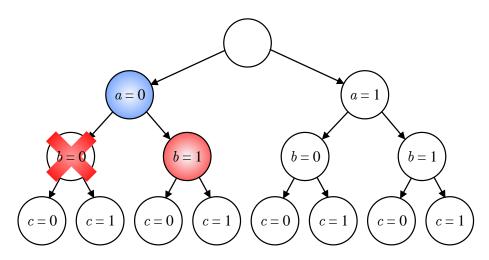

Figure 2.7: We begin the search on the tree of all possible variable assignments by assigning a = 0. The clause (a + b) then implies b = 1 must also be assigned.

# 2.5 The DPLL Algorithm and its Enhancements

#### 2.5.1 The Basics of DPLL

The Davis-Putnam-Logemann-Loveland algorithm [4] was created in the 1960s before SAT was proven NP-complete, yet it still serves as the basis for many modern SAT solvers (which also have sophisticated enhancements). DPLL performs a depth-first search on the tree of all possible variable assignments. We illustrate this with an example. Suppose our SAT problem is:

$$(a+b)(a+\overline{b}+\overline{c})(a+\overline{b}+c)(\overline{a}+b+c).$$

In Figure 2.7, we begin the tree search by assigning a = 0. At this point, all other variables are unassigned. If we were to then also assign b = 0, it would be impossible to satisfy the problem regardless of the assignment to the remaining variables. The clause (a + b) implies that we must assign b = 1 given that a = 0.

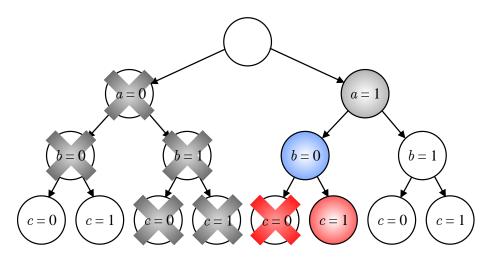

Figure 2.8: Under the partial assignment a = 0 and b = 1, the clause  $(a + \overline{b} + \overline{c})$ implies c = 0 which cuts the c = 1 subtree, likewise  $(a + \overline{b} + c)$  implies c = 1.

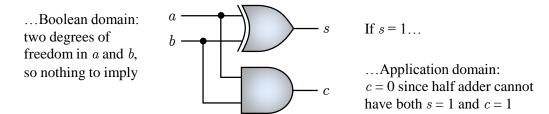

DPLL directs its search by trying to maintain satisfiability, as opposed to SSP from section 2.4 which directs its search in the unsatisfiable region of the space. DPLL prunes branches of the search tree once they are known to be unsatisfiable. This is done with Boolean constraint propagation (BCP). In general, constraint propagation is not restricted to just Boolean clauses. It operates in an intuitive manner:

If we have not yet satisfied a clause, and

If all variables in that clause are assigned except for one variable,

Then we must assign that last variable in the way that will satisfy the clause.

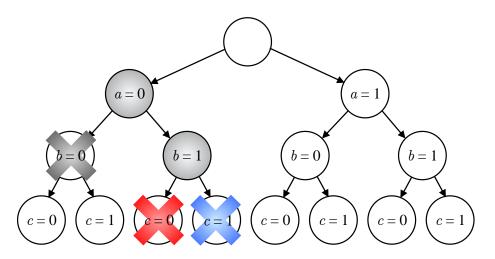

Continuing the above example, we now have a = 0 and b = 1. Following the rules of BCP, the clause  $(a + \overline{b} + \overline{c})$  implies c = 0. This is illustrated by the blue X in Figure 2.8, which prunes the c = 1 subtree. Likewise  $(a + \overline{b} + c)$  implies c = 1, so the red X cuts the c = 0 subtree. Having pruned both subtrees, it is clear that a = 0 and b = 1cannot lead to a satisfying assignment.

Figure 2.9: Backtracking, as a result of a conflict, helps to prune the search space.

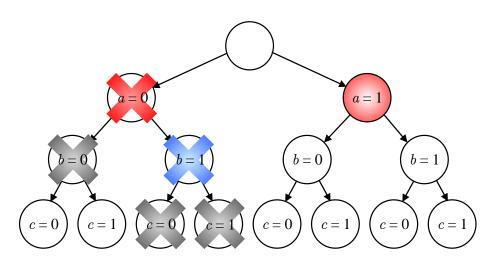

Conflicts are useful because they help to prune the search tree. Now we must backtrack the search, as shown by the blue X in Figure 2.9. With only a = 0 assigned, notice that b = 0 was earlier pruned by BCP and now we have just pruned b = 1, therefore we continue backtracking. Eventually we conclude that if this problem actually has a satisfying assignment, it must have a = 1. This is shown by the red parts of Figure 2.9. Note that a = 1 is implied (it is not a search decision).

Upon inspection of the clauses, there are no variables that can be implied. Therefore we continue the tree search by assigning b = 0. The clause  $(\overline{a} + b + c)$  implies c = 1, as shown in Figure 2.10. Once we reach a leaf node, the path from here to the root of the tree specifies a satisfying assignment. Otherwise we would eventually prune the entire tree, in which case the problem would be unsatisfiable.

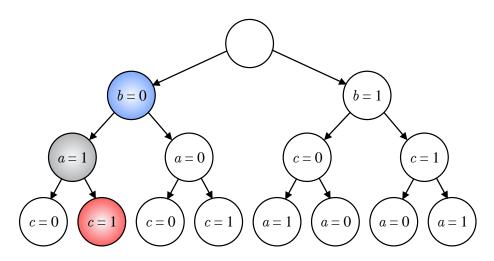

One major degree of freedom in DPLL is the order in which variables are assigned. For example, we could have instead examined variable b first. Furthermore, different subtrees may have a different variable ordering, as illustrated in Figure 2.11. If there is nothing left to imply, any unassigned variable in the current subtree can be selected

Figure 2.10: Reaching a leaf node means that a satisfying assignment has been found.

Figure 2.11: Variables can be assigned in any order so long as the entire space is enumerated. The same satisfying assignment from Figure 2.10 is shown here.

for assignment, and we can choose whether to first assign it true or false. Determining the best ordering of variables is an open research problem and it has a significant impact on the effectiveness and practicality of DPLL-based SAT solvers. One very commonly used heuristic is VSIDS, which we discuss in section 2.5.2.4.

#### 2.5.2 Key Enhancements to DPLL

# 2.5.2.1 Non-Chronological Backtracking, Conflict Analysis, and Learnt Clauses

Conflicts closer to the root of the search tree result in a larger amounts of pruning and therefore are more beneficial. Maintaining a purely depth-first search can hinder this. As example, consider this SAT problem (only the blue clauses will be involved in what we will demonstrate):

$$(a+y+\overline{z})(x+\overline{y})(y+z)(\overline{b}+\overline{c})(\overline{d}+\overline{e}+\overline{f})\dots(\overline{v}+\overline{w})$$

Suppose a SAT solver assigns the variables as false in alphabetical order. We start by assigning a = 0, and no variables can be implied all the way to assigning w = 0. When we then assign x = 0, the second clause  $(x + \overline{y})$  implies y = 0, then the first clause  $(a + y + \overline{z})$  implies z = 0, yet the third clause (y + z) cannot be satisfied. Figure 2.12 shows a graph of the dependencies. A conflict means we made a bad guess at the last assignment. In this case, we deassign x, y, and z, and then we can imply x = 1.

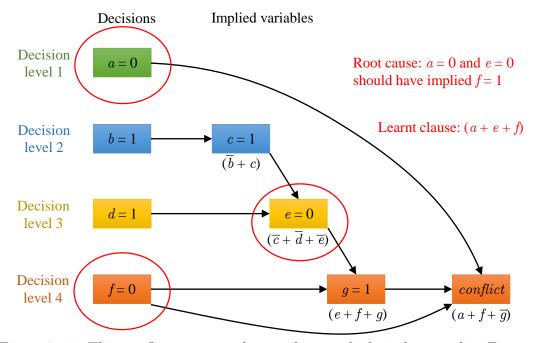

However, the search remains in the a = 0, ..., w = 0 subtree, so not much pruning is achieved. Notice the other variables (b through w) did not participate in the conflict. Essentially we have pruned the a = 0 and x = 0 subtree, which is a full one quarter of the search space. To obtain stronger pruning, we could jump the search to a = 0and x = 1 (with none of the other variables assigned). This idea of conflict-driven "non-chronological backtracking" was introduced by the GRASP SAT solver [31].

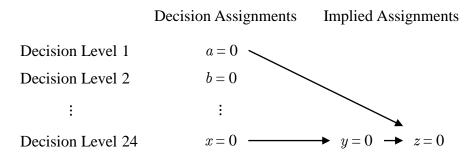

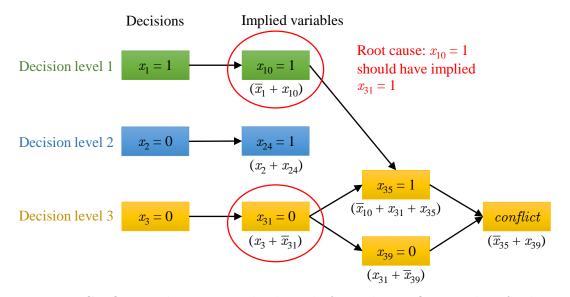

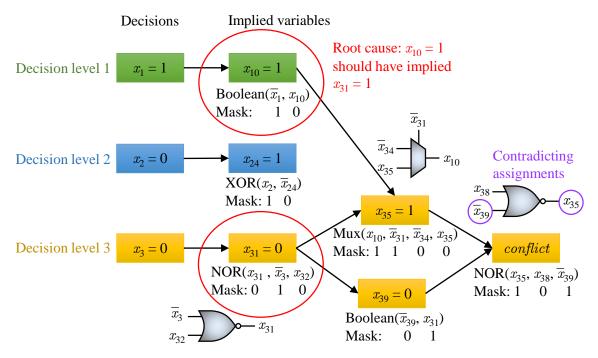

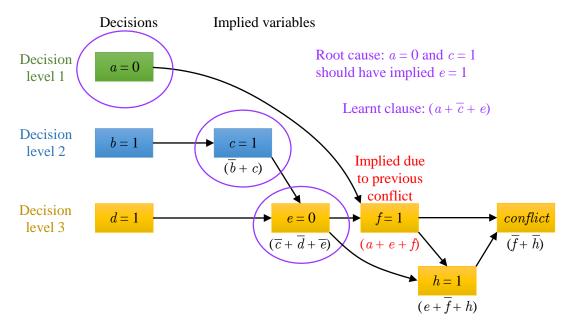

To determine where we can jump the backtracking to, a root cause analysis is required when we encounter a conflict. Zhang *et al.* [32] introduced conflict analysis

Figure 2.12: A conflict can be root-caused by analyzing the dependencies of implied assignments. Decision level refers to how deep in the search tree we currently are.

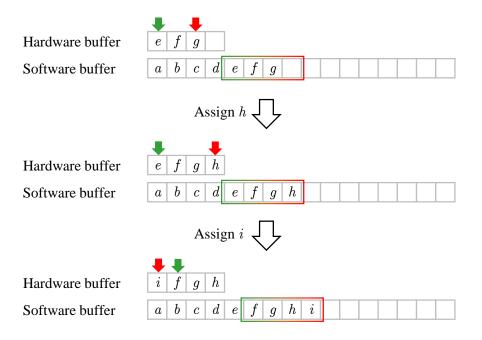

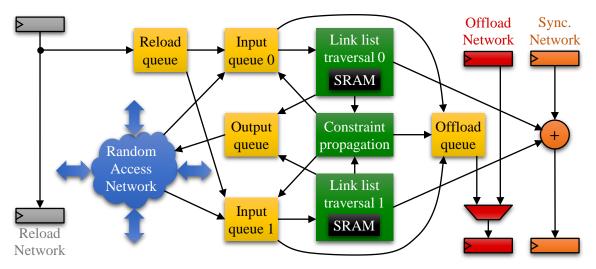

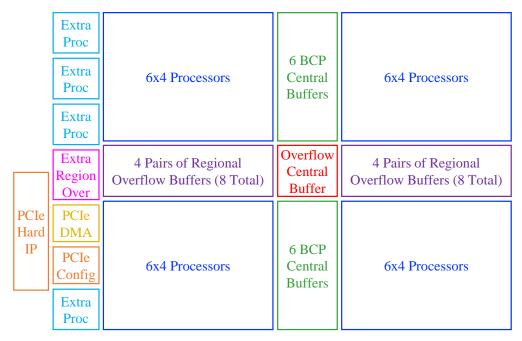

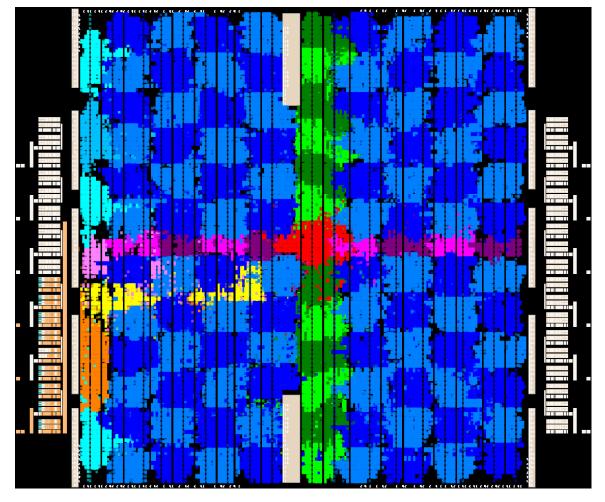

using the unique implication point (UIP). For instance, looking at the dependencies in Figure 2.12, only a = 0 and y = 0 would also produce the same conflict. UIP-based analysis favors this since it is closer to the conflict than our earlier example of a = 0and x = 0. Notice that if we jump the search back to a = 0 and y = 1 instead, we can still imply x = 1 due to  $(x + \overline{y})$ . However, if we jump the search back to a = 0 and x = 1 as originally described, we know nothing about y since  $(x + \overline{y})$  is satisfied.