# **University of Southampton**

# LOW-COST TEST FOR CORE-BASED SYSTEM-ON-A-CHIP

by

Paul Theo Gonciari

A thesis submitted in partial fulfilment of the requirements for the degree of Doctor of Philosophy in the Faculty of Engineering and Applied Science Department of Electronics and Computer Science

December 2002

### UNIVERSITY OF SOUTHAMPTON

### ABSTRACT

# FACULTY OF ENGINEERING AND APPLIED SCIENCE DEPARTMENT OF ELECTRONICS AND COMPUTER SCIENCE

#### Doctor of Philosophy

### LOW-COST TEST FOR CORE-BASED SYSTEM-ON-A-CHIP

#### by Paul Theo Gonciari

The availability of high level integration leads to building of millions of gates systemson-a-chip (SOC). Due to the high complexity of SOCs, testing them is becoming increasingly difficult. In addition, if the current test practises are maintained, the high cost of test will lead to a considerable production cost increase. To alleviate the test cost problem, this research investigates methods which lead to *low-cost test of core-based systems-on-a-chip* based on test resource partitioning and without changing the embedded cores. Analysing the factors which drive the continuous increase in test cost, this thesis identifies a number of factors which need to be addressed in order to reduce the cost of test. These include volume of test data, number of pins for test, bandwidth requirements and the cost of test equipment. The approaches proposed to alleviate the cost of test problem have been validated using academic and industrial benchmark cores.

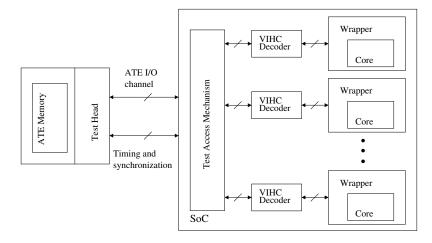

To reduce the volume of test data and the number of pins for test, the new Variablelength Input Huffman Coding (VIHC) test data compression method is proposed, which is capable of simultaneously reducing the volume of test data, the test application time and the on-chip area overhead, when compared to previously reported approaches. Due to the partitioning of resources among the SOC and the test equipment, various synchronisation issues arise. Synchronisation increases the cost of test equipment and hence limits the effectiveness of test resource partitioning schemes. Therefore, the synchronisation issues imposed by test data compression methods are analysed and an on-chip distribution architecture is proposed which in addition to accounting for the synchronisation issues also reduces the test application time.

The cost of test equipment is related to the amount of test memory, and therefore efficient exploitation of this resource is of great importance. Analysing the memory requirements for core based SOCs, useless test data is identified as one contributor to the total amount of allocated memory, leading to inefficient memory usage. To address this problem a complementary approach to test data compression is proposed to reduce the test memory requirements through elimination of useless test data.

Finally, a new test methodology is proposed which combines the approaches proposed in this thesis into an integrated solution for SOC test. The proposed solution leads to reduction in volume of test data, test pins, bandwidth requirements and cost of test equipment. Furthermore, the solution provides seamless integration with the design flow and refrains from changing the cores. Hence, it provides a low-cost test solution for corebased SOC using test resource partitioning.

# Acknowledgements

I wish to thank my supervisor Dr. Bashir Al-Hashimi for his help and assistance, for his guidance and encouragement throughout this PhD. I am grateful for his invaluable help during the preparation of this thesis and several papers.

This PhD would have not been possible without the generous funding and computing facilities provided by the Department of Electronics and Computer Science, University of Southampton, for which I am grateful. Thanks are also due to the members of the Electronic Systems Design Group which have inspired me with their support. In particular I wish to acknowledge Dr. Neil J. Ross for serving on my nine-month and MPhil transfer, and for his constructive criticism.

I wish to thank my friend and colleague Dr. Nicola Nicolici for his guidance, constructive comments and supervision throughout the period of this PhD. I am grateful for the numerous late night technical discussions, especially before paper submission deadlines. I would also like to thank the Department of Electrical and Computer Engineering for providing the required computing facilities during the 3 months period whilst I was a visiting researcher in McMaster University.

I am thankful to my friends Marcus Schmitz, Mauricio Varea, Neil Henderson, Mircea Gândila, Reuben Wilcock and Manoj Gaur, to name a few, for their support and for providing feedback on several occasions. Special thanks are due to Paul Rosinger for intriguing discussions and valuable feedback throughout this PhD. I am also thankful to my landlord for putting up with me for the period of this PhD, and for introducing me to simplicity. Thanks are also due to Monika and Daniel Benta for their support whilst I was staying in Germany. Special thanks go to Ioana Oarga, for her love and for reminding me of the important things in life.

Last but certainly not least, this work could have not been carried out without the unshakable love, encouragement and tolerance of my mother Renate, father Matei, brother Demis, aunt Gerlinde and my grandmother Anna, to whom I am forever thankful.

# **Table of Contents**

| Al | Abstract ii |           |                                                        |    |  |

|----|-------------|-----------|--------------------------------------------------------|----|--|

| 1  | Intr        | roduction |                                                        |    |  |

|    | 1.1         | Core b    | based System-on-a-Chip design                          | 2  |  |

|    |             | 1.1.1     | Design flow                                            | 3  |  |

|    |             | 1.1.2     | Core based design                                      | 7  |  |

|    | 1.2         | Core b    | based System-on-a-Chip test                            | 8  |  |

|    |             | 1.2.1     | System level DFT                                       | 11 |  |

|    |             | 1.2.2     | Automated test equipment (ATE)                         | 16 |  |

|    | 1.3         | Cost o    | f test                                                 | 18 |  |

|    |             | 1.3.1     | Cost of test execution                                 | 20 |  |

|    | 1.4         | Thesis    | contributions and organisation                         | 24 |  |

| 2  | Prev        | vious wo  | ork                                                    | 26 |  |

|    | 2.1         | SOC I     | DFT                                                    | 26 |  |

|    | 2.2         | Test re   | esource partitioning                                   | 30 |  |

|    |             | 2.2.1     | Test response compaction                               | 31 |  |

|    |             | 2.2.2     | Test data compression                                  | 32 |  |

|    | 2.3         | Conclu    | uding remarks                                          | 35 |  |

| 3  | Volu        | ıme of t  | est data reduction through compression                 | 36 |  |

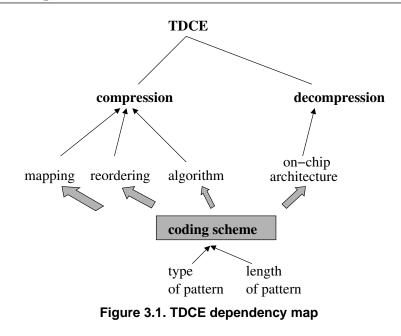

|    | 3.1         | Test da   | ata compression environment                            | 37 |  |

|    |             | 3.1.1     | TDCE characterisation                                  | 37 |  |

|    |             | 3.1.2     | Analysis of previous approaches in TDCE                | 39 |  |

|    | 3.2         | Comp      | ression                                                | 41 |  |

|    |             | 3.2.1     | New Variable-length Input Huffman Coding (VIHC) scheme | 41 |  |

|    |             |           |                                                        |    |  |

# TABLE OF CONTENTS

|   |      | 3.2.2   | Compression algorithm based on VIHC                                       | 46  |

|---|------|---------|---------------------------------------------------------------------------|-----|

|   | 3.3  | Decon   | pression                                                                  | 48  |

|   |      | 3.3.1   | VIHC decoder                                                              | 49  |

|   |      | 3.3.2   | Test application time analysis                                            | 52  |

|   | 3.4  | Experi  | mental results                                                            | 56  |

|   | 3.5  | Conclu  | uding remarks                                                             | 64  |

| 4 | Sync | chronis | ation overhead in test data compression environments                      | 65  |

|   | 4.1  | The in  | portance of synchronisation in TDCE                                       | 66  |

|   |      | 4.1.1   | Synchronisation overhead                                                  | 67  |

|   |      | 4.1.2   | Previous approaches to reduce synchronisation overhead                    | 70  |

|   | 4.2  | Reduc   | ing synchronisation overhead                                              | 73  |

|   |      | 4.2.1   | Tailoring the compressed test set                                         | 74  |

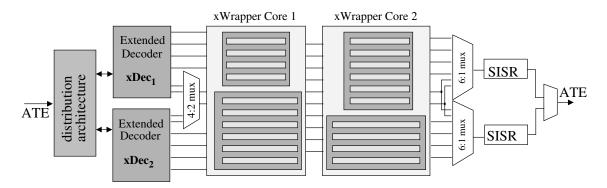

|   |      | 4.2.2   | Distribution architecture for multiple core test                          | 77  |

|   | 4.3  | Experi  | mental results                                                            | 81  |

|   | 4.4  | Conclu  | uding remarks                                                             | 86  |

| 5 | Test | data re | eduction through elimination of useless test data                         | 87  |

|   | 5.1  | Useles  | s memory allocation (UMA)                                                 | 88  |

|   | 5.2  | Core v  | vrapper design, UMA and the ATE                                           | 89  |

|   |      | 5.2.1   | UMA and core wrapper design relationship                                  | 90  |

|   |      | 5.2.2   | UMA and ATE test vector deployment                                        | 94  |

|   | 5.3  | Novel   | test methodology for UMA reduction                                        | 95  |

|   |      | 5.3.1   | Wrapper design algorithm for reducing UMA                                 | 95  |

|   |      | 5.3.2   | Test vector deployment procedure for reduced UMA                          | 99  |

|   | 5.4  | Analys  | sing wrapper scan chain partitioning trade-offs                           | 101 |

|   |      | 5.4.1   | Theoretical analysis                                                      | 101 |

|   |      | 5.4.2   | Volume of test data and test application time trade-offs                  | 103 |

|   | 5.5  | Experi  | mental results                                                            | 105 |

|   |      | 5.5.1   | Core specifications                                                       | 106 |

|   |      | 5.5.2   | Experiment 1: Trade-off between ATE control and mUMA                      | 108 |

|   |      | 5.5.3   | Experiment 2: UMA( $np = 2$ ) vs. conventional ATE                        | 109 |

|   |      | 5.5.4   | Experiment 3: ATE pin-group granularity constrained WSC par-<br>titioning | 112 |

# TABLE OF CONTENTS

|   | 5.6  | Conclu    | uding remarks                                                 | 115 |

|---|------|-----------|---------------------------------------------------------------|-----|

| 6 | Inte | grated    | test solution for core-based System-on-a-Chip                 | 116 |

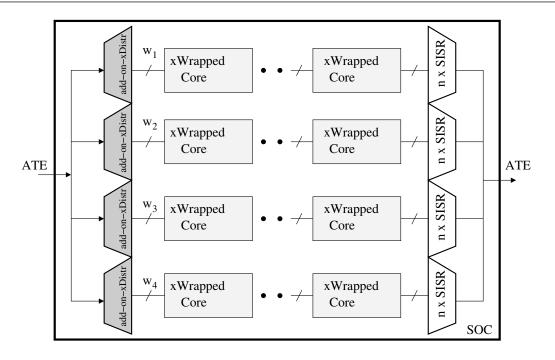

|   | 6.1  | Prelim    | inaries and motivation                                        | 117 |

|   |      | 6.1.1     | Power dissipation during scan                                 | 117 |

|   |      | 6.1.2     | TDC for multiple scan chains cores                            | 118 |

|   |      | 6.1.3     | Exploiting core wrapper design for control overhead reduction | 121 |

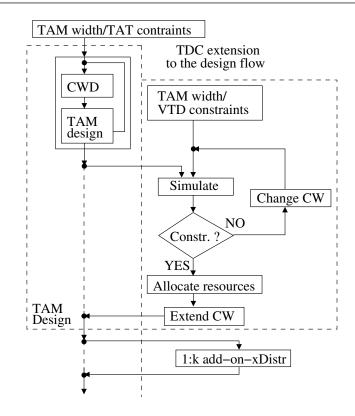

|   | 6.2  | Extend    | led distribution architecture                                 | 124 |

|   |      | 6.2.1     | TAM add-on decompression architecture                         | 129 |

|   |      | 6.2.2     | Design flow integration                                       | 131 |

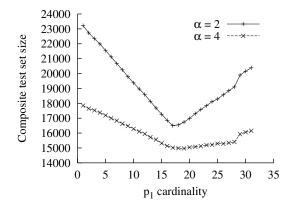

|   | 6.3  | Experi    | mental results                                                | 133 |

|   |      | 6.3.1     | Comparison with single scan chain TDC                         | 133 |

|   |      | 6.3.2     | Comparison with multiple scan chain TDC                       | 139 |

|   | 6.4  | Conclu    | uding remarks                                                 | 145 |

| 7 | Con  | clusion   | s and future research directions                              | 146 |

|   | 7.1  | Future    | research directions                                           | 149 |

| A | Core | e level I | )FT                                                           | 151 |

| B | VIH  | C deco    | der's implementation                                          | 155 |

| С | Dist | ributio   | n architecture's implementation                               | 161 |

| D | Usel | ess mer   | nory and test bus width relationship                          | 165 |

|   | D.1  | Upper     | bound on $w_{max}$                                            | 165 |

|   | D.2  | UMA(      | (np = 2) vs. conventional ATE                                 | 167 |

|   | D.3  | ATE p     | in-group granularity constrainted mUMA                        | 168 |

| E | Exte | ended d   | istribution architecture's implementation                     | 171 |

|   | E.1  | Power     | dissipation during scan                                       | 171 |

|   | E.2  | XOR-      | network based architecture                                    | 173 |

|   | E.3  | Gate le   | evel implementation of add-on-xDistr                          | 178 |

| F | Tool | s and b   | enchmarks                                                     | 182 |

|   | F.1  | Bench     | mark circuits                                                 | 182 |

# TABLE OF CONTENTS

| Re | References 19    |                              |     |  |  |

|----|------------------|------------------------------|-----|--|--|

| G  | G Publications 1 |                              |     |  |  |

|    | F.5              | Integrated SOC test solution | 188 |  |  |

|    | F.4              | Core wrapper design          | 188 |  |  |

|    | F.3              | Synchronisation overhead     | 187 |  |  |

|    | F.2              | Test data compression        | 186 |  |  |

# **List of Figures**

| 1.1  | System-on-a-Chip, an example                             | 2  |

|------|----------------------------------------------------------|----|

| 1.2  | Core based SOC design                                    | 4  |

| 1.3  | Board vs. SOC design                                     | 8  |

| 1.4  | Conceptual architecture for external SOC test            | 10 |

| 1.5  | Conceptual architecture for internal SOC test            | 11 |

| 1.6  | IEEE P1500 wrapped core                                  | 12 |

| 1.7  | Core and core wrapper design                             | 14 |

| 1.8  | SOC with P1500 based cores wrappers                      | 15 |

| 1.9  | SOC with multiple TAMs                                   | 16 |

| 1.10 | ATE – DUT interface                                      | 17 |

| 1.11 | Test and manufacturing cost per transistor               | 18 |

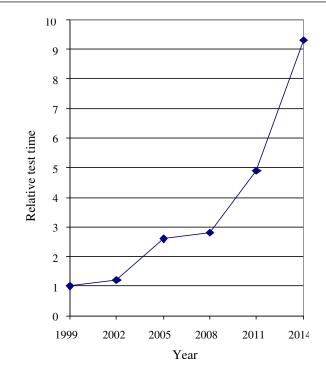

| 1.12 | Test time increase relative to 1999                      | 21 |

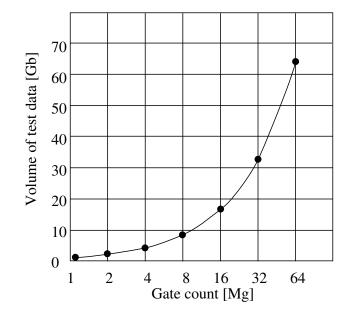

| 1.13 | Gate count vs. volume of test data trend                 | 22 |

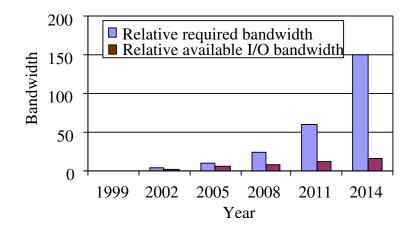

| 1.14 | Growth in complexity and bandwidth relative to 1999      | 23 |

| 2.1  | System-on-a-Chip and test resource partitioning          | 31 |

| 2.2  | Cyclical scan register architecture                      | 35 |

| 3.1  | TDCE dependency map                                      | 38 |

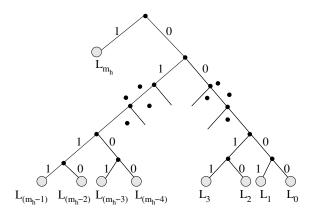

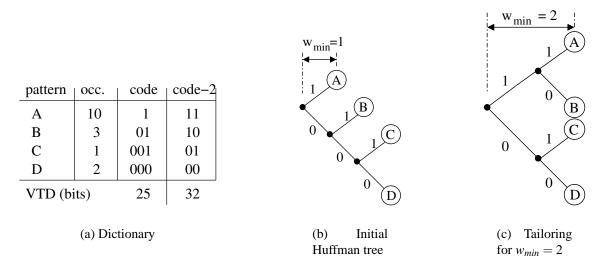

| 3.2  | VIHC for $m_h = 4$                                       | 42 |

| 3.3  | VIHC, the general case                                   | 43 |

| 3.4  | Huffman tree when the Golomb code and the VIHC are equal | 44 |

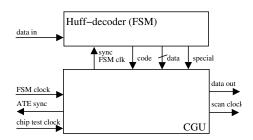

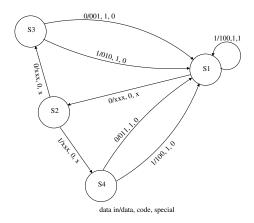

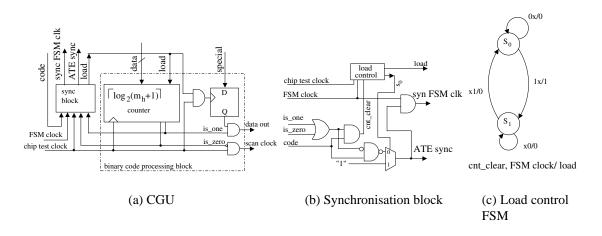

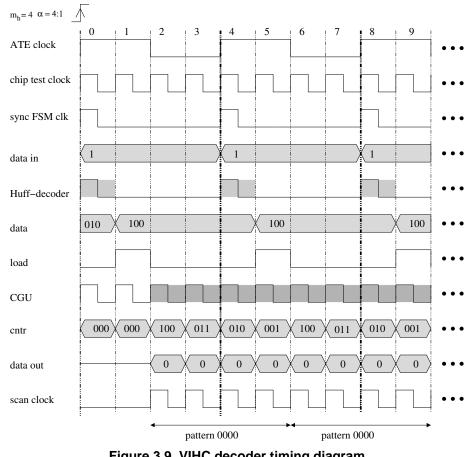

| 3.5  | VIHC generic decompression architecture                  | 49 |

| 3.6  | VIHC decoder                                             | 50 |

| 3.7  | FSM for example in Figure 3.2                            | 51 |

| 3.8  | CGU for VIHC decoder                                     | 51 |

|      |                                                          |    |

# LIST OF FIGURES

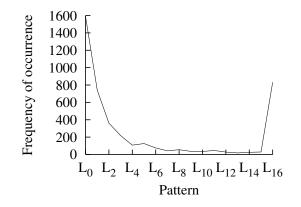

| 3.10       | Pattern distribution for s5378 with $m_h = 16$                    | 55       |

|------------|-------------------------------------------------------------------|----------|

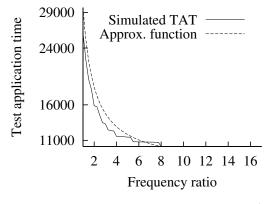

| 3.11       | TAT for s5378 with $m_h = 16$                                     | 56       |

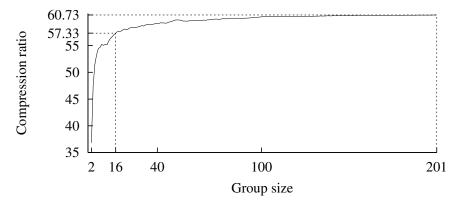

| 3.12       | Compression ratio vs. group size for s5378 with $T_{diff}$        | 58       |

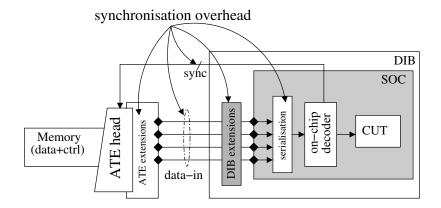

| 4.1        | Test data compression environment with synchronisation overhead   | 66       |

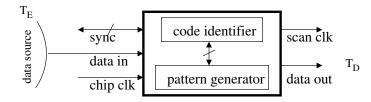

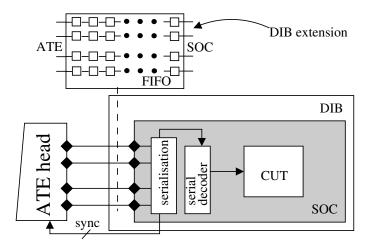

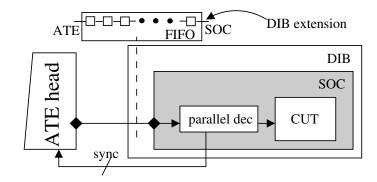

| 4.2        | Generic on-chip decoder                                           | 67       |

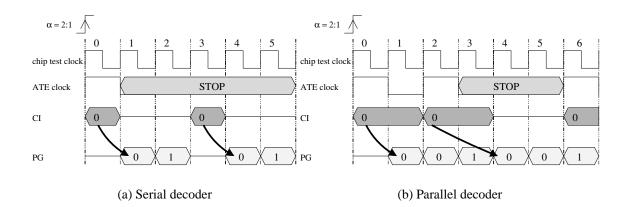

| 4.3        | Serial decoder's synchronisation overhead                         | 68       |

| 4.4        | Parallel decoder's synchronisation overhead                       | 69       |

| 4.5        | The stopping of the ATE data stream                               | 70       |

| 4.6        | Tailoring the compression method                                  | 71       |

| 4.7        | Interleaving architecture                                         | 73       |

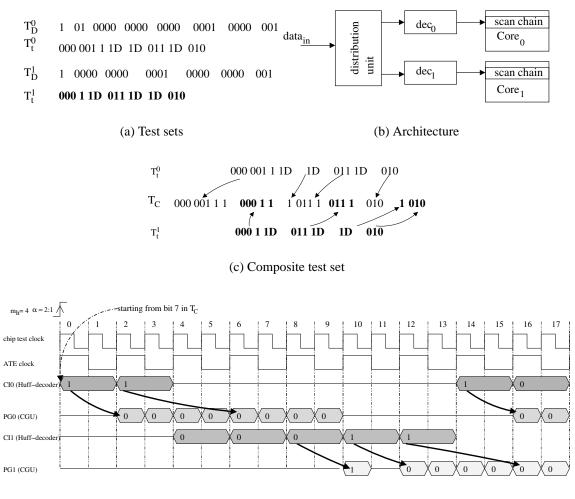

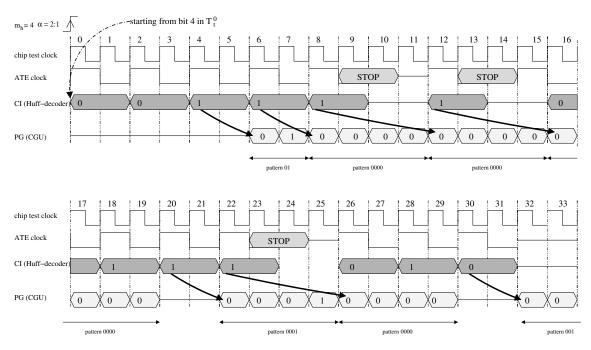

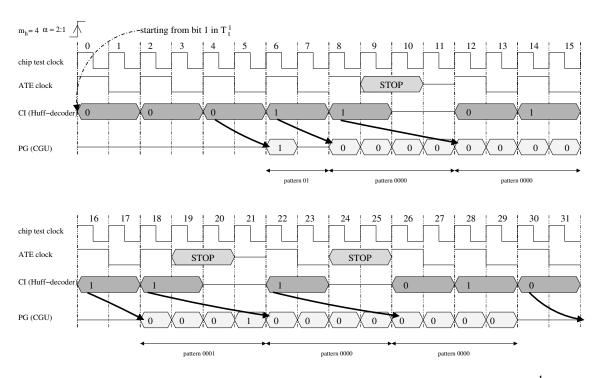

| 4.8        | VIHC - an example                                                 | 73<br>74 |

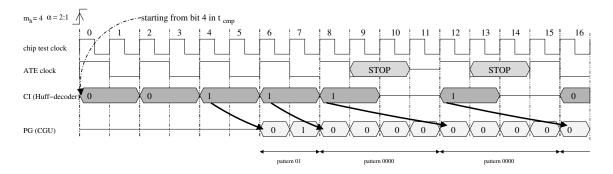

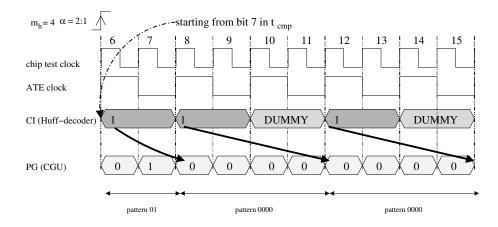

| 4.9        | Timing diagram to illustrate the stopping of the data stream      | 75       |

| 4.10       | Timing diagram to illustrate tailoring of the compressed test set | 75<br>76 |

|            |                                                                   |          |

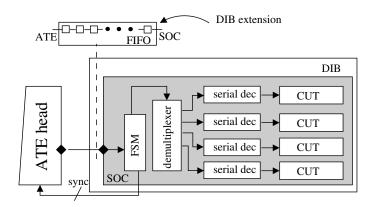

|            | Distribution architecture for two core test                       | 78       |

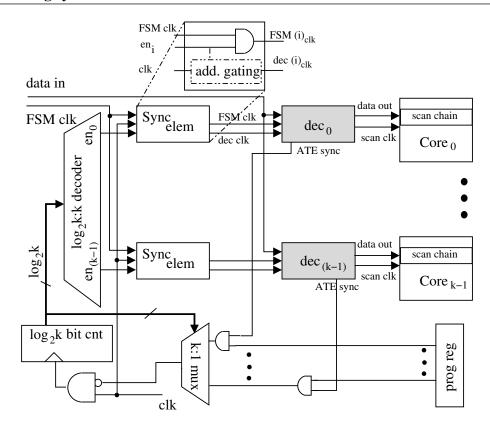

| 4.12       | Distribution architecture for multiple core test                  | 80       |

| 5.1        | Useless memory allocation                                         | 88       |

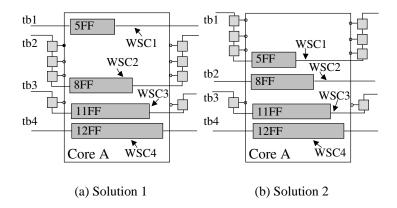

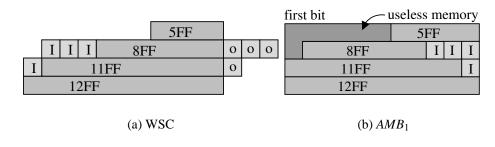

| 5.2        | Alternative core wrapper design solutions with equal TAT          | 91       |

| 5.3        | WSC and ATE memory bitmap for Solution 1                          | 92       |

| 5.4        | WSC and ATE memory bitmap for Solution 2                          | 92       |

| 5.5        | WSC and memory bitmap when $wsc^i < wsc^o$                        | 93       |

| 5.6        | WSC and memory bitmap when $wsc^i = wsc^o$                        | 93       |

| 5.7        | ATE test vector deployment information                            | 94       |

| 5.8        | Trade-off between test application time and memory requirements   | 103      |

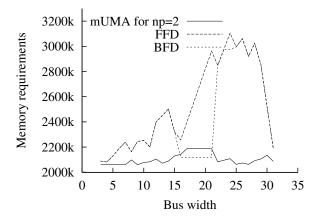

| 5.9        | Memory requirements reduction for ISCAS89                         | 111      |

| 5.10       | Memory requirements reduction for ITC02                           | 113      |

| 5.11       | ATE pin-group granularity and WSC partitioning                    | 114      |

| <b>c</b> 1 |                                                                   | 110      |

| 6.1        | Extending single scan chain approaches to MSC test                |          |

| 6.2        | Extending FDR to MSC test                                         |          |

| 6.3        | MSC test with SmartBIST                                           |          |

| 6.4        | Low-cost core based SOC test                                      |          |

| 6.5        | Core wrapper characterisation                                     | 122      |

# LIST OF FIGURES

| 6.6         | Single scan chain TDC                                                                    | 123 |

|-------------|------------------------------------------------------------------------------------------|-----|

| 6.7         | Extended distribution architecture (xDistr)                                              | 125 |

| 6.8         | Extended decoder unit (xDec)                                                             | 126 |

| 6.9         | Composite test construction for <i>xDistr</i>                                            | 129 |

| 6.10        | TAM add-on decompression architecture (add-on-xDistr)                                    | 130 |

| 6.11        | Conceptual architecture for SOC test                                                     | 131 |

| 6.12        | Design flow integration                                                                  | 132 |

| 6.13        | Composite test set size vs. $p_1$ cardinality                                            | 134 |

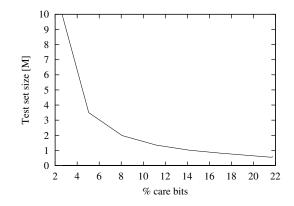

| 6.14        | Test set size decrease with increase of $\% cb$                                          | 140 |

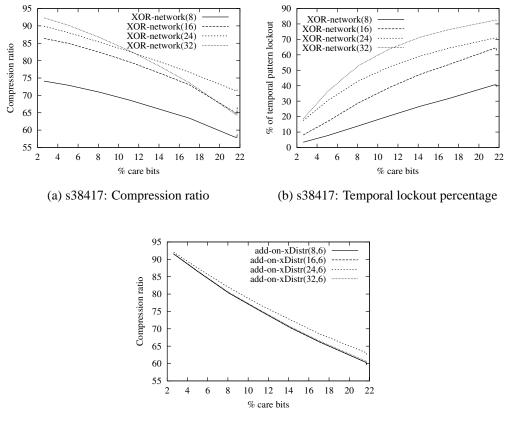

| 6.15        | Compression ratio and temporal pattern lockout                                           | 142 |

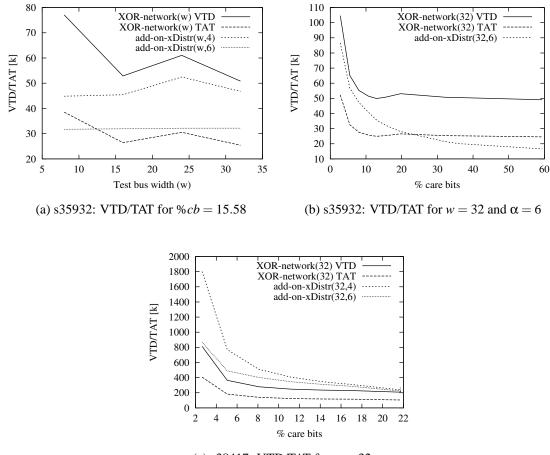

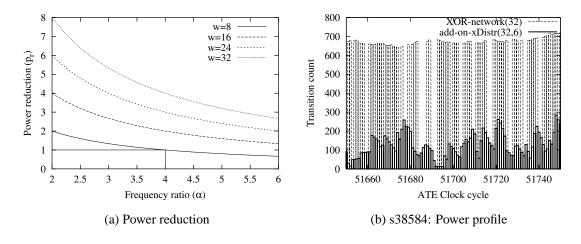

| 6.16        | Volume of test data and test application time                                            | 143 |

| 6.17        | Power dissipation                                                                        | 145 |

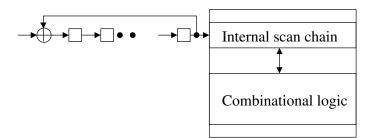

| A.1         | Scan based DFT                                                                           | 152 |

| A.1<br>A.2  | Core with MSC                                                                            |     |

| A.2<br>A.3  | Core with BIST                                                                           |     |

| A.J         |                                                                                          | 134 |

| <b>B</b> .1 | VIHC decoder                                                                             | 156 |

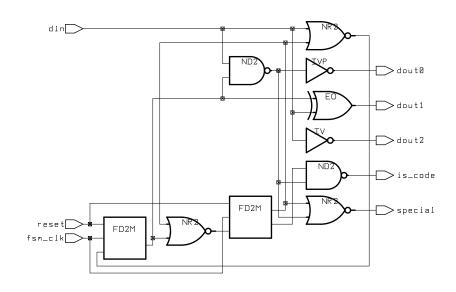

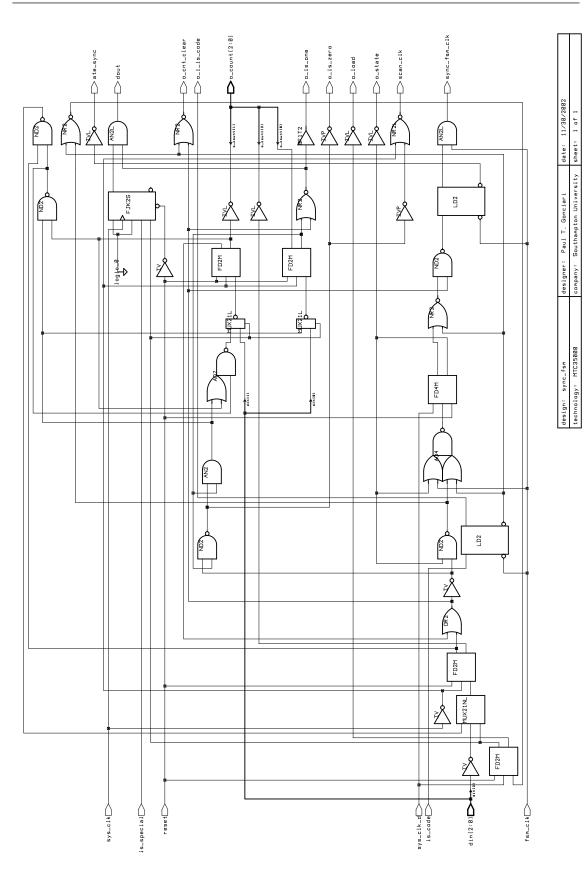

| B.2         | Huff-decoder                                                                             | 157 |

| B.3         | Control and generation unit (CGU)                                                        | 158 |

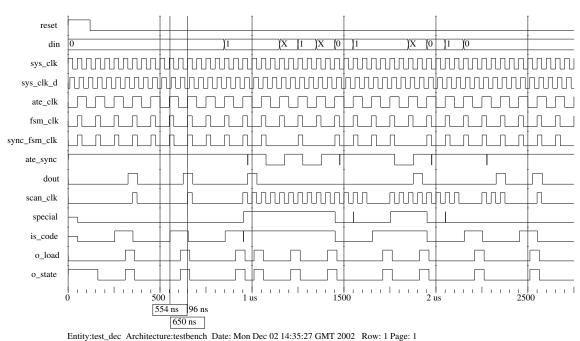

| B.4         | Gate level timing diagram for the example given in Figure 3.2(d)                         | 159 |

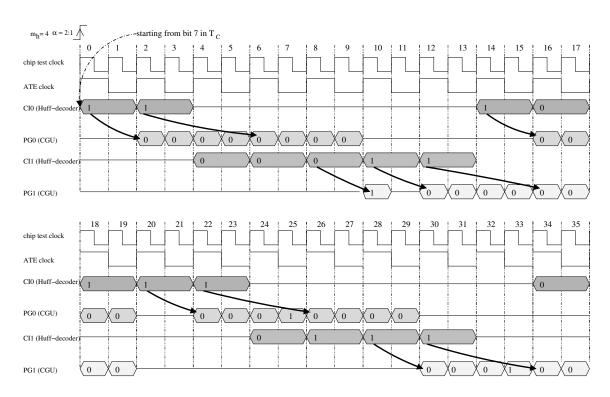

| C.1         | Timing diagram to illustrate the stopping of the data stream for $t^0$                   | 161 |

| C.2         | Timing diagram to illustrate the stopping of the data stream for $t^1$                   |     |

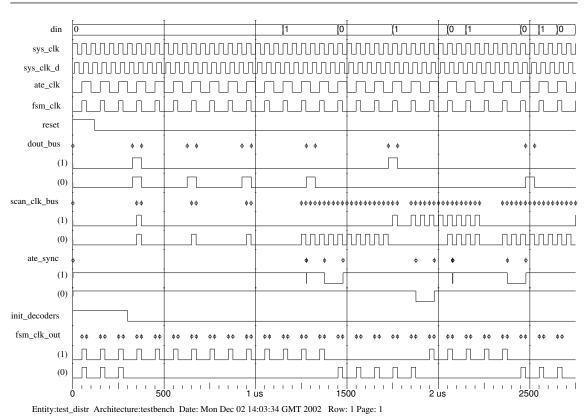

| C.3         | Timing diagram to illustrate the distribution architecture and $T_C$                     |     |

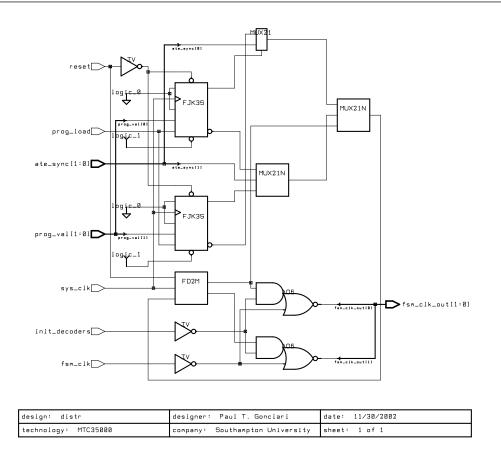

| C.4         | The distribution unit                                                                    |     |

| C.5         | Gate level timing diagram for the example given in Figure 4.11(d)                        | 164 |

|             |                                                                                          |     |

| D.1         | Example of unequal scan chains                                                           | 166 |

| D.2         | Comparison between FFD, BFD and mUMA with $np = 2$ for core Module26 of SOC p22810       | 168 |

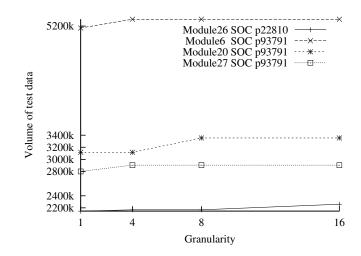

| D.3         | Volume of test data variation with granularity for $w = 32$ for ITC02 benchmark circuits | 170 |

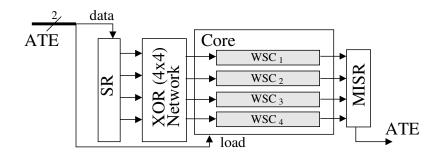

| E.1         | XOR-network based architecture                                                           | 174 |

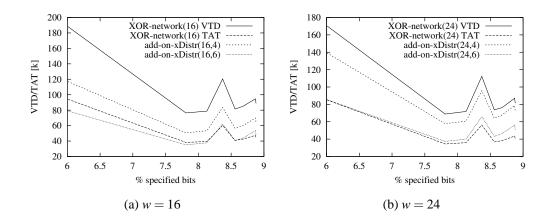

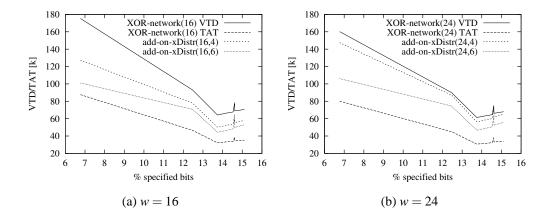

| E.2         | VTD and TAT for s13207                                                                   | 176 |

# LIST OF FIGURES

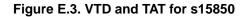

| E.3 | VTD and TAT for s15850                                                                               |

|-----|------------------------------------------------------------------------------------------------------|

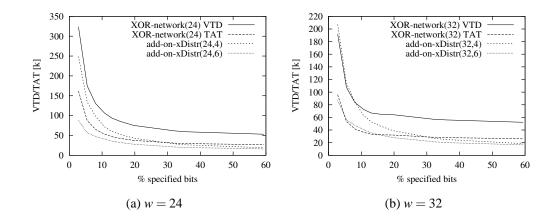

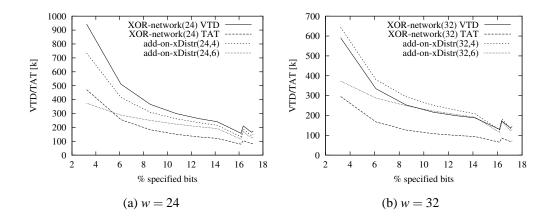

| E.4 | VTD and TAT for s35932                                                                               |

| E.5 | VTD and TAT for s38584                                                                               |

| E.6 | The extended decoder (xDec)                                                                          |

| E.7 | The extended distribution architecture (add-on-xDistr)                                               |

| E.8 | Gate level timing diagram for programming the add-on-xDistr for the ex-<br>ample given in Figure 6.9 |

| E.9 | Gate level timing diagram for the example given in Figure 6.9 181                                    |

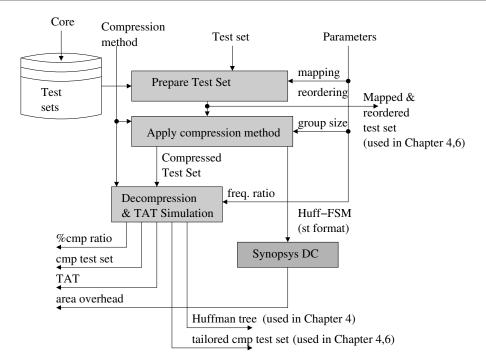

| F.1 | Tool flow for test data compression                                                                  |

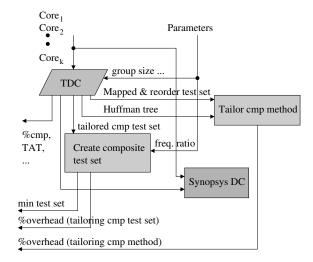

| F.2 | Tool flow for computing synchronisation overhead                                                     |

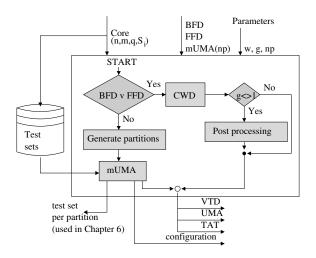

| F.3 | Tool flow for determining UMA                                                                        |

| F.4 | Tools flow for integrated SOC test solution                                                          |

# **List of Tables**

| 3.1               | Core user/vendor information exchange                                                                                                                                |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.2               | VIHC for $T_{diff}$                                                                                                                                                  |

| 3.3               | VIHC for $T_D$                                                                                                                                                       |

| 3.4               | Best compression ratio comparison for $T_{diff}$                                                                                                                     |

| 3.5               | Best compression ratio comparison for $T_D$                                                                                                                          |

| 3.6               | Comparison between SC and VIHC                                                                                                                                       |

| 3.7               | Comparison between Golomb and VIHC                                                                                                                                   |

| 3.8               | Area overhead comparison for s5378                                                                                                                                   |

| 3.9               | TAT comparison         62                                                                                                                                            |

| 3.10              | TAT reduction obtained with VIHC over previous methods 63                                                                                                            |

| 3.11              | Previous approaches compared to VIHC                                                                                                                                 |

| 4.1<br>4.2<br>4.3 | Tailoring compression method vs. tailoring compressed test set                                                                                                       |

| 4.3               | Comparison for 52                                                                                                                                                    |

| 5.1               | Core specification for ISCAS89 benchmarks                                                                                                                            |

| 5.2               | Core specification for ITC02 benchmarks                                                                                                                              |

| 5.3               | mUMA for $w_{max}$ with ISCAS89 benchmark circuits                                                                                                                   |

| 5.4               | mUMA for $w_{max}$ with ITC02 benchmark circuits $\dots \dots \dots$ |

| 5.5               | Memory requirements comparison for ISCAS89                                                                                                                           |

| 5.6               | Memory requirements comparison for ITC02 112                                                                                                                         |

| 6.1               | Core specification                                                                                                                                                   |

| 6.2               | xDistr composite test set                                                                                                                                            |

| 6.3               | Volume of test data comparison                                                                                                                                       |

| 6.4               | add-on-xDistr for TAM of widths 24 and 32                                                                                                                            |

| 6.5 | Core specification                                                                     | 139 |

|-----|----------------------------------------------------------------------------------------|-----|

| D.1 | ATE pin-group granularity constrained WSC partitioning for ISACS89 benchmarks circuits | 169 |

| D.2 | ATE pin-group granularity constrained WSC partitioning for ITC02 benchmarks circuits   | 169 |

| F.1 | Core specification for ISCAS89 benchmarks                                              | 183 |

| F.2 | Core specification for ITC02 benchmarks                                                | 183 |

# **List of Abbreviations**

| ATE  | Automatic Test Equipment                 |

|------|------------------------------------------|

| ATPG | Automatic Test Pattern Generation        |

| BIST | Built-In Self-Test                       |

| CI   | Code Identifier                          |

| CMOS | Complementary Metal Oxide Silicon        |

| CTL  | Core Test Language                       |

| CUT  | Core Under Test                          |

| CWD  | Core Wrapper Design                      |

| DFT  | Design for Test                          |

| DIB  | Device Interface Board                   |

| DRAM | Dynamic Random Access Memory             |

| DUT  | Device Under Test                        |

| EDA  | Electronic Design Automation             |

| FDR  | Frequency Directed Run-length            |

| FF   | Flip Flop                                |

| HDL  | Hardware Description Language            |

| IC   | Integrated Circuit                       |

| IP   | Intellectual property                    |

| ITRS | International Roadmap for Semiconductors |

| MSC  | Multiple Scan Chains                     |

| PCB  | Printed Circuit Board                    |

| PG   | Pattern Generator                        |

# LIST OF ABBREVIATIONS

| RAM  | Random Access Memory                 |

|------|--------------------------------------|

| RISC | Reduced Instruction Set Computer     |

| RPCT | Reduce Pin Count Test                |

| SC   | Selective Coding                     |

| SECT | Standard for Embedded Core Test      |

| SFF  | Scan Flip Flop                       |

| SOC  | System-on-a-Chip                     |

| SSC  | Single Scan Chain                    |

| TAM  | Test Access Mechanism                |

| TAT  | Test Application Time                |

| TDC  | Test Data Compression                |

| TDCE | Test Data Compression Environment    |

| UDL  | User Defined Logic                   |

| UMA  | Useless Memory Allocation            |

| VIHC | Variable-length Input Huffman Coding |

| VTD  | Volume of Test Data                  |

| WSC  | Wrapper Scan Chain                   |

# Chapter 1

# Introduction

Driven by the high level of integration the industry is capable of building an entire system into a single chip [1, 2, 3, 4]. Systems-on-a-chip (SOC) are composed from *embedded cores*, which make it easier to import existing technologies and shorten the time-to-market through design reuse [1]. The new market driven by the SOC revolution comprises *core vendors* as providers, and *core users* as customers. While the core vendor has full knowledge about the core's functionality and its internal structure, the core user is often knowledgeable only about the core's functionality. Therefore, besides the immediate advantages of core based SOCs, the SOC paradigm brings forth new problems from the design and test perspective [5, 1, 6, 2], which require new test strategies for testing the core itself as well as the entire system [7, 8, 9, 10, 11, 12].

Due to the continuous increase in chip complexity and transistor density, the cost of testing the chips will approach and even exceed the cost of manufacturing them [13]. Therefore, if the cost of test is not lowered, testing will have a negative impact on the cost of the design [14, 9, 15, 13] leading to an increase in the overall production cost of the chip. Addressing the cost of test problem in a core based SOC environment requires solutions which refrain from changing the cores. This is of great importance since if core redesign is required, then the very purpose of core based SOC, short time-to-market through core reuse, can be defeated. Considering this constraint imposes the usage of basic knowledge about the cores when addressing the cost of test problem. Therefore, the topic of this dissertation is to provide methods which contribute toward reduced cost of test providing *low-cost system-on-a-chip test* solutions assuming only basic knowledge about the cores, and hence leveraging the core based SOC environment.

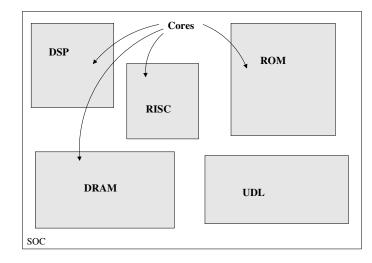

Figure 1.1. System-on-a-Chip, an example

This chapter is organised as follows. In Section 1.1 the differences between the traditional printed circuit board (PCB) and the new SOC design flows are illustrated, emphasising the implications on testing SOCs. Section 1.2, illustrates the SOC DFT challenges, and Section 1.3 investigates the main factors which drive the continuous increase in test cost, motivating the work of this thesis. Finally, Section 1.4 outlines the main contributions of this work and presents the organisation of the thesis.

# 1.1 Core based System-on-a-Chip design

To understand why testing in the new core based SOC paradigm becomes such a major problem, and why it is important to address it without imposing changes to the cores, one must understand the differences between the SOC and the traditional PCB design flows and how these differences influence the testing of the entire system. Therefore, in this section a generic integrated circuit (IC) design flow is described, and the various types of cores and their influences on the design flow are illustrated.

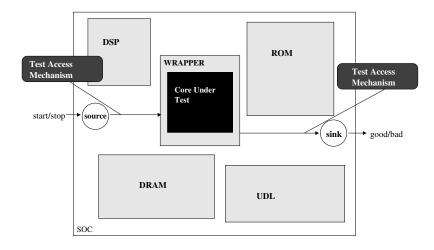

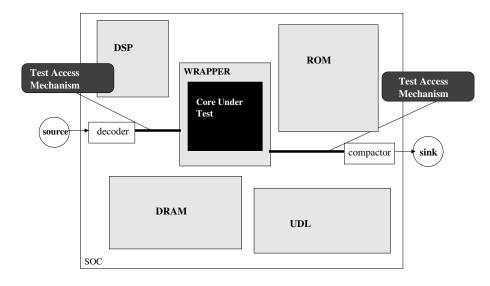

There are two main types of components is SOCs: the cores and the user defined logic (UDL). This is exemplified in Figure 1.1 where the cores (which in the figure are represented by memories (DRAM, ROM) and the RISC and DSP processors) and UDL are illustrated considering a fictive system. A *core* is a pre-designed, pre-verified silicon circuit block, usually containing at least 5,000 gates, that can be used in building a larger or more complex application on a semiconductor chip [1]. Similar to ICs on a

PCB, cores can perform a wide range of functions (e.g., digital signal processors, RISC processors, or DRAMs) and can be found in a number of technologies (e.g., complementary metal-oxide-silicon (CMOS) logic, DRAM and analog circuits). Furthermore, the more complex cores come in hierarchical compositions (i.e., complex cores comprise a number of simple cores). Often these cores are products of technology, software, and know-how that are subject to patents and copyrights. Hence, a core block represents intellectual property (IP) that the core builder licenses to the core user [1]. Therefore, the core user is not always entitled to do changes to the core and is forced to reuse it "as is" (as a black box), being knowledgeable only about the core's functionality, however, not about the implementation details. In addition, while ICs are delivered to the customer in a *manufactured and tested* form, cores are delivered in a range of hardware description levels (soft, firm, and hard). These two fundamental differences will influence not only the design of the SOCs (as shown in Section 1.1.2) but also the testing of the SOCs (as shown in Section 1.2).

*UDL* is added by the system integrator to the SOC to customise or to interface the different cores such that the desired functionality is obtained. While the cores are IPs delivered by third party vendors and are reused within the design, the UDL is custom logic specific to the SOC under development. Hence, the system integrator has full knowledge about its functionality and its implementation details. The UDL is a required investment from the design point of view, however, testing the UDL gives way to new issues in system test [16, 17, 18].

### **1.1.1 Design flow**

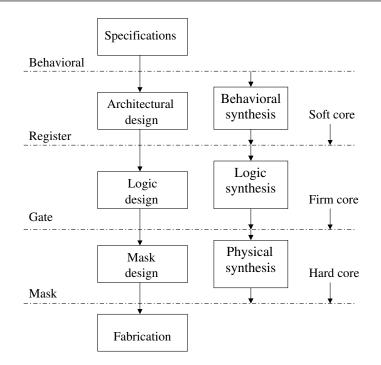

In this section a generic IC design flow is illustrated. Starting from the initial requirements definitions, i.e., the specifications of the desired chip functionality described in a formal form, the design follows a number of phases which transform these specifications into the final chip in a chosen technology. This is illustrated with the left hand side of the generic core based SOC design flow in Figure 1.2. The term technology (or fabrication technology) refers to the semiconductor process used to produce the final chip, i.e., it denotes the type of semiconductor (e.g., silicon), the type of transistor (e.g., CMOS) or the details of a certain transistor technology (e.g., 0.18 micron CMOS) [19]. Each design phase corresponds to a level of abstraction, i.e., the level of dependence on the fabrication

Figure 1.2. Core based SOC design

technology. There are four levels of abstraction: behavioural level, where the specifications are described using generic methods, no structural constraints are considered (e.g., a variable is of type integer; a conditional assignment is represented by an IF statement); register transfer level (RTL), where generic functions and variables are replaced by structural blocks (e.g., the variable is replaced by a register of a given size; an IF statement is represented by a multiplexer, the arithmetic operations are replaced with arithmetic logic units (ALUs)); gate level, where the structural components are mapped to netlists - interconnection of building cells, gates - in a specific cell library (e.g., a 2 : 1 multiplexer is represented by two AND gates and an OR gate); and mask level (or physical level), where each cell is represented by the layout of the transistor model counterpart. The specifications of the desired chip functionality are described at the various levels of abstraction using hardware description languages (HDL). For example, at the behavioural level of abstraction, the HDL can be VHDL [20, 21, 22, 23], Verilog [24], C and C++ [25, 26], and SystemC [27, 28, 29]; at the RTL level of abstraction, the HDL is usually VHDL and Verilog. From the initial specifications to the final chip, the design goes through a number of translation and verification steps. The translation of the descriptions from one level of abstraction into the other is referred to as *synthesis*. Verification is used to check whether the design in the current level of abstraction is correct, conforming with the specifications. Both steps are performed using computer aided design (CAD) tools [30].

**Synthesis** A synthesis process aims at finding the best equivalent representation in the next level of abstraction which guarantees the same functionality as the design in the current level of abstraction considering the constraints given by the designer (e.g., the area occupied by silicon should not exceed 300 sq-mils; the design should work for frequencies up to 100 MHz). Corresponding to the above four levels of abstractions, there are three synthesis steps: behavioural synthesis, logic synthesis and physical synthesis. These transform the initial specifications from behavioural to RTL, then from RTL to gate level, and finally from gate level to layout.

**Verification** Verification in hardware design mainly consists of validation and formal verification. Validation, verifies the design through simulation and testing. Formal verification, on the other hand, uses rigorous mathematical reasoning to show that a design meets all or parts of its specification [31, 32]. However, it does not necessarily guarantee correct operation with respect to timing, power, noise and routability [33]. At the different levels of abstraction, validation and formal verification take different shapes. For example, they are represented by property checking [31, 34] or RTL/cycle simulation [32] at the RTL level; and equivalence checking and physical verification at the gate and layout (or mask) level [35]. The verified design at mask level will then go through manufacturing.

**Manufacturing** The manufacturing of an IC implies wafer fabrication and packaging. Wafer fabrication involves printing of geometric shapes corresponding to the layout onto wafer layers [19]. As each wafer contains a number of chips, the wafer is cut and then packaged. Each of the above processes involved in wafer fabrication can introduce defects into the chip. For example, particles (material which is not removed in the areas exposed by the masking process) may cause bridges between two or more lines; incorrect spacing between connections may cause circuit shorts; holes (exposed areas that is unexpectedly etched) may lead to open interconnects. These manufacturing defects (or physical faults) affect the functionality of the circuit and hence lead to faulty chips. To avoid shipping bad chips to customers, and at the same time correct the manufacturing process which caused the defects, hence improving yield, testing of the manufactured circuit is required.

**Testing** After wafer manufacturing, testing is also referred to as manufacturing test. The wafer is first subjected to wafer sort, where most of the faulty chips are identified, and then

the packaged chips are further tested in order to eliminate the defects which escaped wafer sort (due to electrical limitations), and in order to accelerate infant mortality through burnin (which is a high-voltage, high-temperature stress of the device) [36, 37, 38]. Finally, the device is tested for conformance with the specifications. Because of the high complexity of the chips, testing is done using automated test equipment (ATE). The ATE is a precision measurement tool which provides the environment required to test the chip. There are two main types of testing: functional test and structural test. The former checks for the correct functionality of the manufactured chip. The latter, verifies that the chip was manufactured correctly [38]. If not specified differently, the term testing and manufacturing test will refer to structural testing as introduced above. Testing implies applying test stimuli (or test vectors), and inspecting the circuit responses (or test responses). If the circuit response is not correct then a defect was identified. While during verification, at the previous levels of abstraction, access to the entire model was available, during manufacturing test, the access to the chip's internals is limited by the inputs and outputs of the circuit. To increase the access to the chip internals and increase the effectiveness of testing, design for testability (DFT) has been introduced as a mandatory step in the design process [36, 38]. While DFT features are embedded in various design stages of the IC (e.g., at the RTL or the gate level of abstraction [39, 40, 41]), they are exploited after the manufacturing of the wafer and the packaging of the chip. In order to ensure the effectiveness of DFT, the manufacturing test problem has to be modelled at the higher levels of abstraction. Therefore, faults models were developed corresponding to the physical defects [36, 37, 38]. Based on the fault models, the problem of identifying a defect is equivalent to finding the circuit's input values (test stimuli) which will provoke a faulty and fault free output (test responses) depending on the existence of the fault. This process is performed by automatic test pattern generation (ATPG) [42, 43, 44] tools. ATPG tools can determine a list of faults, the test vectors which detect the faults, and the corresponding fault free responses. In addition, using fault simulation ATPG tools can estimate the fault coverage (how many from the total modelled faults can be detected), and they can also be used for fault diagnosis (which was the root cause of the defect). The test vectors generated by ATPG can be completely specified (e.g., "1100") or incompletely specified (e.g., "1x0x") in which case they are referred to as test cubes. For the different types of defects various fault models have been proposed (e.g., bridging fault models, open fault models, delay fault models, stuck-at fault models [36, 45, 37, 38, 46]). For example, the stuck-at fault model assumes that a given node has always a fixed value, either logic 0 or logic 1, i.e., the

node is assumed to be either connected to the power line (stuck-at-1 fault) or connected to the ground line (stuck-at-0 fault).

### **1.1.2** Core based design

The hardware description levels in which core providers deliver their cores can be related to the levels of abstractions described in the previous subsection. Hence,

- soft cores consists of a synthesisable representation that can be re-targeted for different technologies and system constraints. As a HDL description (behavioural or RTL), these cores leave much of the implementation to the designer, however they are flexible and process-independent;

- *firm* cores usually consist of gate-level netlist representation ready for place and route. They give some flexibility to the designer, are accompanied by simulation models and fit into standard HDL design methodologies;

- *hard* cores include timing information and technology dependent layout, i.e., physical level description of the core. While they are optimised for predictable area and performance, they lack flexibility.

The three types of cores offer various trade-off opportunities, each of them having different modelling and test requirements [1], affecting the design at the corresponding level of abstraction. This is illustrated on the right hand side of Figure 1.2 (see Page 4), where the entrance of the different types of cores in the design flow is shown. Core based integration within the design flow is possible if electronic design automation (EDA) companies provide tools which are capable of embedding cores at their corresponding level of abstraction, considering not only their functionalities but also their DFT features [1]. As mentioned in the beginning of Section 1.1, there are two factors which fundamentally differentiate PCB design and core based SOC design: the IP factor and the manufacturing factor. The former will forbid the core user to do any changes to the core. This will impact the design cycle of the SOC, since the changes have to be done by the IP/core vendor [1], and the testing of the design, as the system integrator is forced to use the DFT embedded with the IP even if this does not suit the DFT methodologies adopted for the rest of the SOC. The latter will mainly influence the testing of the SOC as illustrated in the following section.

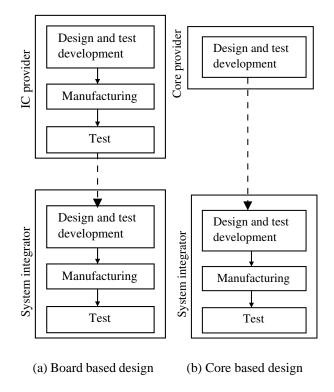

Figure 1.3. Board vs. SOC design [2]

# **1.2** Core based System-on-a-Chip test

Due to the high complexity of SOCs two main problems are identified with respect to test. Firstly, the test infrastructure for the SOCs, and secondly, the cost of test, which if current trends continue will have a negative impact on the total production cost of the chip. The former is illustrated in this section, while the latter is detailed in Section 1.3.

To illustrate the challenges in testing SOCs, firstly the difference between the PCB and SOC design flows is analysed. The two design flows are shown from the system integrator's perspective, illustrating only a high level view of the two design processes, in Figure 1.3. In the traditional PCB design (see Figure 1.3(a)) each IC has been designed and developed, manufactured and tested for manufacturing faults. The system integrator had merely to put the system together and test for interconnect faults between the ICs on the PCB. In the core base SOC design (see Figure 1.3(b)) the cores are only designed and developed, the manufacturing and testing of the cores is the job of the system integrator. The system integrator in this case has to manufacture the SOC (and not assemble the system as in PCB like systems), test each core for manufacturing faults, test the interconnects and the entire system. Hence, even though conceptually the difference between the two

designs is small, the issues in testing core based designs differ considerably from testing PCBs. The problems related to core based SOC test [2] are detailed next.

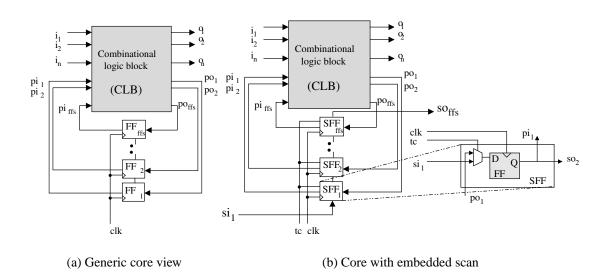

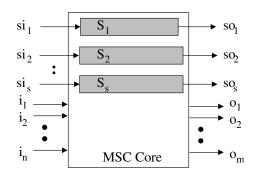

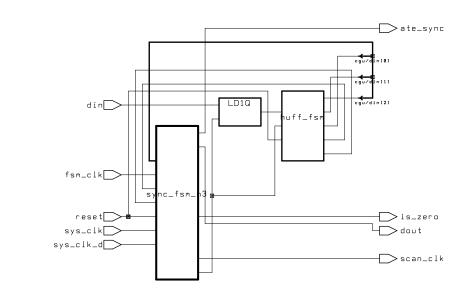

**Core level test** deals with the testing of the core itself. Since the system integrator is usually forced to deal with the core as a black box, the core vendor has to provide the model, the DFT (e.g., scan based DFT or built-in self test (BIST) based DFT<sup>1</sup>) [36, 47, 38] structures and the corresponding test vectors.

**Test access** provides the electronic test infrastructure for accessing the cores. This is required since contrary to PCBs where the ICs primary inputs and outputs were accessible, and thus during test direct physical access to the IC is available, in SOCs the cores are embedded within the chip and thus, no access to the cores terminals is available. In addition to providing the means to access the cores, the test access needs to isolate the core under test (CUT) from its surroundings, facilitating inter-core test [48]. Furthermore, test scheduling is also required to run intra-core and inter-core tests such that initialisation and final content of the individual cores is not affected.

**System level test** addresses the test of the entire system. Compared to conventional PCB test, system level test is far more complex. The system chip test comprises: tests for the individual core, tests for the UDL and tests for interconnect logic and wiring. This composite system level test requires adequate test scheduling which must meet several chip-level constraints, such as, test application time (TAT), area overhead, and power dissipation [49].

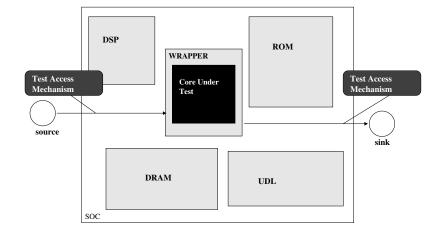

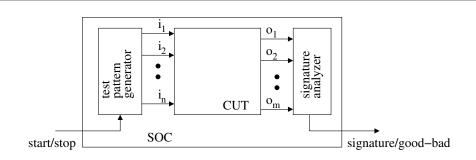

Driven by the above challenges two conceptual architectures for SOC test have been proposed [2], illustrated in Figures 1.4 and 1.5. Characteristic to both architectures are the *source and sink*, the *test access mechanism* and the *core test wrapper*, described next:

• the *source and sink* are responsible for providing the test stimuli and analysing the test responses. Depending on the location of the source and the sink, an external-only (Figure 1.4) or internal-only (Figure 1.5) solution has been envisioned. The former is referred to as external deterministic test where the source and the sink are represented by the automatic test equipment (ATE), detailed in Section 1.2.2. For the

<sup>&</sup>lt;sup>1</sup>For scan based and BIST based DFT the reader is referred to Appendix A

Figure 1.4. Conceptual architecture for external SOC test [2]

latter the internal source and sink are represented by BIST structures. The test in this case is initiated by an off-chip test equipment, which also receives the result of the test;

- *test access mechanism (TAM)* provides the mechanism to transport the test stimuli from the source to the CUT, and the test responses from the CUT to the sink. In general, having a wide TAM will reduce the test application time, however, it will also increase the wiring overhead. Hence, designing a TAM involves making trade-offs between the bandwidth and the test application cost. In addition, the type of test architecture (internal-only or external-only) must also be consider, since, when the external test is performed, the TAM width should not exceed the number of ATE I/O channels (see Section 1.2.2);

- core test wrapper provides an interface between the embedded core and its environment. The core test wrapper connects the core terminals to the rest of the chip and to the TAM. A core test wrapper, must support the following mandatory modes [49, 50, 51]: Normal operation: when the core test wrapper is transparent and the core is connected to the chip environment; Core-internal test: when the core test wrapper connects the TAM to the core such that the test patterns can be applied, and the test responses observed; Core-external test: when testing of the interconnect logic and wiring is allowed by the core test wrapper.

With respect to DFT, the above can be divided into *core level DFT*, which includes scan based and BIST based DFT; and *system level DFT*, which provides the SOC test

Figure 1.5. Conceptual architecture for internal SOC test [2]

infrastructures, i.e., the core test wrapper and the TAM. System level DFT comprising the core test wrapper design and TAM design are illustrated next.

## **1.2.1** System level DFT

It should be noted that the core wrapper design can be performed by both the core vendor and the system integrator. If not specified differently, it is considered in this dissertation that core wrapper design is the responsibility of the system integrator. This is motivated by the flexibility obtained in this case as detailed in the next section.

### Core test wrapper design

It has been illustrated in the previous section that the core test wrapper provides an interface between the embedded core and its environment. Because the core user rarely participates in a core's architectural and functional development, the core appears as a black box with known functionality and I/Os [11]. To integrate the core into a design and to exploit the DFT features of the core, the core test access interface and the core test knowledge must be available to the core user. To provide a common basis for core test knowledge exchange and core test access design, the emerging IEEE P1500 [52] working group is focusing on standardising: *Core Test Language* (CTL), capable of representing all test related information [53, 50, 51, 54], and a scalable and configurable *core test wrapper* to allow easy test access to the core in a SOC [49, 53, 51].

Figure 1.6. IEEE P1500 wrapped core [55]

The IEEE P1500 standard for embedded core test (SECT) does not cover the core's internal test methods or DFT, nor SOC test integration and optimisation. These are completely in the hands of the core provider or the core user respectively, and not suited for standardisation due to the fact that their requirements differ for different cores and SOCs [49, 53, 51]. Hence, in the emerging P1500 standard [52], it is assumed that the core provider performs DFT (scan design, BIST) [36, 47, 38] and supplies all the information required for the proper test of the core [49, 53, 51]. Currently the IEEE P1500 SECT is focusing on "non-merged"<sup>2</sup> digital logic and memory elements. In order to provide the flexibility required to test various types of cores, the IEEE P1500 SECT allows "two levels of compliance". (i) IEEE 1500 Unwrapped Core, this level will allow the core to be delivered without a complete IEEE 1500 wrapper however, it does have the IEEE 1500 CTL program. Using this program, the core user can develop its own IEEE 1500 wrapper. In this scenario, the CTL will describe the core test knowledge at the bare core terminals. (ii) IEEE 1500 Wrapped Core, this level requires the complete IEEE 1500 wrapper and the IEEE 1500 CTL to be delivered with the core. In this scenario, the CTL describes the core test knowledge including how to operate the core wrapper.

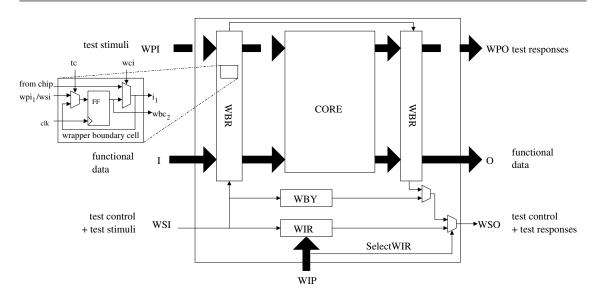

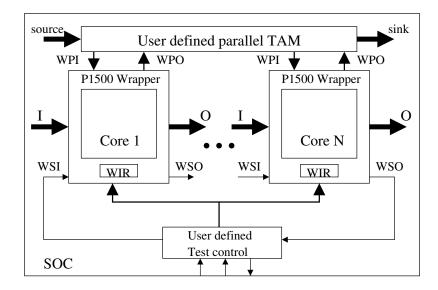

The P1500 core wrapper is a shell which allows various configurations at its inputs and outputs, i.e., various operating modes. A IEEE P1500 core wrapper is illustrated in Figure 1.6. The wrapper has as inputs the wrapper parallel input (WPI), the wrapper

<sup>&</sup>lt;sup>2</sup>"Non-merged" refers to cores that are tested as separate entities with test patterns developed for each core as stand alone [51]

serial input (WSI) and the functional inputs (I), and the wrapper interface port (WIP). The outputs are the wrapper parallel output (WPO), the wrapper serial output (WSO) and the functional outputs (O). The core wrapper comprises two wrapper boundary registers (WBR), the wrapper bypass register (WBY) and the wrapper instruction register (WIR).

The WBRs provide the interface between the test environment and the core, facilitating the test modes noted in Section 1.2: normal operation, core-internal test and coreexternal test. The WBR is a register formed out of wrapper boundary scan cells. The wrapper cell assigned to the inputs are referred to as wrapper boundary input cells, while those assigned to the outputs are referred to as wrapper boundary output cells. The cell illustrated in the top-left part of Figure 1.6 is a wrapper boundary input cell. The functionality of the cell is similar to the scan cell (see Appendix A). One difference is the output multiplexer controlled by the wrapper control input (wci) which differentiate between the test mode and the normal functional mode.

The WIP facilitates the load of instructions corresponding to the above modes into the WIR. For each of the above modes there can be different configurations. For example, there can be a serial internal test, when the test stimuli are provided through the WSI (serial access), and the test responses are observed at the WSO; or a parallel internal test when the test stimuli are provided through the WPI (parallel access), and the test responses are observed at the WPO. It should be noted that this dissertation targets core internal tests, for both the serial and the parallel configurations. However, the methodologies presented are also applicable to core external tests. While the behaviour of the core wrapper and its interface are standardised, the design of the core wrapper itself can be adapted for the system integrator's necessities. The usage of the serial and parallel test access are illustrated next for a fictive core.

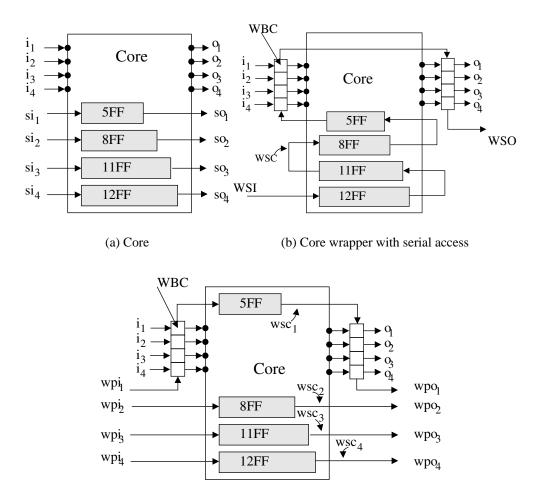

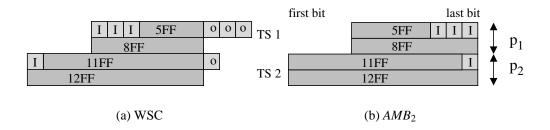

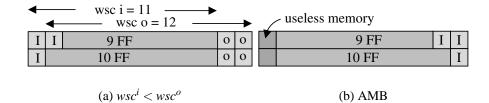

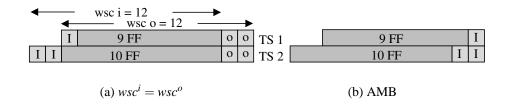

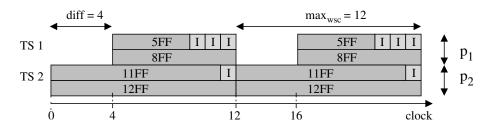

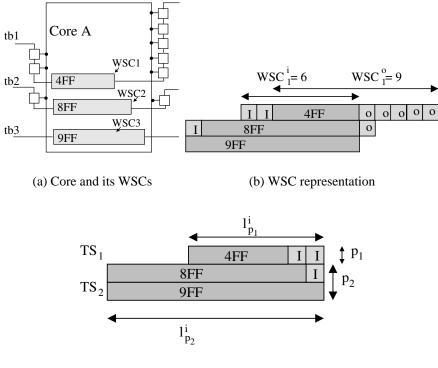

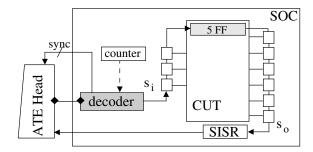

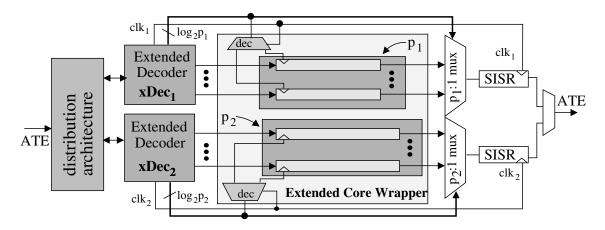

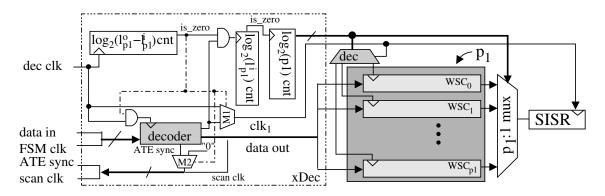

Core wrapper design implies the construction of wrapper scan chains (WSCs). A WSC comprises a number of wrapper boundary input cells, scan chains and wrapper boundary output cells. Corresponding to the two types of access (serial or parallel) the WSC construction is either a simple concatenation of scan chains, or an optimisation problem with respect to minimum test application time. This is illustrated in Figure 1.7 where for the core in Figure 1.7(a), a core wrapper design for a serial test access is given in Figure 1.7(b), and a possible WSC configuration for a parallel test access is given Figure 1.7(c). The core illustrated in Figure 1.7(a) has four inputs ( $i_1$ , $i_2$ , $i_3$  and  $i_4$ ), four outputs ( $o_1$ , $o_2$ , $o_3$  and  $o_4$ ) and four scan chains ( $s_1$ , $s_2$ , $s_3$  and  $s_4$ ) of length 5,8,11 and 12

(c) Core wrapper with parallel access

FFs respectively. In Figure 1.7(b), the internal scan chains and the WBCs are connected together into a long scan chain, while in Figure 1.7(c) a four bit wide WPI port is assumed, and the four WSCs have been constructed accordingly. For example, in the case of  $WSC_1$ , four wrapper boundary input cells are chained together with  $s_1$ , and with four wrapper boundary output cells. Similar to multiple scan chain designs, using a greater number of WSCs can lead to a smaller test application time (TAT). It can be observed in Figure 1.7(b) that the length of the WSC is considerable greater than the length of the WSCs in Figure 1.7(c). Hence, the advantage of reducing TAT when parallel test access is available. While apparently simple, the core wrapper design problem for parallel test access has been shown to be an NP - hard problem [56, 57] (an optimum solution is found in at least exponential computational time [58, 59]). The maximum number of WSCs is dictated by the width of the parallel test access mechanism, as it will be seen next.

Figure 1.8. SOC with P1500 based cores wrappers [55]

#### Test access mechanism (TAM) design

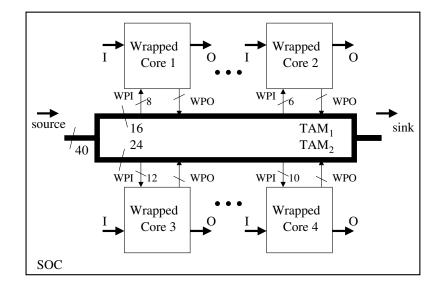

It was illustrated previously that the core wrapper can be connected to either a serial test TAM, or a parallel one. In both cases, the system integrator has to ensure proper access to the core. Based on the IEEE P1500 core wrapper, in Figure 1.8 a SOC test scenario is illustrated when both, a serial and a parallel TAM are defined. The serial TAM is a one bit bus connected to the WSIs and WSOs of each core. The parallel TAM on the other hand is optional, its width is the system integrator's choice. The parallel TAM is in effect a bus of a given width connected to the WPIs and WPOs of the cores. The figure also shows the user defined test control which based on a known test scheduling scheme starts the test sessions corresponding to the various cores. The source and sink can be on-chip divided across multiple TAMs, each of them having different widths. The width of the TAM and the number of TAM lines used to connect the various cores may differ. This is illustrated in Figure 1.9, for a SOC comprising four cores connected to two TAMs. The test control and the WSIs/WSOs have been omitted for clarity. As it can be seen in Figure 1.9, the 40 bit TAM originating from the source is divided into two TAMs of 16 and 24 bits respectively. Cores 1 and 3 are using the maximum available TAM width -8TAM lines for WPI and WPO in the case of *Core*1, and 12 TAM line for WPI and WPO in the case of Core3. Cores 2 and 4, on the other hand are using only 6 and 10 TAM lines respectively. Determining the widths of the TAMs and the assignment of cores to TAMs depending on the system integrator's constraints, e.g., the maximum TAT, the maximum TAM width, and routing constraints, is known as TAM design. The TAM design problem

Figure 1.9. SOC with multiple TAMs

has been also shown to be NP - hard [60, 61]. As illustrated in both Figures 1.8 and 1.9, the TAM is connected to the source and sink. These can be on-chip (BIST source and sink) and off-chip (ATEs source and sink). The ATE is illustrated in the following section.

## **1.2.2** Automated test equipment (ATE)

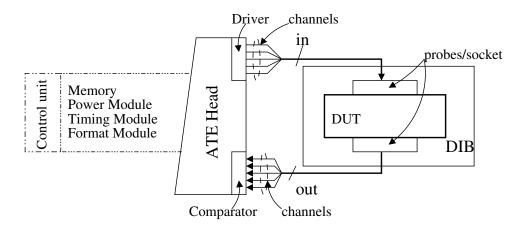

As emphasised in Section 1.1.1 and illustrated with the conceptual architectures in the beginning of Section 1.2, regardless of the embedded DFT method, each chip after manufacturing has to be tested using an automated test equipment (ATE). Testing implies applying a set of test stimuli to the device under test (DUT) and verifying the correctness of the test responses. The ATE is a precision measurement tool which is responsible for providing the required test patterns to the input of the DUT and for comparing the DUT responses to the fault free test responses [19]. A generic ATE – DUT interface is illustrated in Figure 1.10. The ATE is connected to a device interface board (DIB) which is connected to a wafer prober for testing of uncut and unpackaged wafers, or to a socket for testing packaged chips [38]. Due to the high precision electronics on the ATE the cost of these machines is considerable. It is estimated in the international roadmap for semiconductors (ITRS) [13] that the cost of an ATE can exceed \$20*M*. In addition, as it will be seen later in Section 1.3, the cost of the DIB can also considerably influence the overall cost of the ATE, and hence of the design. Thus, it is desirable to reduce the inter-

Figure 1.10. ATE – DUT interface

action and the changes required to the DIB, through elimination of this component from the cost of test. The test stimuli are applied to the DUT using the driver, and the DUT responses are compared to the fault free responses using the comparator as illustrated in Figure 1.10. The channels are the connection between the ATE and the DIB. The generic ATE illustrated in the figure comprises: memory – to store the test stimuli and required timing information; power module - to generate the required high and low voltages and precisely measuring the circuit outputs; format module - to prepare the data, to be sent to the DUT, considering the test stimuli and the timing information; timing module - to define the clock edges for each pin; and control unit – a computer which monitors the entire process, and stores the test result: good/bad chip. There are a number of parameters which characterise the ATE. These include: the number of ATE channels (or ATE test pins) – the number of chip pins which can be connected to the ATE; the ATE frequency – the frequency with which the ATE is capable of supplying data on the ATE channels; the ATE accuracy – the accuracy of the device to provide test data with respect to the ATE clock, e.g., for an ATE frequency of 1GHz the accuracy is of  $\pm 200ps$  – the data will be accurate within  $\pm 200 ps$  from the rising edge of the clock.

The amount of time required to complete one test set is referred to as test application time (TAT). In this dissertation it is considered that the TAT is given in ATE clock cycles. As it will be seen in the following section, where the cost of test is analysed, the ATE has a substantial contribution to the overall cost of test. The main reason for this is that regardless of the type of methodology embedded within the chip, the chip has to go through the manufacturing testing process. And hence, it has to be tested using an ATE. In addition, due to the fact that ATEs are built using previously available technology, they are limited in providing the performances required by cutting edge chips.

Figure 1.11. Test and manufacturing cost per transistor [13]

# **1.3** Cost of test

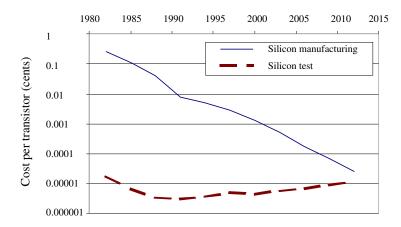

Testing SOCs requires the insertion of SOC DFT which facilitates the test of the embedded cores and the entire system. In addition to the SOC DFT problems illustrated in the previous section, another important issue is the cost of test. It is anticipated in the ITRS that, if the current trends are maintained, the cost of testing a transistor will approach and may even exceed the cost of manufacturing it [13]. This is illustrated in Figure 1.11, where the test curve will intersect the manufacturing curve by 2015. To motivate the work described in this thesis and at the same time highlight the importance of considering low-cost SOC test, in this section the cost of test and the main parameters which drive its continuous increase are analysed.

Conceptually the cost of test  $(C_{test})$  [62] can be computed as given below:

$$C_{test} = C_{prep} + C_{exec} + C_{silicon} + C_{quality}$$

(1.1)

where:

- *C*<sub>prep</sub> the fixed cost of test preparation. It captures fixed costs of test generation, tester program creation, and any design efforts for incorporating any test related features, i.e., it includes all non-recurring costs, including software systems;

- *C<sub>exec</sub>* the cost of test execution. Consists of test related hardware and it includes: tester setup time, tester execution time, capital cost of the tester and capital equipment depreciation rate;

- *C<sub>silicon</sub>* is the cost required to incorporate DFT features;

•  $C_{quality}$  - is the cost of imperfect test quality. That is, the profit loss from performance degradation caused by the added DFT circuitry, the test of cost escape (the relation between fault coverage and fault occurrence - or simply yield), and cost of good dies being deemed faulty by imperfect test;

With SOCs comprising cores at different levels of abstractions provided by third party vendors, none of the above components are directly under the control of the system integrator. That is, both the core user and the system integrator influence them. For example, the system integrator ensures the proper TAM and on-chip test pattern source and sink through SOC DFT, however, the core vendor incorporates the core level DFT to ensure the required fault coverage (see Section 1.2). These two are related since the core level DFT influences the system level DFT requirements. In addition, the test quality ( $C_{auality}$ ) depends on the fault coverage and the types of faults targeted by the core level DFT [37], hence these must be in concordance with system integrators' necessities [48], i.e., manufacturing process. Therefore, the more information the core vendor has about the final manufacturing process used by the system integrator the greater the chance the delivered core is suitable for the system integrator's needs. Driven by the need for high quality test and the assurance that the core performance is in concordance with the specifications, the system integrator prefers hard cores [1]. As noted in Section 1.1.2, these come with predictable area and performance, however, they lack flexibility. This lack of flexibility restricts the system integrator from performing fault simulation and ATPG, hence it is constraint to accepting the core's DFT and test information delivered with the core "as is". As it will be seen in Section 1.3.1, the cost of test execution ( $C_{exec}$ ) is also dependent on the test time of the cores which is influenced by the core DFT methodology and the SOC DFT. Hence, this cost is also, to some extend, dependent on both the core vendor and the system integrator.

While in order to reduce the cost of test, all the four parameters are sought small,  $C_{prep}$  is a fixed cost per design,  $C_{quality}$  is directly dependent on the core DFT methodology, and  $C_{silicon}$  is a requirement for providing core level DFT. Hence, cost reduction in manufacturing test is possible if the  $C_{exec}$  is reduced. This is because each chip, regardless of the area overhead or the fault coverage obtained by using DFT, has to be physically tested. Therefore, while all the parameters are sought small, this work will address the issue of reducing the overall cost of test with special emphasis on the *cost of test execution*, detailed in the next section.

### **1.3.1** Cost of test execution

As shown in Equation (1.1), the cost of test execution is part of the cost of test and it includes: tester setup time, tester execution time, capital cost of the tester and capital equipment depreciation rate. The cost of test execution can be approximated using the following equation:

$$C_{exec} \approx C_{hw} + T_{tester} \times C_{tester} \tag{1.2}$$

where  $C_{hw}$  represents the cost of necessary hardware to perform the test (excepting the cost of the tester),  $C_{tester}$  represents the cost of the tester, and  $T_{tester}$  represents the time spent on the tester. These three components are analysed next.

**Cost of extra hardware**  $C_{hw}$  represents a recurring cost per design, and comprises the cost of the probes and sockets, and the cost of extending the device interface board (DIB) to accommodate for different DFT features. The cost of the sockets and probes is bounded by the physical handling of the DUT. The DIB, due to the mix of high and low frequency signals, requires special design techniques in order to provide the DUT with unaltered signals [63, 64]. In addition, the various extension required by various DFT techniques – e.g., external clocks, serialisation units, are also implemented on the DIB [65]. Therefore, the DIB can considerably influence the cost of the design, especially since the DIB is custom built for the exact pin specification of the DUT [13]. While the cost of the DIB cannot be eliminated completely from the cost equation, it is desirable to reduce the interaction and the changes required to the DIB, hence reducing the cost of  $C_{hw}$ .

**Test time** The semiconductor industry is building 300nm fabs capable of producing up to 2000 wafers per week. With the average test time of a wafer of up to 24 hours [9], the test execution time clearly becomes an important factor in the overall test cost. To illustrate the importance of  $T_{tester}$ , Figure 1.12 shows the increase in test time relative to 1999. It becomes clear from the figure that the increase in test time is considerable, and the trend is an ascending one.  $T_{tester}$  from the Equation (1.2) can be further detailed as illustrated below:

$$T_{tester} \approx T_{inactive} + T_{active} \tag{1.3}$$

where, the time spent on tester  $T_{tester}$  is divided into the time when the tester is just providing a socket for the DUT, since it is inactive ( $T_{inactive}$ ), i.e., like in the case of internal-only

Figure 1.12. Test time increase relative to 1999 [15]

testing where the interaction between the tester and the DUT is reduced to a minimum; and the time when the tester is actively testing the DUT ( $T_{active}$ ).  $T_{inactive}$  is mainly due to inefficient tester usage, for example, when a BIST session is started the LFSR will generate patterns for a given number of clock cycles. In this time, the tester is not used, leading to inefficient tester usage. Therefore,  $T_{inactive}$  main increase the cost since the DUT has to physically remain connected to the tester until the entire test process is finished.

$T_{active}$ , on the other hand, is determined by the volume of test data (VTD), needed to test the DUT, and the ATE parameters, as illustrated below:

$$T_{active} = \frac{VTD}{n_{ate} \times f_{ate}} \tag{1.4}$$

where,  $n_{ate}$  represent the number of ATE channels used for testing the DUT, and  $f_{ate}$  represents the ATE operating frequency. The product  $n_{ate} \times f_{ate}$  is also referred to as the bandwidth. The test time increase illustrated in Figure 1.12 is due to the continuous increase in VTD and the insufficient ATE bandwidth when compared to the requirements. These are illustrated next.

Figure 1.13. Gate count vs. volume of test data trend [66]

The VTD for single scan chain designs can be approximated using equation

$$(1.5)$$

:

$$VTD \approx scan_chain_length \times no_patterns$$

(1.5)

i.e., the VTD is given by the length of the scan chain multiplied with the number of scan patterns [9]. Since, the number of scan cells is directly related to the number of gates (typically, 1 scan cell to every 20 gates) [9], the number of scan cells will increase directly proportional to the number of gates. The number of gates, according to Moore's "law", doubles every 18 months, and hence, the number of scan cells will double every 18 months as well. Since, the VTD is proportional with the number of scan cells, it will also double every 18 month, and therefore, the ATE memory requirements will also **double** every 18 month. This is illustrated in Figure 1.13, where the increase in VTD (given in giga bytes) with the increase in design size (given in million of gates) follows the above rule. In addition to the above, further increase in VTD is expected due to DFT methods' dependencies on scan to deliver their test vectors. For example, delay and open faults require pairs of scan test vectors when tested. In order for the ATE upgrade is needed to meet the new memory capacity requirements.

From the above discussion a potential solution to reduce test time, and hence reduce one of the factors that contribute to  $C_{exec}$ , is to reduce the VTD and inefficient ATE usage.

Figure 1.14. Growth in complexity and bandwidth relative to 1999 [15]

The alternative solution, of increasing the bandwidth, is analysed next.

It is immediately derived from Equation (1.4) that the test time can be reduce if the bandwidth is increased. This however, encounters the following limitations. Firstly, the available ATE bandwidth does not increases at the same rate as the IC bandwidth [14]. And secondly, not all the chip pins can be used for testing, and therefore, there is a gap between the required bandwidth and the available bandwidth for test [15] (see Figure 1.14). Finally, increasing the available ATE bandwidth is followed by an increase in ATE cost, hence, reducing test time at the expense of an increase in  $C_{tester}$ . The cost of the tester is analysed next.

**Cost of tester** The cost of the tester ( $C_{tester}$ ) from Equation (1.2), can be further divided into the cost of the test equipment itself ( $C_{ate}$ ), and the various cost of handling the test equipment ( $C_{handling}$ )

$$C_{tester} \approx C_{ate} + C_{handling} \tag{1.6}$$

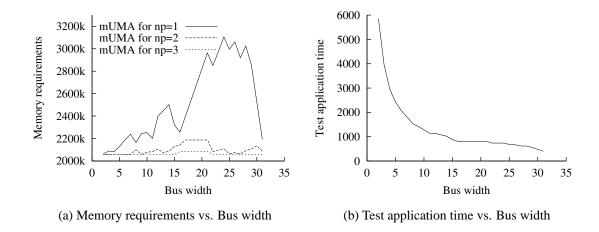

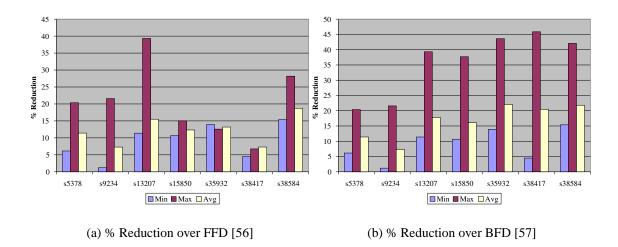

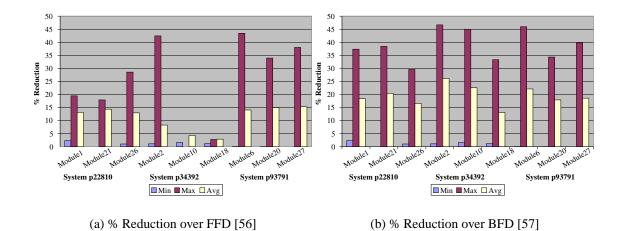

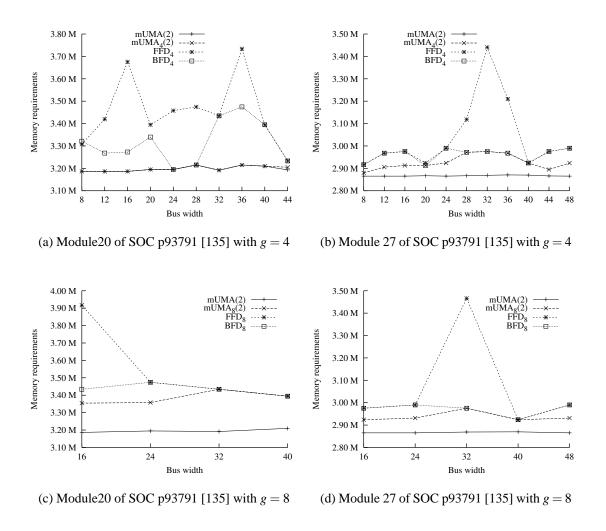

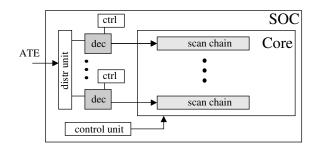

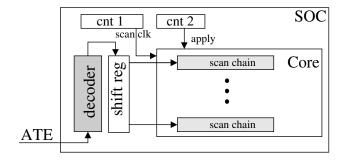

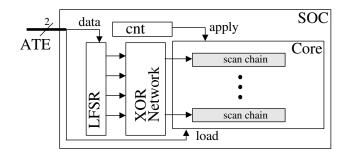

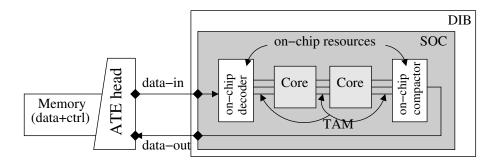

The increase in pin count and the mixture of various technologies in system chips, causes ATE costs - for running the tests as well as the equipment itself - to increase significantly according to [13]. Furthermore, ATEs with higher accuracy are much more expensive than lower accuracy ATEs [11]. Thus, increasing the ATE operating frequency and the number of ATE pins, hence the bandwidth, does not provide viable solutions for low-cost system test, as they increase the cost of the ATE itself. Therefore, in order to keep the cost of ATE low, *reduce pin count test (RPCT)* methodologies, and methods which *reduce the bandwidth requirements* are needed. It should be noted that there is a clear distinction between RPCT and reduced bandwidth requirements. The former refers to reducing the