# Logic Design

#### Asynchronous Sequential circuits

### Asynchronous Sequential Circuits

- Synchronous sequential circuits: operation is controlled by a clock pulse (operates in pulse mode)

- Sequential circuits that do not operate in pulse mode and do not use flip-flops

- In asynchronous sequential circuits changes in state are not triggered by clock pulses but by change in the inputs

- Conditions:

- Inputs must change one at a time

- Sufficient time exists between changes in input signals so all internal signals stop changing

- Above conditions true: circuit is operating in the fundamental mode

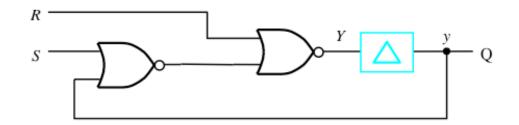

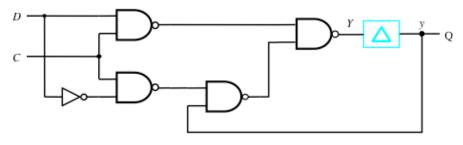

(b) Circuit with modeled gate delay

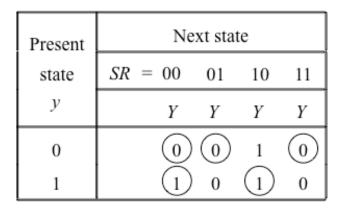

(b) State-assigned table

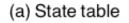

Figure 9.1. Analysis of the SR latch.

- Because of the feedback the circuit is sequential

- Box labeled  $\Delta$  represents combined propagation delays through two NOR gates

- y is the current state

- Y is the next state

- After a  $\Delta$  time delay y takes the value of Y

- If for a particular input y is not equal to Y, the circuit is not stable

- Stable states are indicated by circles

- We can derive state table and state diagram

| Present | Next state            | Output |

|---------|-----------------------|--------|

| state   | SR = 00  01  10  11   | Q      |

| А       | (A) $(A)$ $(B)$ $(A)$ | 0      |

| В       | B A B A               | 1      |

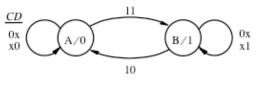

(b) State diagram

Figure 9.2. FSM model for the SR latch.

- Consider the opposite task: synthesis of an asynchronous circuit

- Using the state assigned table to find minimal SOP yields:

- Y=R'.(S+y)

- If we were doing synchronous circuits we would use a D flipflop

- Here, we create a circuit that realizes the expression and we feed back the output signal as the present state input y

- In asynchronous circuits:

- State table => flow table

- State-assigned table => transition table or excitation table

### Gated D latch

- We consider the clock signal to be one of the input signals

- Y=CD+C'y+Dy

- Using the consensus theorem: Y=CD+C'y

(a) Circuit

| Present |      | Next state |    |    |    |   |

|---------|------|------------|----|----|----|---|

| state   | CD = | 00         | 01 | 10 | 11 |   |

| У       |      | Y          | Y  | Y  | Y  | Q |

| 0       |      | 0          | 0  | 0  | 1  | 0 |

| 1       |      | 1          | 1  | 0  | 1  | 1 |

#### (b) Excitation table

| Present | Next state |    |    |    |   |

|---------|------------|----|----|----|---|

| state   | CD = 00    | 01 | 10 | 11 | Q |

| А       | A          | A  | A  | в  | 0 |

| в       | В          | в  | А  | в  | 1 |

(c) Flow table

(d) State diagram

#### Figure 9.4. The gated D latch.

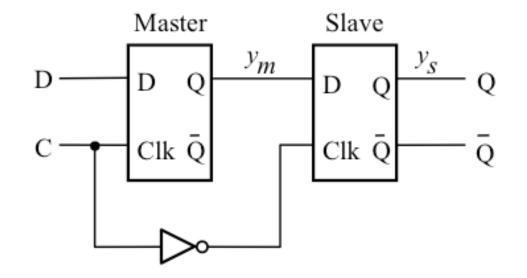

#### Master Slave D Flip-flop

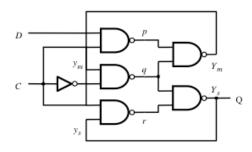

- Ym=CD+C'ym

- Ys=C'ym+Cys

#### Master Slave D Flip-flop

Figure 9.5. Circuit for the master-slave D flip-flop.

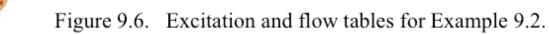

| Present | Next state          |        |

|---------|---------------------|--------|

| state   | CD = 00  01  10  11 | Output |

| ym ys   | $Y_m Y_s$           | Q      |

| 00      | 00 00 00 10         | 0      |

| 01      | 00 00 (01) 11       | 1      |

| 10      | 11 11 00 🕕          | 0      |

| 11      |                     | 1      |

#### (a) Excitationtable

| Present | Nex     | Next state |     |     |             |

|---------|---------|------------|-----|-----|-------------|

| state   | CD = 00 | 01         | 10  | 11  | Output<br>Q |

| S1      | S1      | S1)        | S1) | S3  | 0           |

| S2      | S1      | <b>S</b> 1 | \$2 | S4  | 1           |

| S3      | S4      | S4         | S1  | \$3 | 0           |

| S4      | \$4     | <u>\$4</u> | S2  | 64  | 1           |

(b) Flow table

| Present    | ent Next state |            |              |     | Output |

|------------|----------------|------------|--------------|-----|--------|

| state      | CD = 00        | 01         | 10           | 11  | Q      |

| S1         | <u>(S1</u>     | <b>S</b> 1 | <u>(S1</u> ) | S3  | 0      |

| S2         | S1             | _          | $\odot$      | S4  | 1      |

| <b>S</b> 3 | -              | S4         | S1           | \$3 | 0      |

| S4         | \$4            | \$4        | S2           | \$4 | 1      |

(c) Flow Table with unspecified entries

McMaster University

#### Master Slave D Flip-flop

Figure 9.7. State diagram for the master-slave D flip-flop.

#### Master Slave D Flip-flop

- Since we assumed that inputs must change one at a time, if the circuit is stable in state S2 for which CD=10 it cannot go to S1 under the input valuation CD=01 because simultaneous change in both inputs cannot happen

- These changes are labeled unspecified in the table.

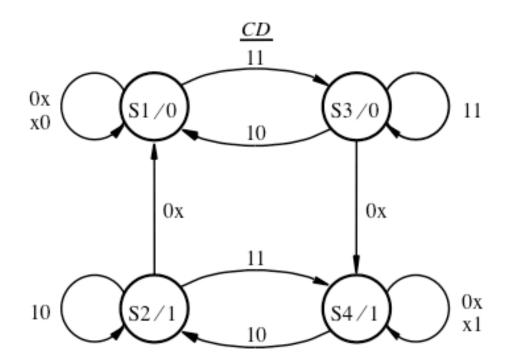

Figure 9.8. Circuit for Example 9.3.

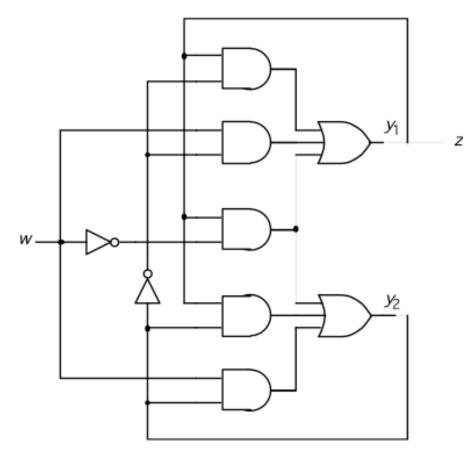

- Y1=y1y2'+w1y2'+w1'w2'y1

- Y2=y1y2+w1y2+w2+w1'w2'y1

- Z=y1'y2

| Present               |                |           |           |           |        |

|-----------------------|----------------|-----------|-----------|-----------|--------|

| state                 | $w_2 w_1 = 00$ | 01        | 10        | 11        | Output |

| <i>y</i> 2 <i>y</i> 1 | $Y_2 Y_1$      | $Y_2 Y_1$ | $Y_2 Y_1$ | $Y_2 Y_1$ | z      |

| 00                    | 00             | 01        | 10        | 11        | 0      |

| 01                    | 11             | (01)      | 11        | 11        | 0      |

| 10                    | 00             | 10        | (10)      | (10)      | 1      |

| 11                    | (1)            | 10        | 10        | 10        | 0      |

(a) Excitation table

| Present | Next state     |            |            |         | Output |

|---------|----------------|------------|------------|---------|--------|

| state   | $w_2 w_1 = 00$ | 01         | 10         | 11      | z      |

| А       | A              | В          | С          | D       | 0      |

| В       | D              | В          | D          | D       | 0      |

| С       | A              | $^{\odot}$ | $^{\odot}$ | $\odot$ | 1      |

| D       | D              | С          | С          | С       | 0      |

(b) Flow table

M Un

Figure 9.9. Excitation and flow tables for the circuit in Figure 9.8. Shirani

| Present | Next state     |         |         |         | Output |

|---------|----------------|---------|---------|---------|--------|

| state   | $w_2 w_1 = 00$ | 01      | 10      | 11      | z      |

| А       | A              | В       | С       |         | 0      |

| В       | D              | В       | _       | D       | 0      |

| С       | А              | $\odot$ | $\odot$ | $\odot$ | 1      |

| D       | D              | С       | С       | С       | 0      |

Figure 9.10. Modified flow table for Example 9.3.

Figure 9.11. State table for Example 9.3.

#### Analysis Process

- Each feedback path is cut and a delay element is inserted at the point where the cut is made.

- The input to the delay is a next state variable Yi and the output is present state variable yi

- Cut can be make anywhere in the loop

- The number of cuts is the smallest number that results in being no feedback anywhere in the circuit (cut set)

- Next state and output expressions are derived from the circuit

- Excitation table is derived

- Flow table is obtained

- State diagram is derived

## Synthesis

- 1. Devise a state diagram for an FSM that realizes the required functional behavior

- 2. Derive the flow table and reduce the number of states if possible

- 3. Perform the state assignment and derive the excitation table

- 4. Obtain the next state and output expressions

- 5. Construct a circuit that implements these expressions

- Note: When devising a state diagram, it is essential to ensure when the circuit is in stable state correct output signals are generated. Should it be necessary to pass through an unstable state, this state must not produce an undesirable output

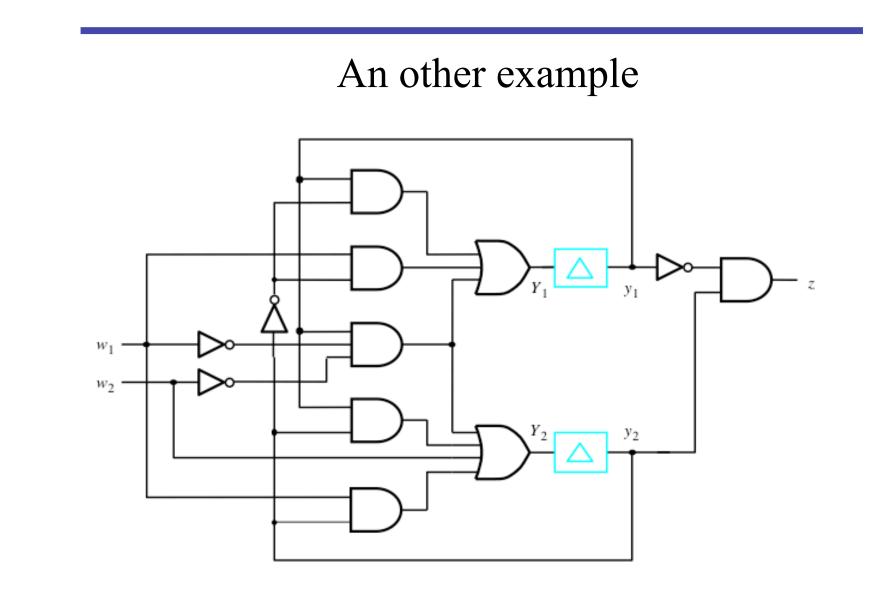

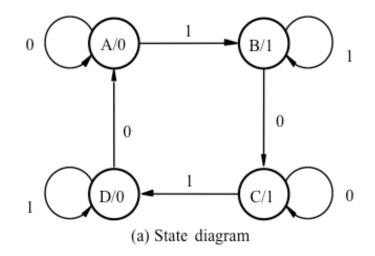

• We want to design a circuit with input w and output z such that z is equal to 0 if the number of previously applied pulses to w is even and z is equal to 1 if the number of pulses is odd.

- State A: an even number of pulses have arrived and the current value of the input is 0

- State B: an odd number of pulses have arrived and the current value of the input is 1

- State C: an odd number of pulses have arrived and the current value of the input is 0

- State D: an even number of pulses have arrived and the current value of the input is 1

| Present | Next  | Output |   |

|---------|-------|--------|---|

| State   | w = 0 | w = 1  | z |

| A       | A     | В      | 0 |

| В       | С     | В      | 1 |

| С       | C     | D      | 1 |

| D       | А     | D      | 0 |

(b) Flow table

Figure 9.13. Parity-generating asynchronous FSM.

• States B and C cannot be combined because it is impossible to have B both stable under w=1 and change to D for w=1

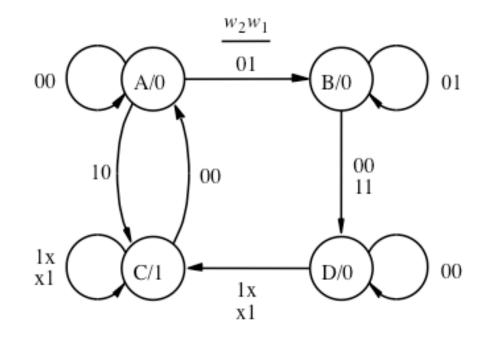

| Р | resent | Next          |     |        |

|---|--------|---------------|-----|--------|

|   | state  | w = 0 $w = 1$ |     | Output |

|   | y2 y1  | $Y_2 Y_1$     |     | z      |

| Γ | 00     | 00            | 01  | 0      |

|   | 01     | 10            | (0) | 1      |

|   | 10     | 10            | 11  | 1      |

|   | 11     | 00            | (1) | 0      |

(a) Poor state assignment

| Present               | Next          |      |        |

|-----------------------|---------------|------|--------|

| state                 | w = 0 $w = 1$ |      | Output |

| <i>y</i> 2 <i>y</i> 1 | $Y_2$         | z    |        |

| 00                    | (0)           | 01   | 0      |

| 01                    | 11            | (01) | 1      |

| 11                    | (11)          | 10   | 1      |

| 10                    | 00            | (10) | 0      |

(b) Good state assignment

Figure 9.14. State assignment for Figure 9.13b.

- Problem with the first state assignment:

- Assume circuit is stable in state 11 with w=1

- Input changes to w=0

- State should change from 11 to 00.

- Both state variables must change their values

- In asynchronous circuits values of the next states are determined by logic gates with varying propagation delays.

- One variable will change slightly before the other

### Race condition

- Scenario 1: y1 changes first

- Circuit goes from 11 to 10.

- As soon as it reaches 10 with w=0 it will stay there

- Scenario 2: y2 changes first

- Circuit goes from 11 to 01

- According to the table with w=0 it will try to change to 10

- This again requires both y's to change.

- If y1 changes first the circuits is going to be stable in 00 with w=0

- Uncertainty caused by multiple changes in the state variables in response to input: race condition

Figure 9.15. Circuit that implements the FSM in Figure 9.13b. University

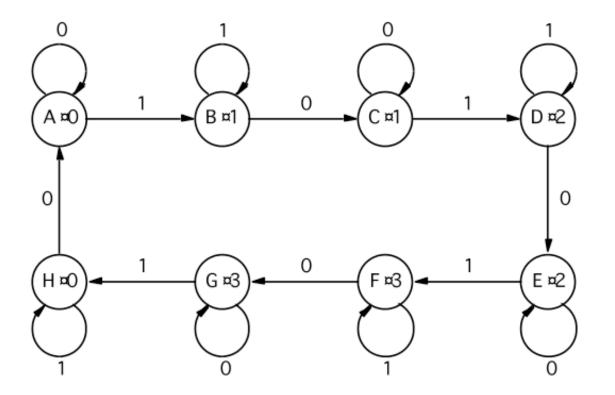

#### Modulo-4 counter

Figure 9.17. State diagram for a modulo-4 counter.

| Present | Next  | Output |   |

|---------|-------|--------|---|

| state   | w = 0 | w = 1  | z |

| А       | A     | в      | 0 |

| в       | С     | В      | 1 |

| с       | C     | D      | 1 |

| D       | Е     | D      | 2 |

| Е       | E     | F      | 2 |

| F       | G     | F      | 3 |

| G       | G     | Н      | 3 |

| Н       | А     | Н      | 0 |

| Present<br>state<br>y3y2y1 | w = 0 | state<br>w = 1<br>$Y_2 Y_1$ | Output<br>Z2Z1                    |  | Mod-8 output<br>Z3Z2Z1 |

|----------------------------|-------|-----------------------------|-----------------------------------|--|------------------------|

| 000                        | 000   | 001                         | 00                                |  | 000                    |

| 001                        | 011   | 001                         | 01                                |  | 001                    |

| 011                        | 011   | 010                         | 01                                |  | 010                    |

| 010                        | 110   | 010                         | 10                                |  | 011                    |

| 110                        | (110) | 111                         | 10                                |  | 100                    |

| 111                        | 101   | (11)                        | 11                                |  | 101                    |

| 101                        | (101) | 100                         | 11                                |  | 110                    |

| 100                        | 000   | (100                        | 00                                |  | 111                    |

| (b) Excitation table       |       |                             | (c) Output for counting the edges |  |                        |

Figure 9.18. Flow and excitation tables for a modulo-4 counter.

Copyright S. Shirani

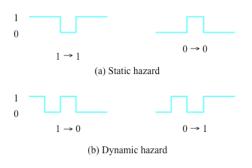

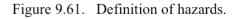

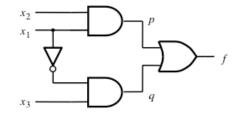

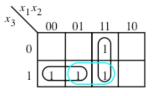

- In asynchronous sequential circuits it is important to avoid glitches

- Glitches caused by the structure of a given circuit and propagation delays are referred to as hazard

- Two types of hazards: static and dynamic

- Static hazard: a signal is supposed to remain at a particular logic value when an input changes it value but instead the signal undergoes a momentary change

- Dynamic hazard: a signal is supposed to change from 0 to 1 (or 1 to 0) but the change involves a short oscillation

- Consider the circuit in the next slide

- Let's assume x1=x2=x3=1, f=1

- Suppose x1 changes to 0

- Point p will see the change before point q

- For a short time both p and q are zero dropping f to zero before recovering back to 1

$$f = x_1 x_2 + x_1 x_3$$

$$f = x_1 x_2 + x_1 x_3 + x_2 x_3$$

(a) Circuit with a hazard

(b) Karnaugh map

(c) Hazard-free circuit

Figure 9.62. An example of a static hazard.

Copyright S. Shirani

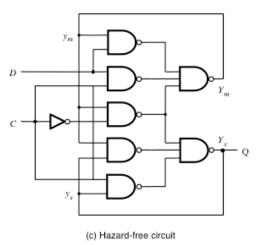

#### Master Slave D Flip Flop

| Present | Next state          |        |

|---------|---------------------|--------|

| state   | CD = 00  01  10  11 | Output |

| ym ys   | Ym Ys               | Q      |

| 00      | 00 00 00 10         | 0      |

| 01      | 00 00 (01) 11       | 1      |

| 10      | 11 11 00 🕕          | 0      |

| 11      |                     | 1      |

(a) Excitationtable

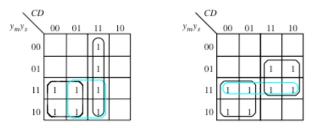

$Y_m = CD + \bar{C} y_m$  $= (C \uparrow D) \uparrow (\bar{C} \uparrow y_m)$

$Y_{s} = Cy_{s} + Cy_{m}$  $= (C \uparrow y_{s}) \uparrow (\bar{C} \uparrow y_{m})$

(a) Minimum-cost circuit

(b) Karnaugh maps for Ym and Ys in Figure 9.6a

Figure 9.63. Two-level implementation of master-slave D flip-flop.

$$Y_m = CD + \bar{C} y_m + Dy_m$$

$$= (C \uparrow D) \uparrow ((C \uparrow \bar{D}) \uparrow y_m)$$

$$Y_{s} = Cy_{s} + \bar{C}y_{m} + y_{m}y_{s}$$

$$= ((\bar{C} \uparrow \bar{y}_{m}) \uparrow y_{s}) \uparrow (\bar{C} \uparrow y_{m})$$

### Dynamic Hazard

- A dynamic hazard is caused by the structure of the circuit where there exist multiple paths for a given signal change to propagate along

- Dynamic hazards are encountered in multilevel circuits obtained using factoring or decomposition techniques

- Dynamic hazards are neither easy to detect nor easy to deal with

- They can be avoided using two-level circuits and ensuring that there are not static hazards