#### DESIGN, AUTOMATION & TEST IN EUROPE

14 – 18 March, 2016 · ICC · Dresden · Germany The European Event for Electronic <u>System Design & Test</u>

## **MCXplore**: An Automated Framework for Validating Memory Controller Designs

https://git.uwaterloo.ca/caesr-pub/mcxplore

Mohamed Hassan and Hiren Patel {mohamed.hassan, hiren.patel}@uwaterloo.ca University of Waterloo

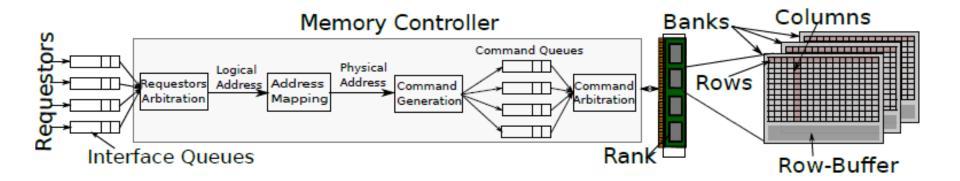

### Background

- There has been a focus on validating processing elements

- Main memory is becoming a vital component in almost all computing systems

#### Background

#### **Simulation-based Validation**

| Benchmarks          | + Time and effort conserving                               | <ul> <li>May not be memory intensive</li> <li>Lack easy-to-analyse memory patterns</li> <li>Do not explore the state space of the memory subsystem properties</li> </ul> |

|---------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exhaustive<br>Tests | + Guaranteed coverage                                      | <ul> <li>Very time and resource consuming (may not be possible)</li> </ul>                                                                                               |

|                     |                                                            |                                                                                                                                                                          |

| Manual<br>Tests     | + Allows for directed testing to cover specific properties | - Time consuming<br>- Prone to human errors                                                                                                                              |

| Random              | + Moderate time and effort                                 | - Questionable test coverage                                                                                                                                             |

| Tests               |                                                            |                                                                                                                                                                          |

#### Outline

- MCxplore, objective and flow

- Validation example from the MC frontend

- Validation example from the MC backend

- Additional features

- Conclusions

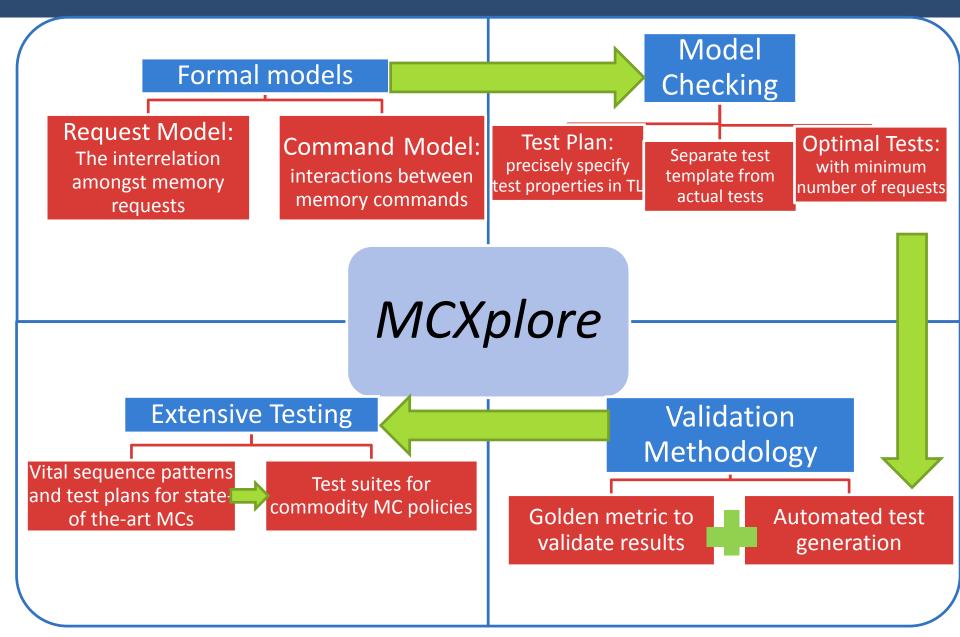

#### Contributions

#### **Proposed Process**

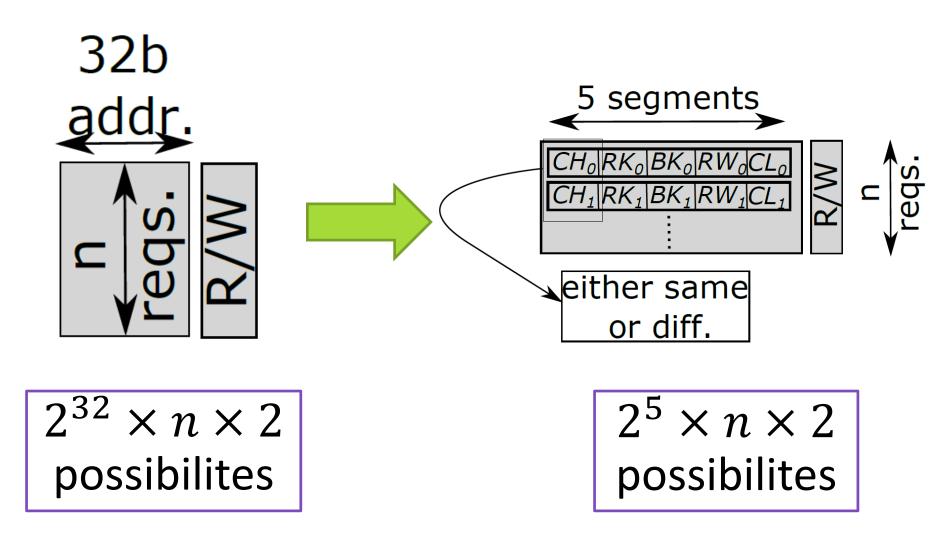

#### **Request Model**

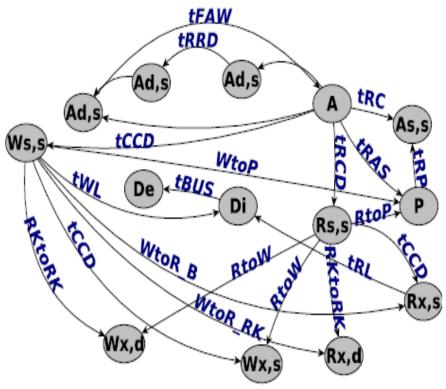

#### **Command Model**

- Simplifies testing properties that are related to timing constraints and command generation

- Enables specifying the timing constraints and *MCXplore* automatically generates the test sequence that exercises these constraints

#### **Evaluation**

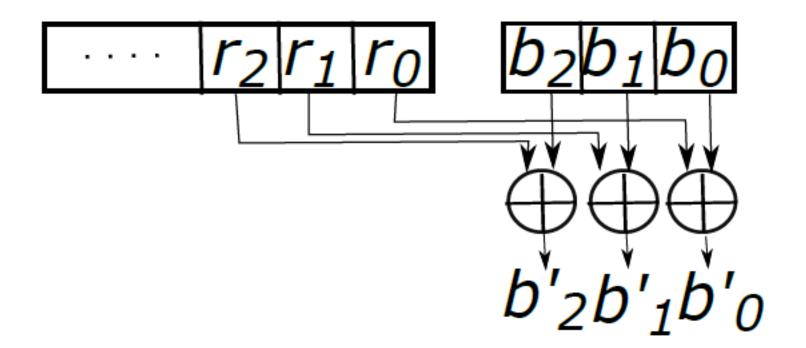

#### **Example: XOR Address Mapping**

| LS row bits | Bank bits | New bank bits |

|-------------|-----------|---------------|

| 001         | 001       | 000           |

| 010         | 001       | 011           |

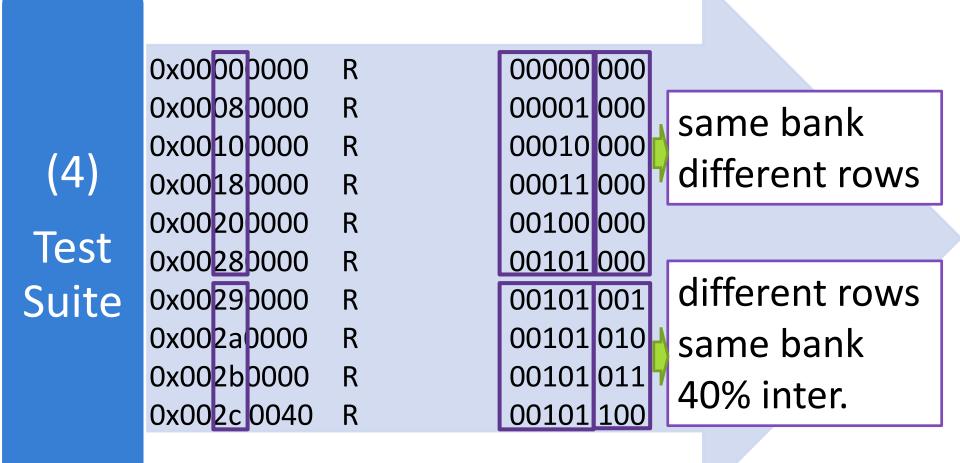

- Optimal memory pattern for the XOR mapping

- A stream of read accesses where we change the bank interleaving ratio per test, requests targeting the same bank are accessing different rows

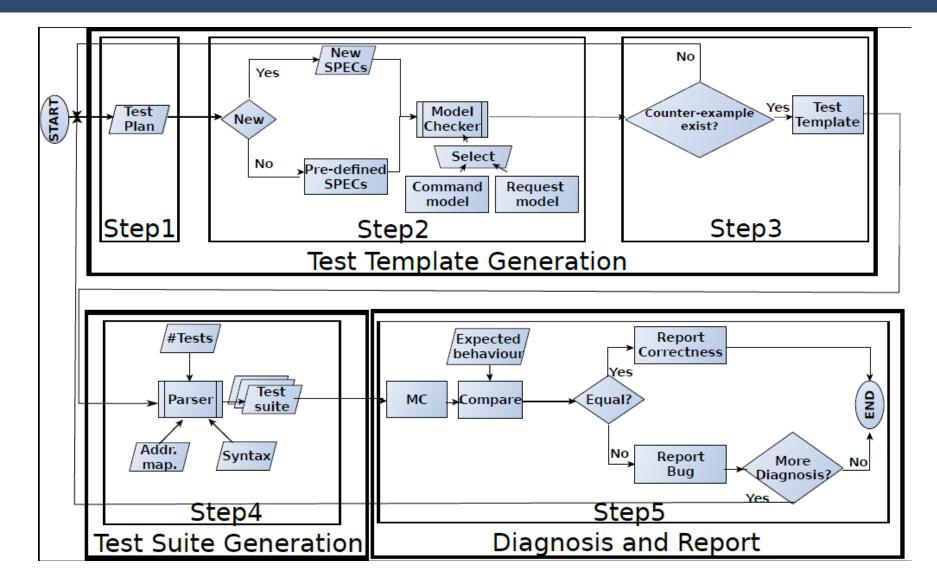

(1)

Test

Plan

(2)

Specs.

$$LTLSPEC$$

$G((t_{req} = 6 \land t_{hit} = 0 \land t_{intr} = 0) - 1$

$F(t_{req} = 10 \land t_{hit} = 4 \land t_{intr} = 4)$

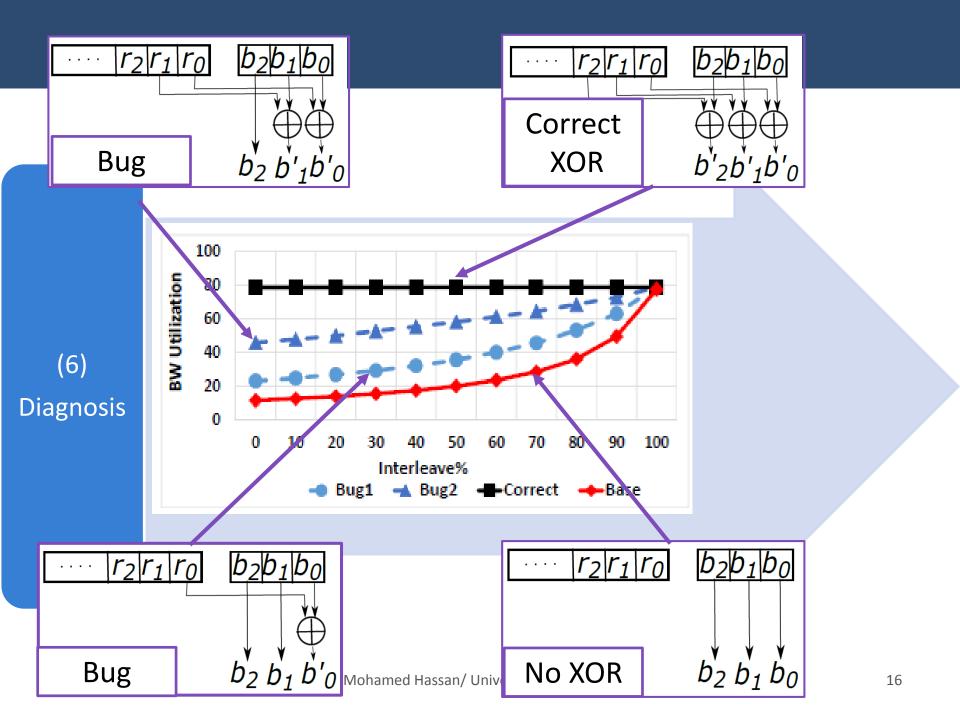

### **XOR Address Mapping**

Model checker produces a counterexample for each specification.

(3) Test Template  Each template has a bank interleaving percentage between 0% and 100%

### **XOR Address Mapping**

### **XOR Address Mapping**

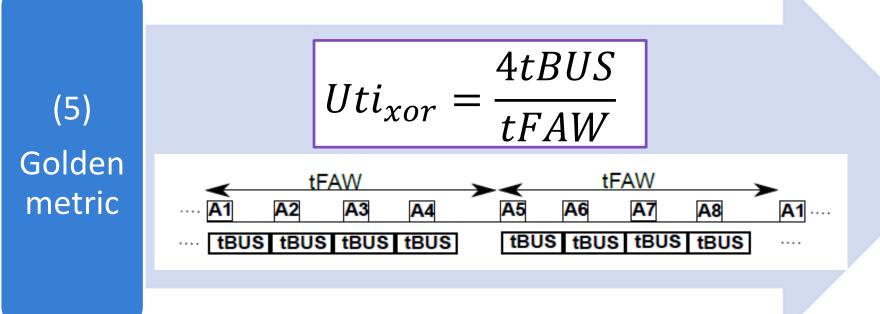

- Elect memory utilization as a golden metric

- It does not require any special debugging capabilities inside the MC

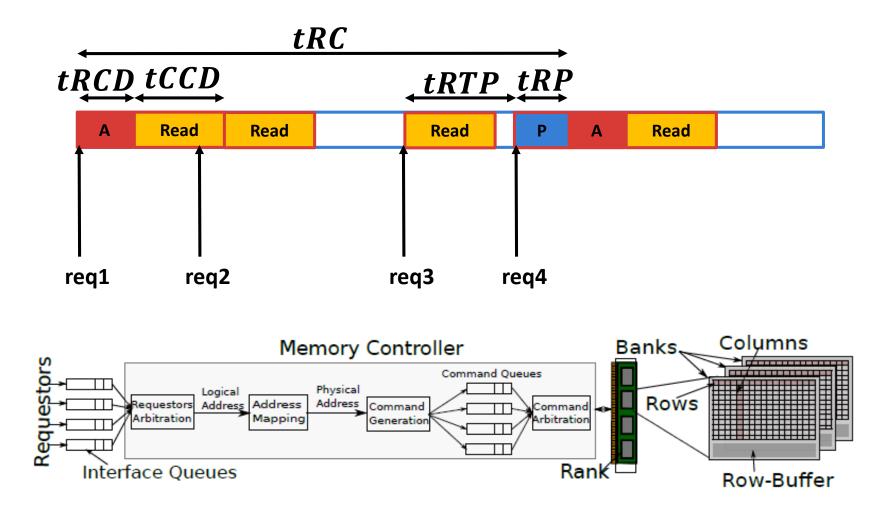

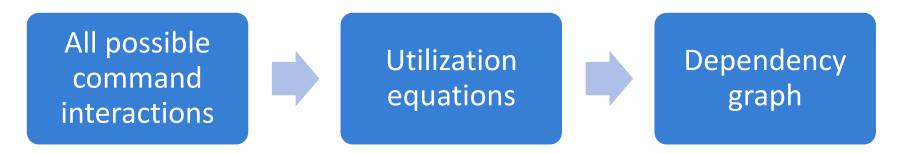

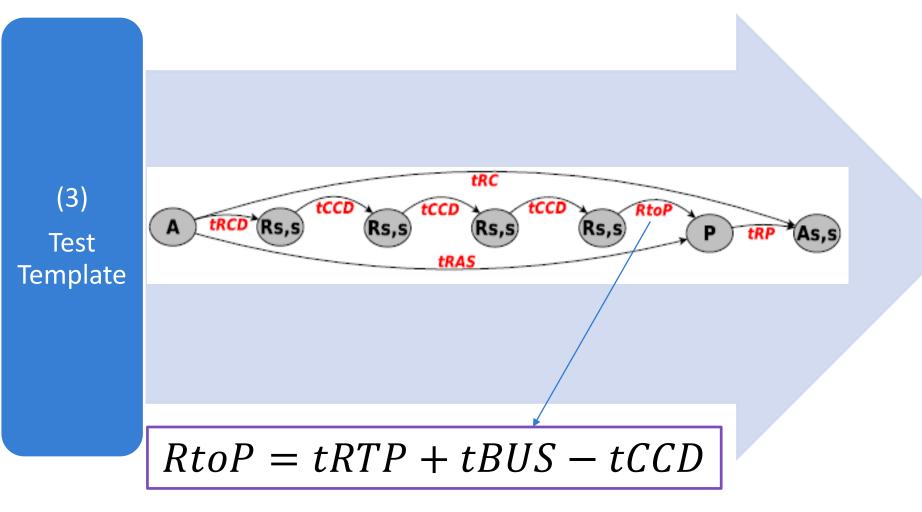

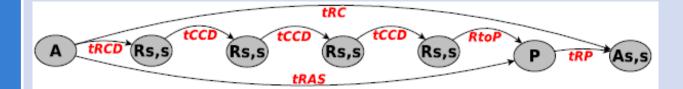

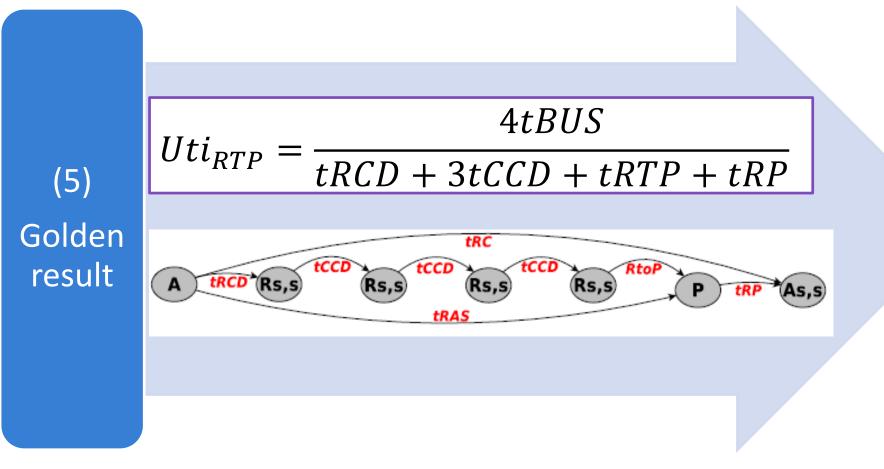

#### **Timing Parameters Validation**

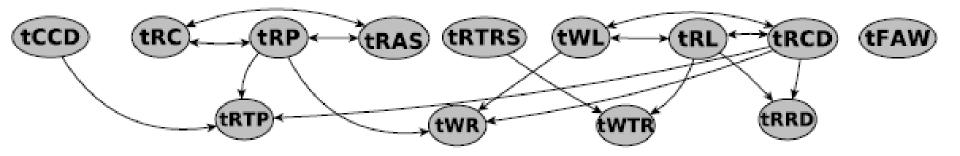

- Each test is designed to maximize the impact of the timing parameter under test while eliminating or minimizing the effect of all other parameters

- Timing parameters dependency graph

#### **Timing Parameters Validation**

- Each test is designed to maximize the impact of the timing parameter under test while eliminating or minimizing the effect of all other parameters

- Timing parameters dependency graph

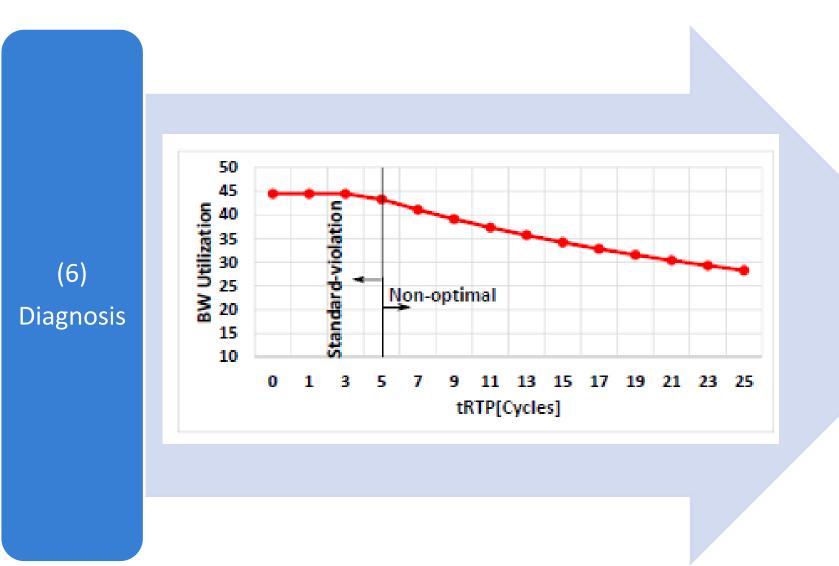

#### **Example: Read-to-Precharge Constraint**

- (1) Test Plan

- Target: validate *tRTP*

- A valid command sequence is A followed by one or more R then a P to close the row followed by an A to a different row

# (2) LTLSPEC $G! (num_{tRTP} \ge 1)$

Specs.

0x000000000 R 0x000000000 R 0x000000080 R 0x00000000 R 0x00100000 R

last request if for a different row  $\rightarrow$  issue P

(1)

Test

Plan

#### Example: Read-to-Precharge Constraint

### Configurability

#### Syntax

- Addr. length

- Output syntax

- Transaction size

- Number of requests

#### Address mapping

- Row mask

- Column mask

- Rank mask

- Bank mask

- Channel mask

#### Patterns

- Transaction:

- rd, wr, random, sw%

- Row:

- hit, conflict, random, linear, locality %, custom

- Rank/ Bank/ Channel:

- Same, linear, random, interleave%

• ....

| Suite           | Description                                                                                                                                               |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| RegressionSuite | includes tests that cover all combinations of the configuration parameters                                                                                |

| PoliciesSuite   | includes tests that test most commonly used policies<br>of commodity memory controllers such as page<br>policies, address mapping and arbitration schemes |

| TimingSuite     | includes tests to detect any timing violations in most timing constraints                                                                                 |

#### Conclusion

- *MCXplore* is design-independent

- Two formal models at different granularities to capture MC behaviors

- A precise methodology to define test plans

- Validated state-of-the-art commercial MC policies

- Highlight interesting test patterns and use memory utilization as a golden metric

- Three test suites to validate and evaluate any new MC feature

- It is open-source!

- <u>https://git.uwaterloo.ca/caesr-pub/mcxplore</u>