## Predictable Cache Coherence for Multi-Core Real-Time Systems

Mohamed Hassan, **Anirudh M. Kaushik** and Hiren Patel RTAS 2017

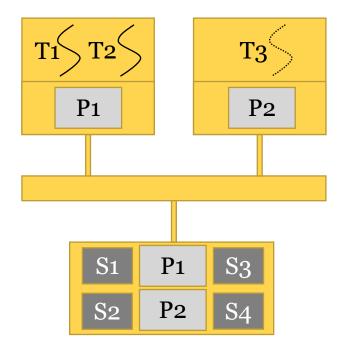

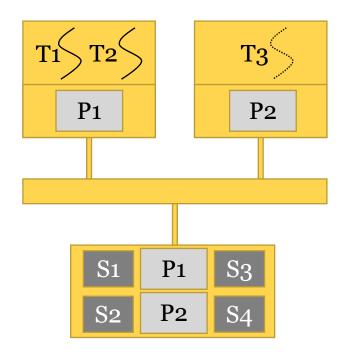

No caching of shared data [RTSS'09, RTNS'10]

- ✓ Simpler timing analysis

- **\*** Hardware support

- **★** Long execution time

No caching of shared data [RTSS'09, RTNS'10]

- ✓ Simpler timing analysis

- **\*** Hardware support

- **★** Long execution time

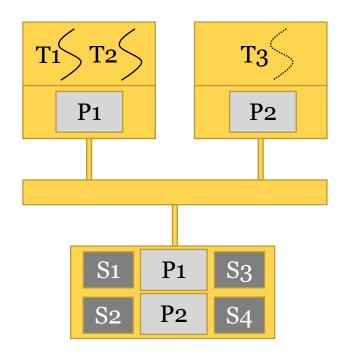

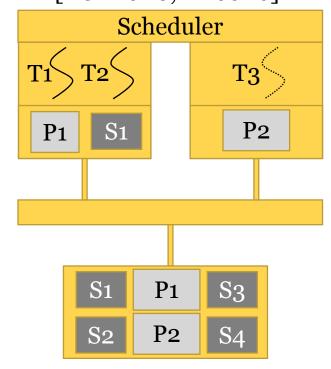

Task scheduling on shared data [ECRTS'10, RTSS'16]

- ✔ Private cache hits on shared data

- ✓ No hardware support

- **★** Limited multi-core parallelism

- **★** Changes to OS scheduler

No caching of shared data [RTSS'09, RTNS'10]

- ✓ Simpler timing analysis

- **★** Hardware support

- **★** Long execution time

Task scheduling on shared data [ECRTS'10, RTSS'16]

- ✓ Private cache hits on shared data

- ✓ No hardware support

- **★** Limited multi-core parallelism

- **★** Changes to OS scheduler

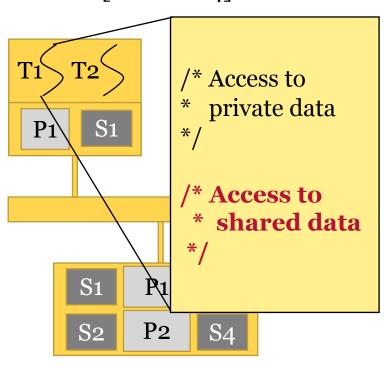

Software cache coherence [SAMOS'14]

- ✓ Private cache hits on shared data

- **★** Hardware support

- **X** Source code changes

No caching of shared data

[RTSS'09, RTNS'10]

Task scheduling on shared data

Software cache coherence

$\Gamma \cap \Lambda \Lambda \Gamma \cap \Omega^{1} \dots \Gamma$

- S1

P1

S3

S2

P2

S4

- ✓ Simpler timing analysis

- **\*** Hardware support

- **★** Long execution time

- S2 P2 S4

- ✓ Private cache hits on shared data

- ✓ No hardware support

- **★** Limited multi-core parallelism

- **★** Changes to OS scheduler

- ✓ Private cache hits on shared data

- **\*** Hardware support

- **X** Source code changes

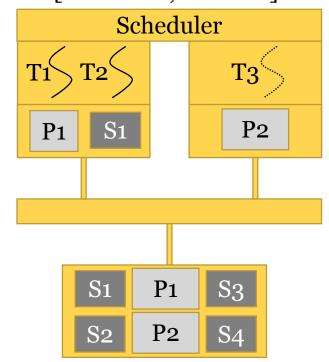

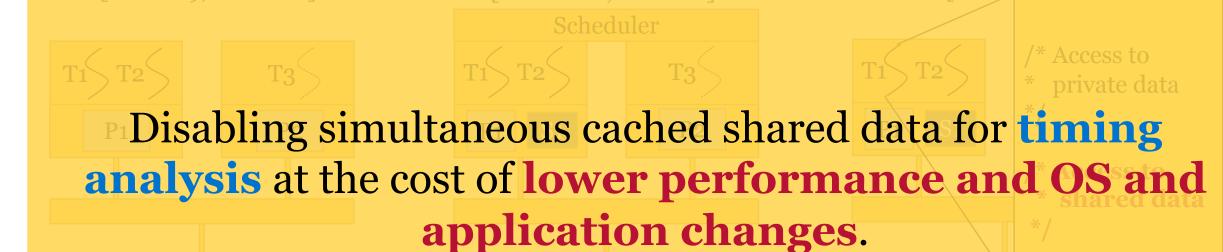

No caching of shared data

Task scheduling on shared data

Software cache coherence

[RISS 09, RINS 10]

[ECRTS'10, RTSS'16]

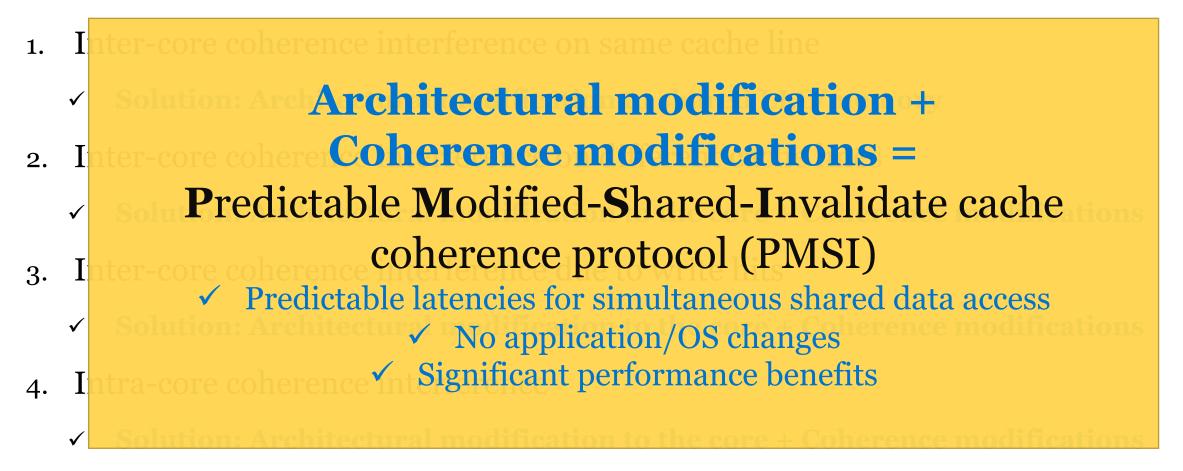

This work:

Allowing predictable simultaneous cached shared data

accesses through hardware cache coherence, and provide

significant performance improvements with no

changes to OS and applications.

- ✓ Simpler timing analysis

- **\*** Hardware support

- **★** Long execution time

- ✓ Private cache hits on shared data

- ✓ No hardware support

- **★** Limited multi-core parallelism

- **★** Changes to OS scheduler

- ✔ Private cache hits on shared data

- **\*** Hardware support

- **X** Source code changes

#### **Outline**

- Overview of hardware cache coherence

- Challenges of applying conventional hardware cache coherence on RT multi-core systems

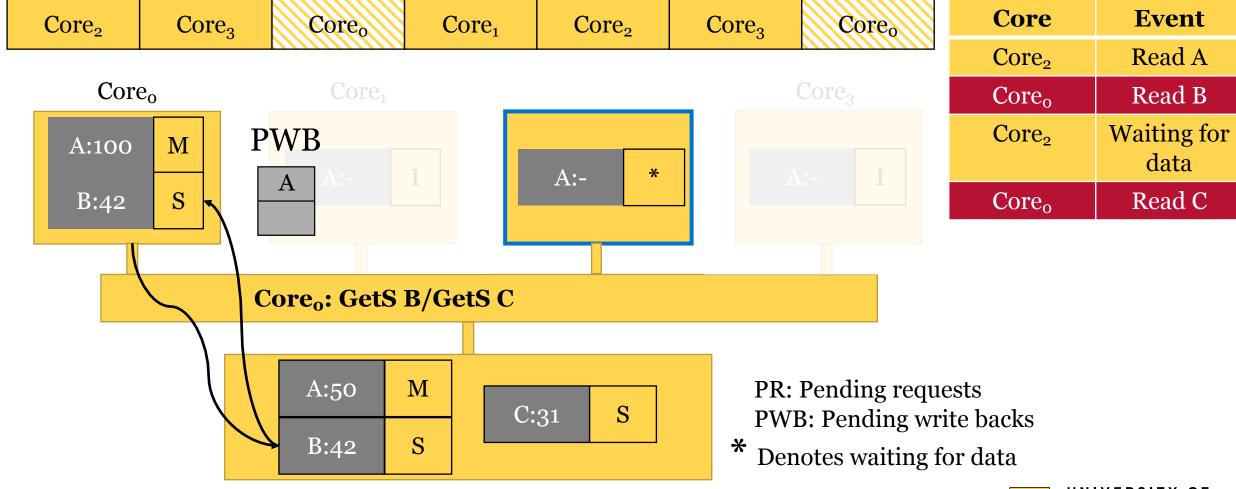

- Our solution: Predictable Modified-Shared-Invalid (PMSI) cache coherence protocol

- Latency analysis of PMSI

- Results

- Conclusion

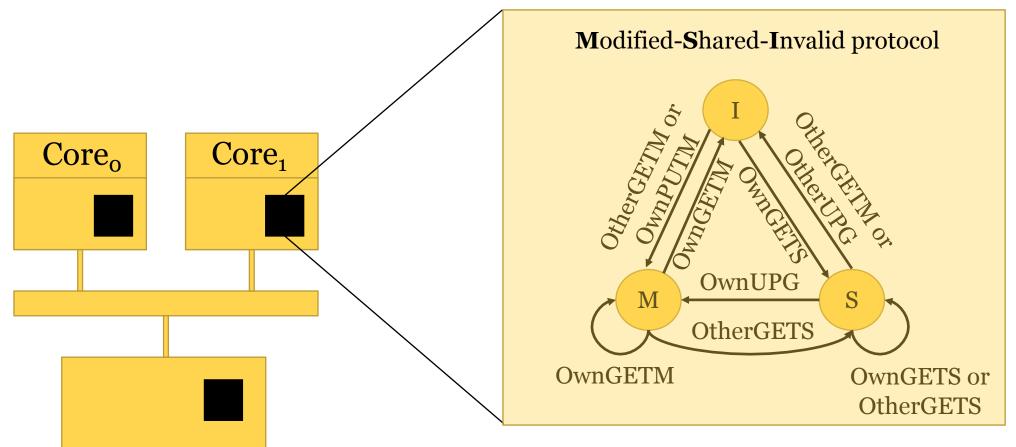

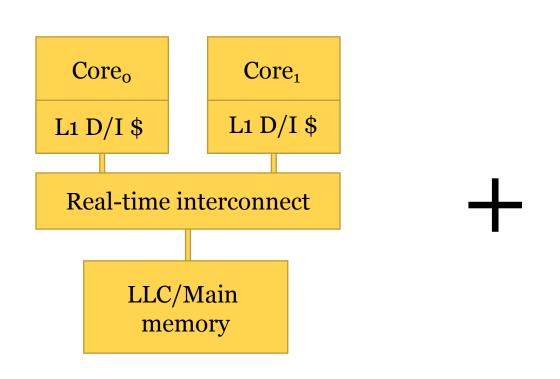

#### Overview of hardware cache coherence

**GETS:** Memory load

GETM/UPG: Memory store

**PUTM:** Replacement

#### Applying hardware cache coherence to multi-core RT systems

#### Applying hardware cache coherence to multi-core RT systems

Modified-Shared-Invalid protocol Multi-core RT system with predictable arbitration to shared components Well studied cache coherence protocol Predictable latencies for shared data accesses? OwnGETM OwnGETS or **OtherGETS**

#### Applying hardware cache coherence to multi-core RT systems

Modified-Shared-Invalid protocol Multi-core RT system with predictable arbitration to shared components Well studied cache coherence protocol Predictable latencies for shared data accesses? OwnGETM OwnGETS or **OtherGETS**

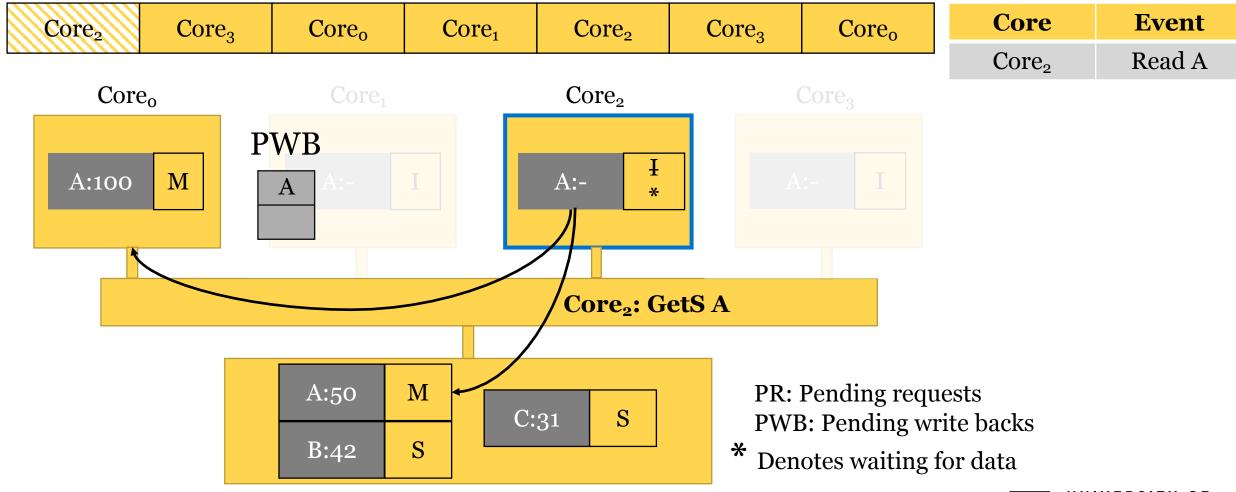

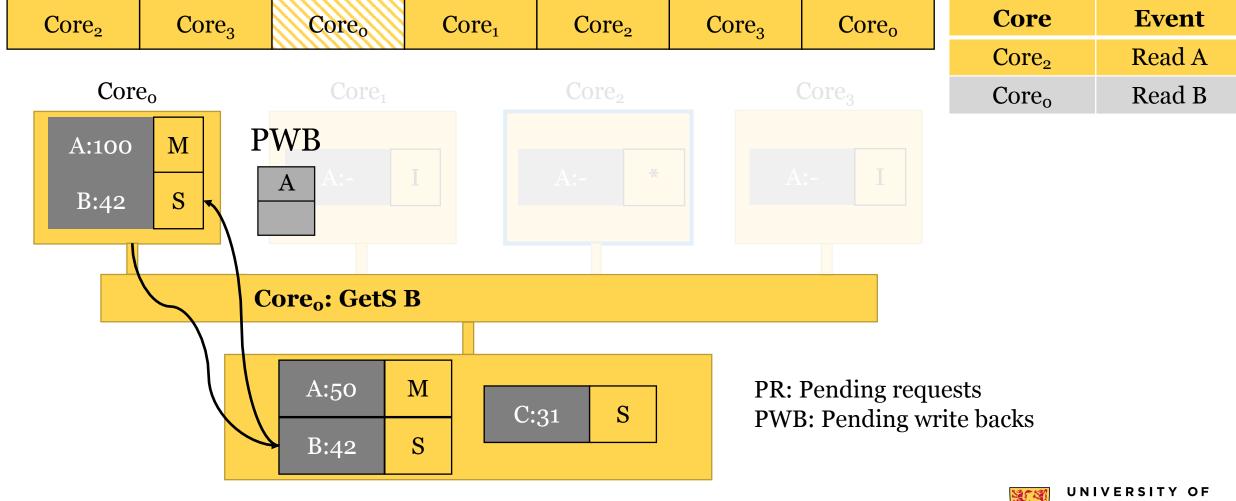

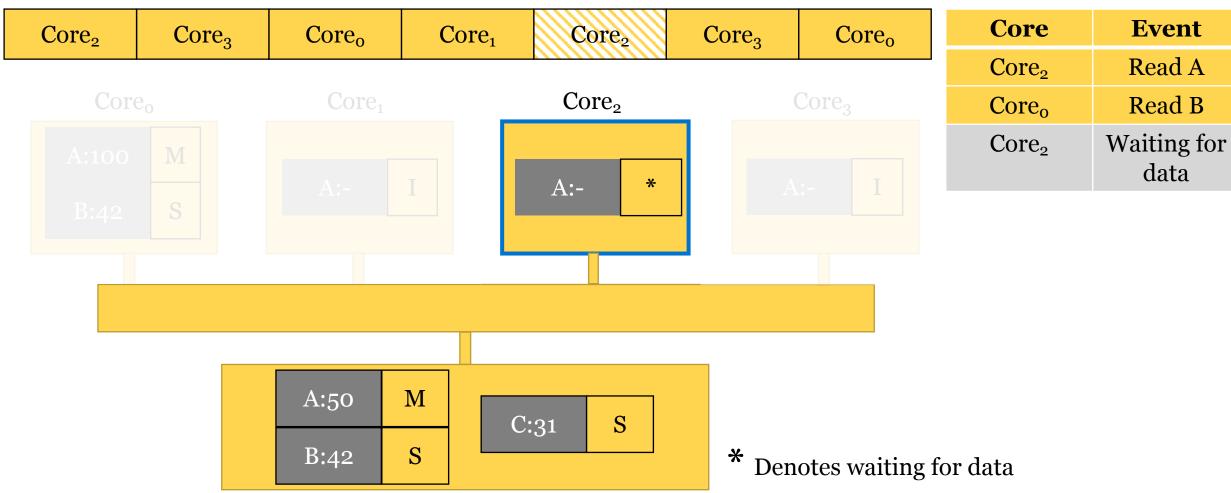

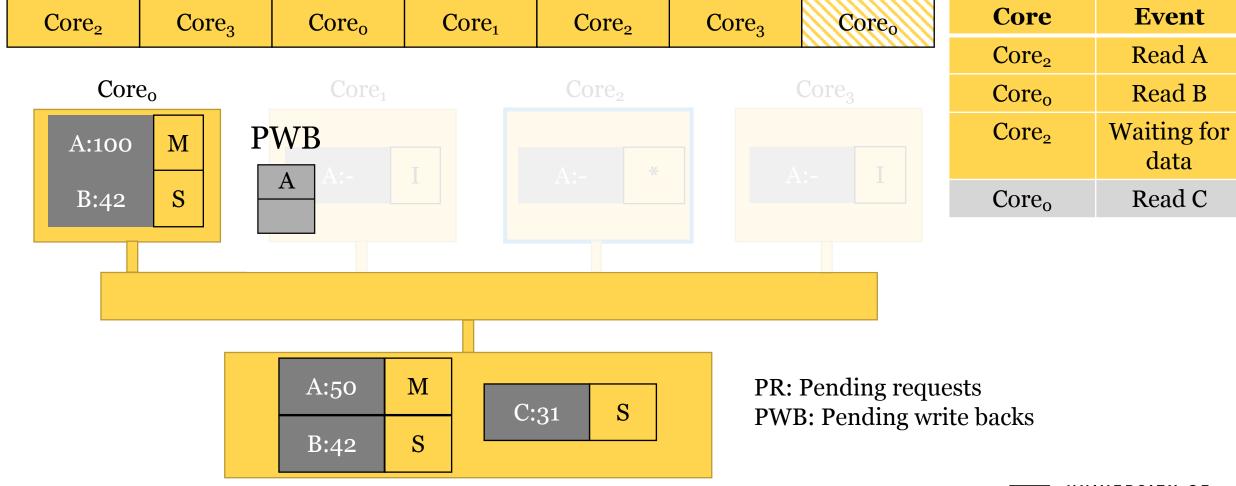

## Sources of unpredictable memory access latencies due to hardware cache coherence

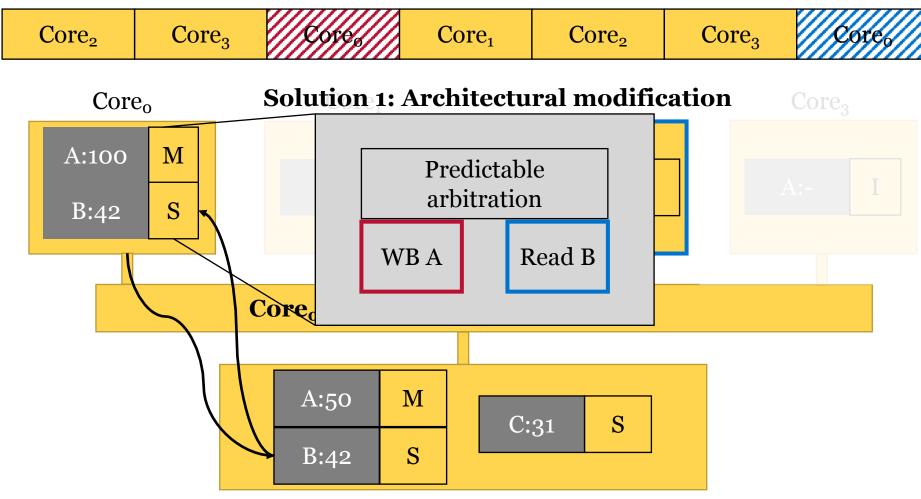

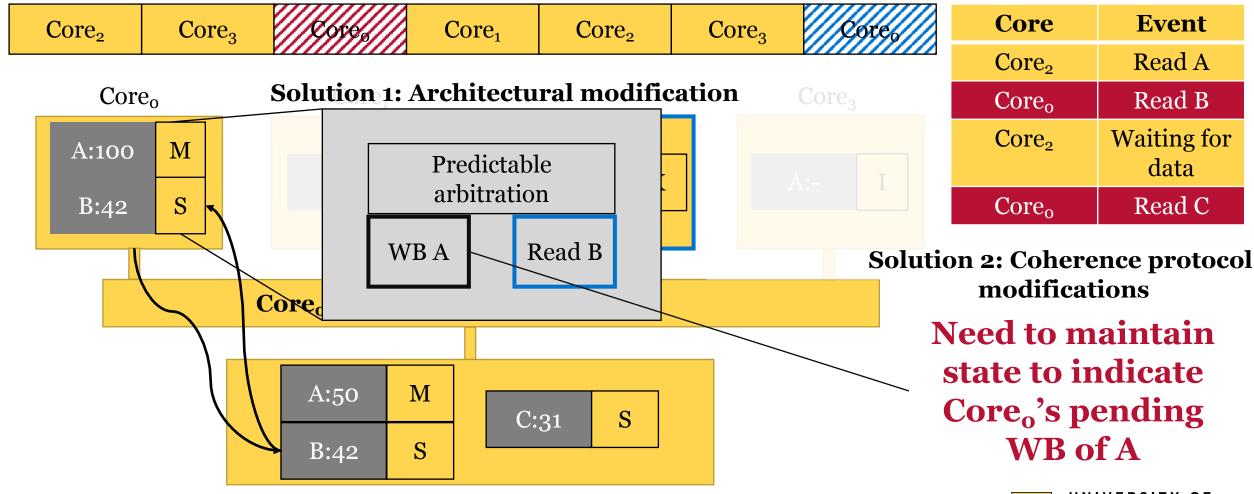

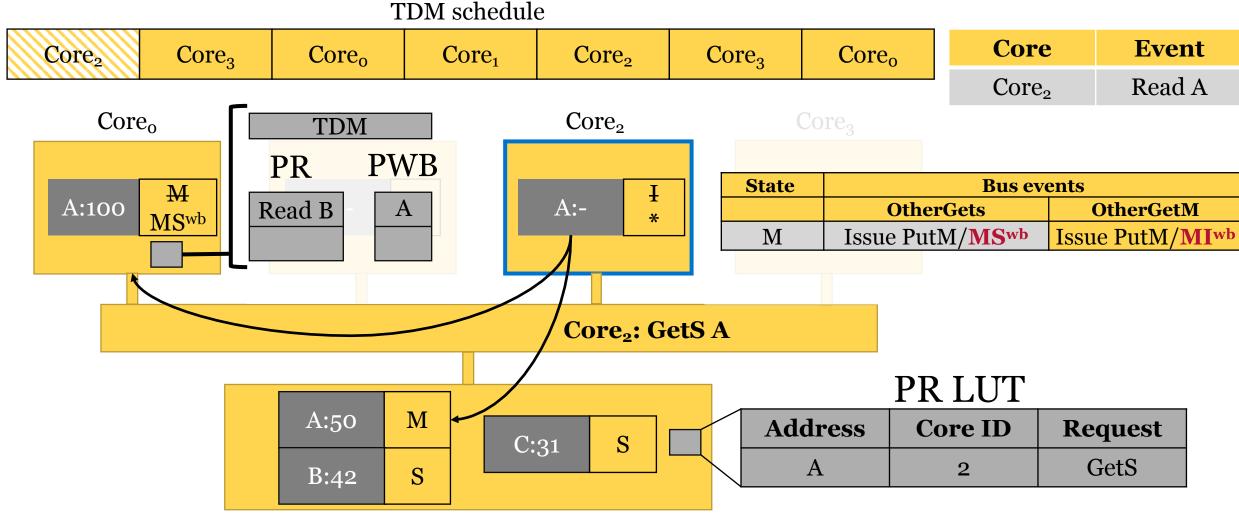

1. Inter-core coherence interference on same cache line

2. Inter-core coherence interference on different cache lines

3. Inter-core coherence interference due to write hits

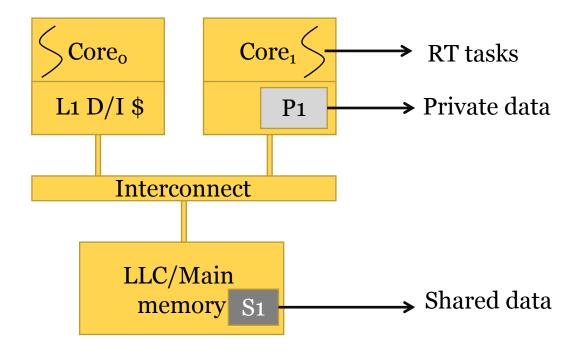

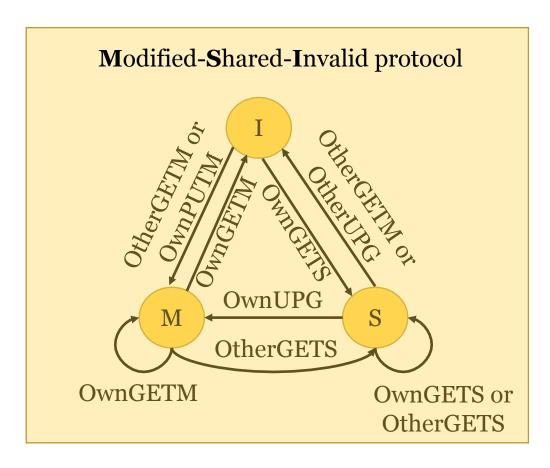

## System model

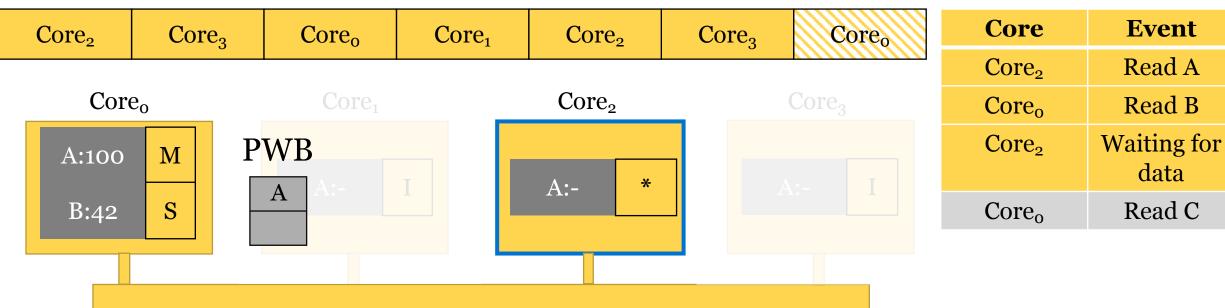

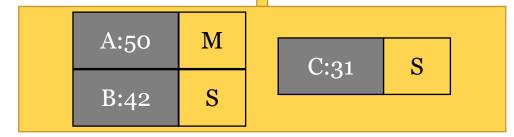

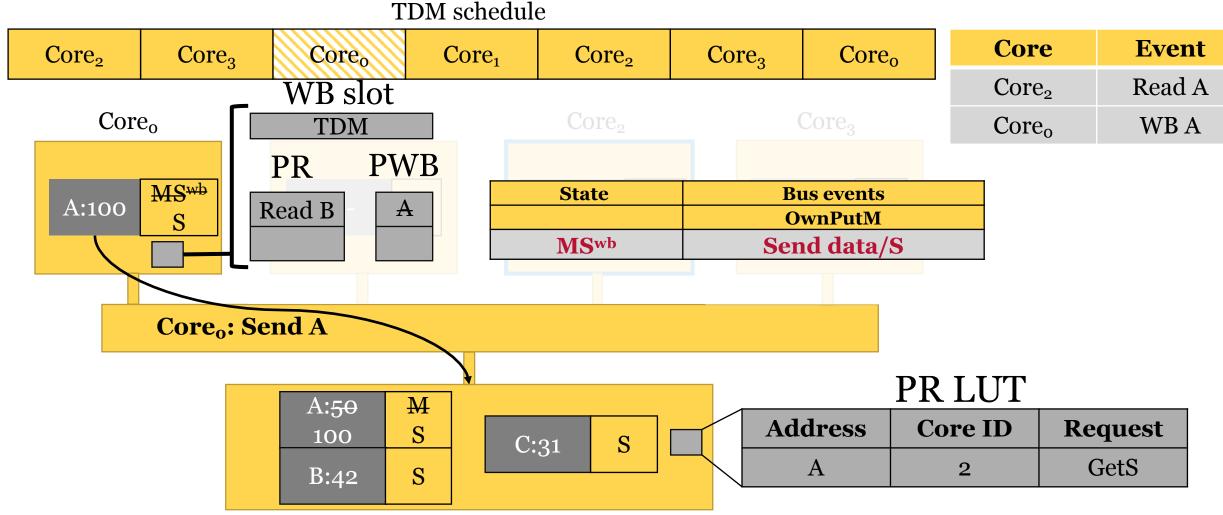

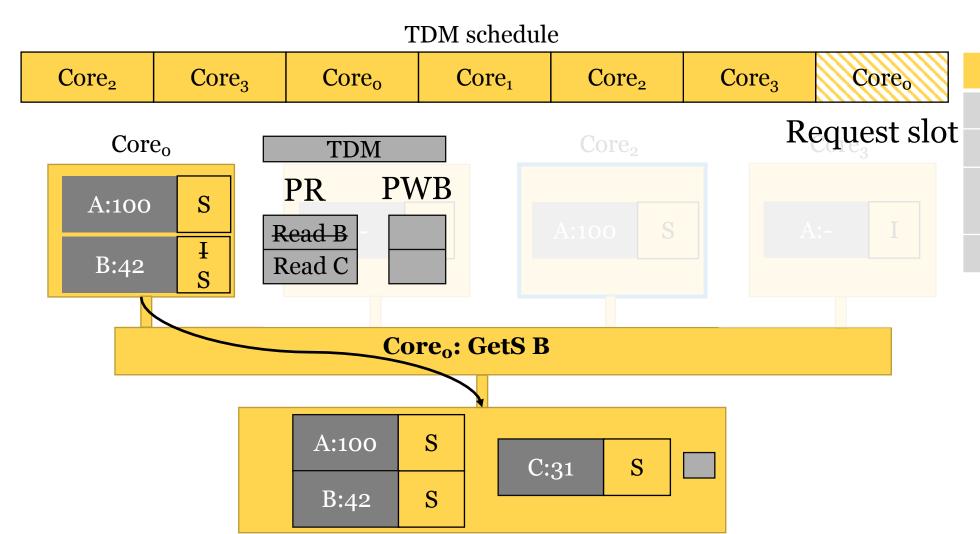

TDM schedule

**Event**

data

TDM schedule

#### **\*** Unbounded latency for Core<sub>2</sub>

\* Denotes waiting for data

| Core     | Event            |

|----------|------------------|

| $Core_2$ | Read A           |

| $Core_o$ | Read B           |

| $Core_2$ | Waiting for data |

| $Core_o$ | Read C           |

| Core              | Event            |

|-------------------|------------------|

| $Core_2$          | Read A           |

| Core <sub>o</sub> | Read B           |

| $Core_2$          | Waiting for data |

| Core <sub>o</sub> | Read C           |

## Sources of unpredictable memory access latencies due to cache coherence

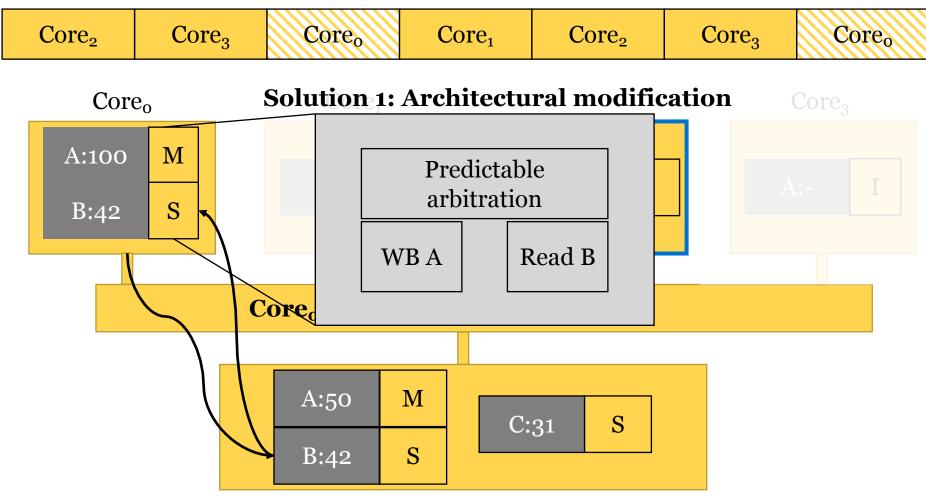

## PMSI cache coherence protocol: Protocol modifications

| State                               | Core events |                                   |             | Bus events          |        |         |           |                                      |              |               |

|-------------------------------------|-------------|-----------------------------------|-------------|---------------------|--------|---------|-----------|--------------------------------------|--------------|---------------|

|                                     | Load        | Store                             | Replacement | OwnData             | OwnUpg | OwnPutM | OtherGetS | OtherGetM                            | Other<br>Upg | Other<br>PutM |

|                                     | Issue       |                                   |             |                     |        |         |           |                                      |              |               |

| I                                   | GetS/ISd    | Issue GetM/IM <sup>d</sup>        | X           | X                   | X      | X       | N/A       | N/A                                  | N/A          | N/A           |

| S                                   | Hit         | Issue Upg/ <b>SM</b> <sup>w</sup> | X           | N/A                 | X      | X       | N/A       | I                                    | I            | X             |

|                                     |             |                                   | Issue       |                     |        |         | Issue     | Issue                                |              |               |

| M                                   | Hit         | Hit                               | PutM/MIwb   | X                   | X      | X       | PutM/MSwb | PutM/MIwb                            | X            | X             |

| IS <sup>d</sup>                     | X           | X                                 | X           | Read/S              | X      | X       | N/A       | ISdI                                 | $IS^{d}I$    | N/A           |

| $\mathbf{I}\mathbf{M}^{\mathrm{d}}$ | X           | X                                 | X           | Write/S             | X      | X       | $IM^dS$   | $\mathrm{IM}^{\mathrm{d}}\mathrm{I}$ | X            | N/A           |

| IM <sup>d</sup> I                   | X           | X                                 | X           | Write/MIwb          | X      | X       | N/A       | X                                    | X            | N/A           |

| IS <sup>d</sup> I                   | X           | X                                 | X           | Read/I              | X      | X       | N/A       | X                                    | X            | N/A           |

| IM <sup>d</sup> S                   | X           | X                                 | X           | Write/ <b>MS</b> wb | X      | X       | N/A       | X                                    | X            | N/A           |

|                                     |             |                                   |             |                     | Store/ |         |           |                                      |              |               |

| <b>SM</b> w                         | X           | X                                 | X           | N/A                 | M      | X       | N/A       | I                                    | I            | X             |

|                                     |             |                                   |             |                     |        | Send    |           |                                      |              |               |

| MIwb                                | Hit         | Hit                               | N/A         | X                   | X      | data/I  | N/A       | N/A                                  | X            | X             |

|                                     |             |                                   |             |                     |        | Send    |           |                                      |              |               |

| <b>MS</b> wb                        | Hit         | Hit                               | MIwb        | X                   | X      | data/S  | N/A       | MIwb                                 | X            | X             |

## PMSI cache coherence protocol: Protocol modifications

| State                  | e Core events |                            |             | Bus events          |        |         |           |                                      |                                               |               |

|------------------------|---------------|----------------------------|-------------|---------------------|--------|---------|-----------|--------------------------------------|-----------------------------------------------|---------------|

|                        | Load          | Store                      | Replacement | OwnData             | OwnUpg | OwnPutM | OtherGetS | OtherGetM                            | Other<br>Upg                                  | Other<br>PutM |

|                        | Issue         |                            |             |                     |        |         |           |                                      |                                               |               |

| I                      | GetS/ISd      | Issue GetM/IM <sup>d</sup> | X           | X                   | X      | X       | N/A       | N/A                                  | N/A                                           | N/A           |

| S                      | Hit           | Issue Upg/SMw              | X           | N/A                 | X      | X       | N/A       | I                                    | I                                             | X             |

|                        |               |                            | Issue       |                     |        |         | Issue     | Issue                                |                                               |               |

| M                      | Hit           | Hit                        | PutM/MIwb   | X                   | X      | X       | PutM/MSwb | PutM/MIwb                            | X                                             | X             |

| IS <sup>d</sup>        | X             | X                          | X           | Read/S              | X      | X       | N/A       | ISdI                                 | $\mathbf{I}\mathbf{S}^{\mathrm{d}}\mathbf{I}$ | N/A           |

| IM <sup>d</sup>        | X             | X                          | X           | Write/S             | X      | X       | $IM^dS$   | $\mathrm{IM}^{\mathrm{d}}\mathrm{I}$ | X                                             | N/A           |

| IM <sup>d</sup> I      | X             | X                          | X           | Write/MIwb          | X      | X       | N/A       | X                                    | X                                             | N/A           |

| ISdI                   | X             | X                          | X           | Read/I              | X      | X       | N/A       | X                                    | X                                             | N/A           |

| IM <sup>d</sup> S      | X             | X                          | X           | Write/ <b>MS</b> wb | X      | X       | N/A       | X                                    | X                                             | N/A           |

|                        |               |                            |             |                     | Store/ |         |           |                                      |                                               |               |

| <b>SM</b> <sup>w</sup> | X             | X                          | X           | N/A                 | M      | X       | N/A       | I                                    | Ι                                             | X             |

|                        |               |                            |             |                     |        | Send    |           |                                      |                                               |               |

| MIwb                   | Hit           | Hit                        | N/A         | X                   | X      | data/I  | N/A       | N/A                                  | X                                             | X             |

|                        |               |                            |             |                     |        | Send    |           |                                      |                                               |               |

| <b>MS</b> wb           | Hit           | Hit                        | MIwb        | X                   | X      | data/S  | N/A       | MIwb                                 | X                                             | X             |

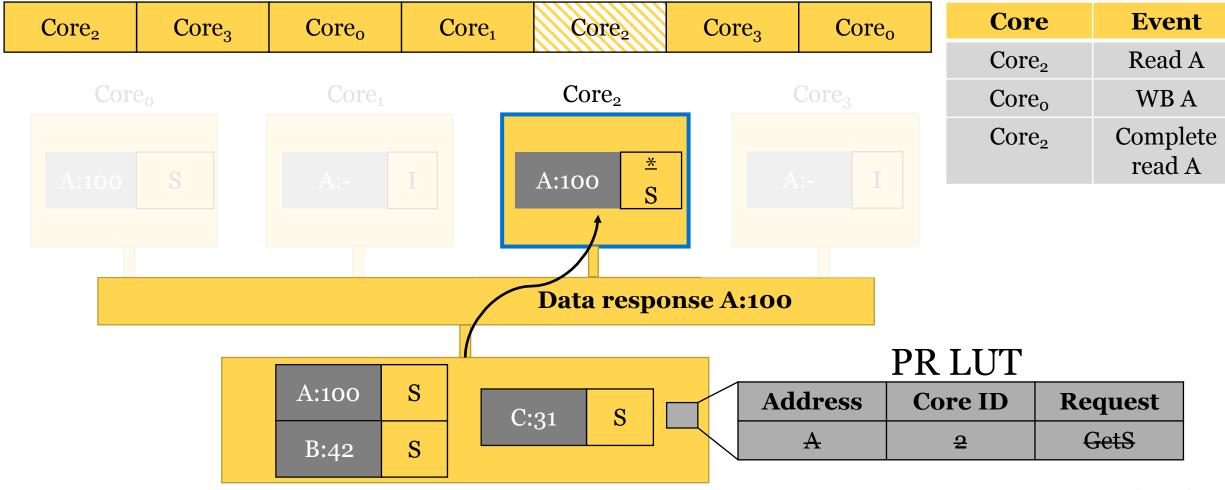

| Core              | Event              |

|-------------------|--------------------|

| $Core_2$          | Read A             |

| $Core_o$          | WB A               |

| $Core_2$          | Complete<br>read A |

| Core <sub>o</sub> | Read B             |

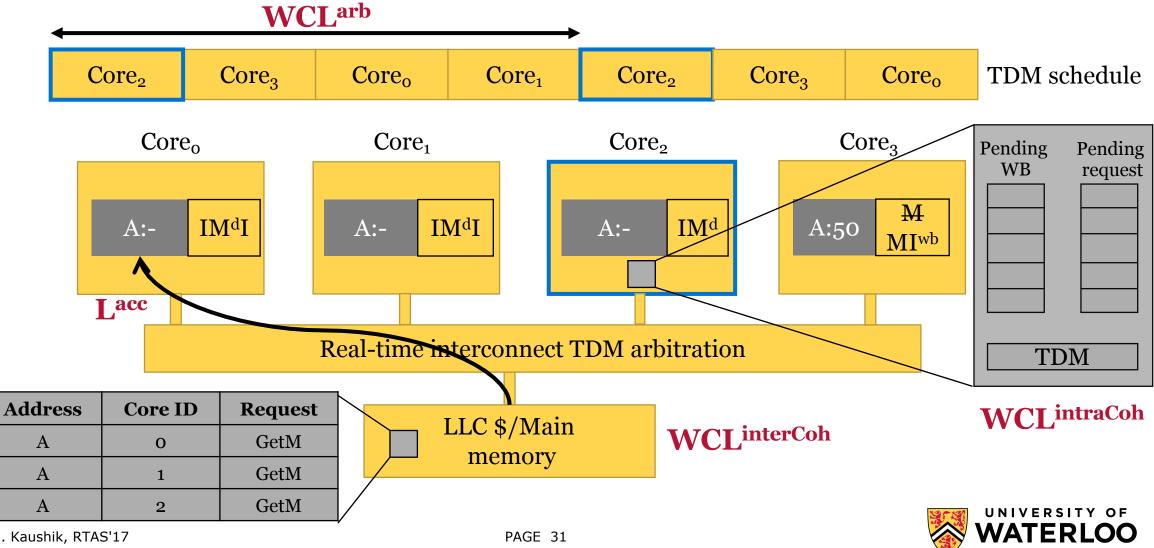

## **Latency analysis of PMSI**

N: Number of cores

## **Latency analysis of PMSI**

WCL of memory request

$$L^{acc} + \\ WCL^{arb} (\alpha N) + \\ WCL^{intraCoh} (\alpha N) + \\ WCL^{interCoh} (\alpha N^2)$$

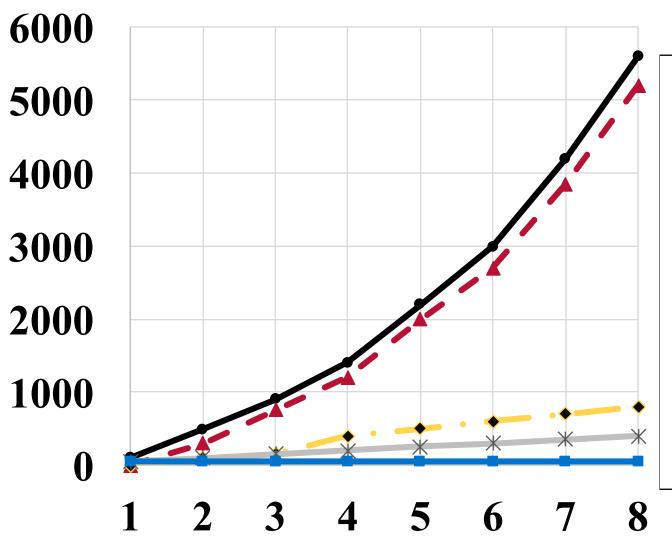

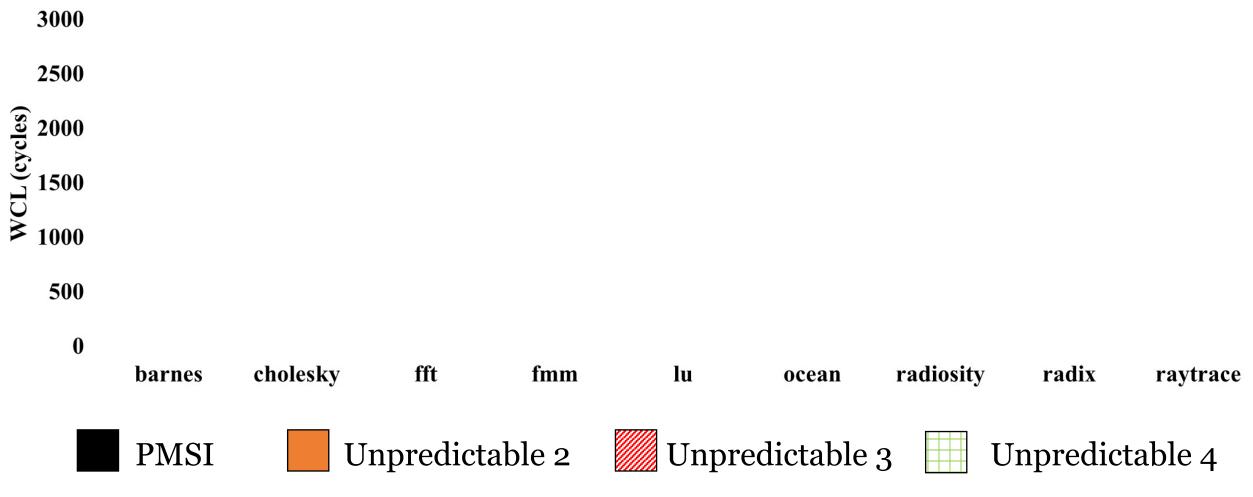

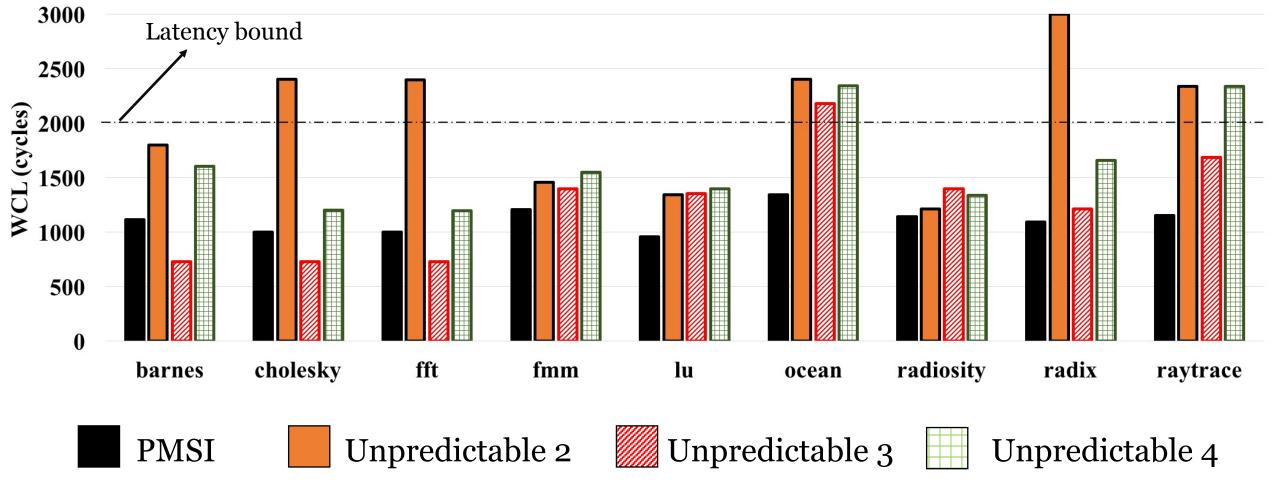

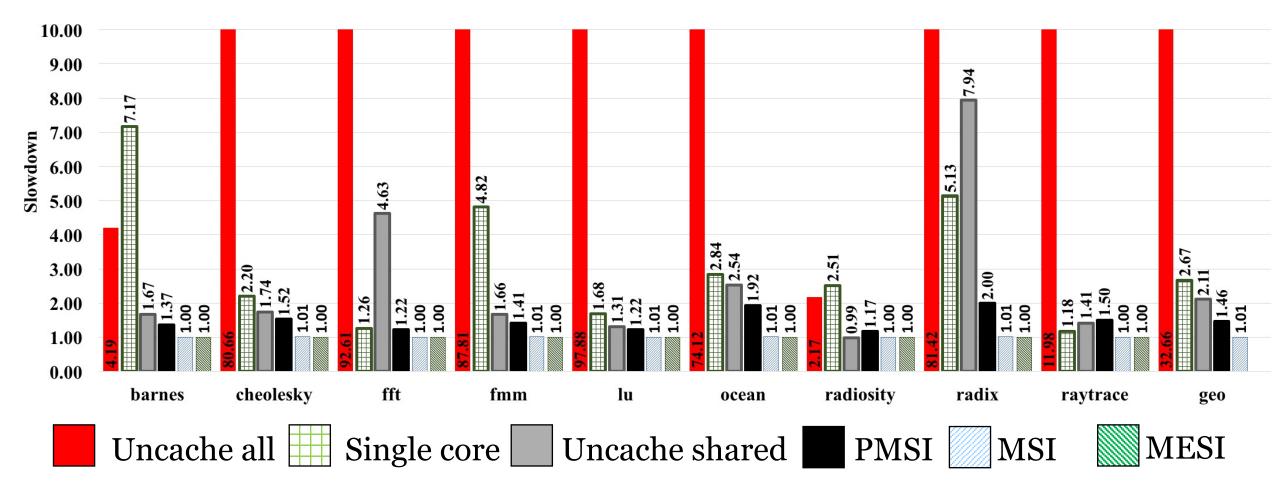

#### **Results**

- Cycle accurate Gem5 simulator

- 2, 4, 8 cores, 16KB direct mapped private L1-D/I caches

- In-order cores, 2GHz operating frequency

- TDM bus arbitration with slot width = 50 cycles

- Benchmarks: SPLASH-2, synthetic benchmarks to stress worst-case scenarios

- Simulation framework available at <a href="https://git.uwaterloo.ca/caesr-pub/pmsi">https://git.uwaterloo.ca/caesr-pub/pmsi</a>

## Results: Observed worst case latency per request

## Results: Observed worst case latency per request

### Results: Observed worst case latency per request

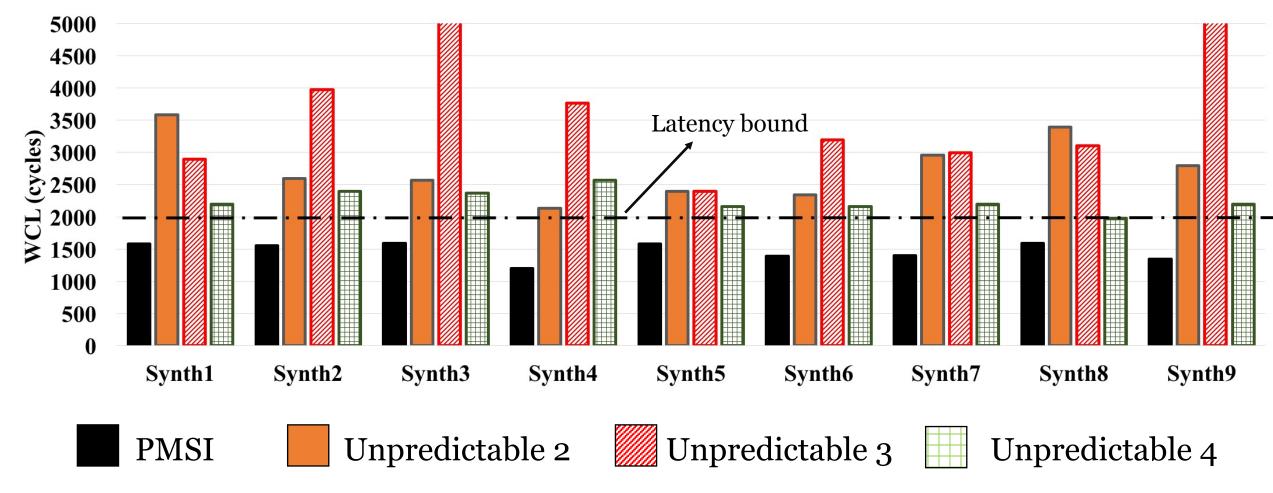

#### Results: Slowdown relative to MESI cache coherence

#### Results: Slowdown relative to MESI cache coherence

#### **Conclusion**

- Enumerate sources of unpredictability when applying conventional hardware cache coherence on multi-core real-time systems

- Propose PMSI cache coherence that allows predictable simultaneous shared data accesses with no changes to application/OS

- Hardware overhead of PMSI is ~ 128 bytes

- WCL of memory access with PMSI  $\alpha$  square of number of cores ( $\alpha$  N<sup>2</sup>)

- PMSI outperforms prior techniques for handling shared data accesses (upto 4x improvement over uncache-shared), and suffers on average 46% slowdown compared to conventional MESI cache coherence protocol

# WATER LOO

THANK YOU & QUESTIONS?