#### Managing DRAM Interference in Mixed Criticality Embedded Systems

#### **Mohamed Hassan**

## Outline

- Emerging Systems No longer solely hosting isolated safety-critical tasks

- Execute tasks with different criticalities

- Criticality  $\alpha$  consequences of failure to meet requirements

#### **High-criticality tasks**

Airbag Control Unit (ACU)

2

MOTIVATION

- Anti-lock Braking System (ABS)

- Engine Control Unit (ECU)

#### Mixed Criticality Systems

- Emerging Systems No longer solely hosting isolated safety-critical tasks

- Execute tasks with different criticalities

- Criticality  $\alpha$  consequences of failure to meet requirements

MOTIVATION

# Mixed Criticality Systems

## Mixed Criticality Systems

#### MOTIVATION

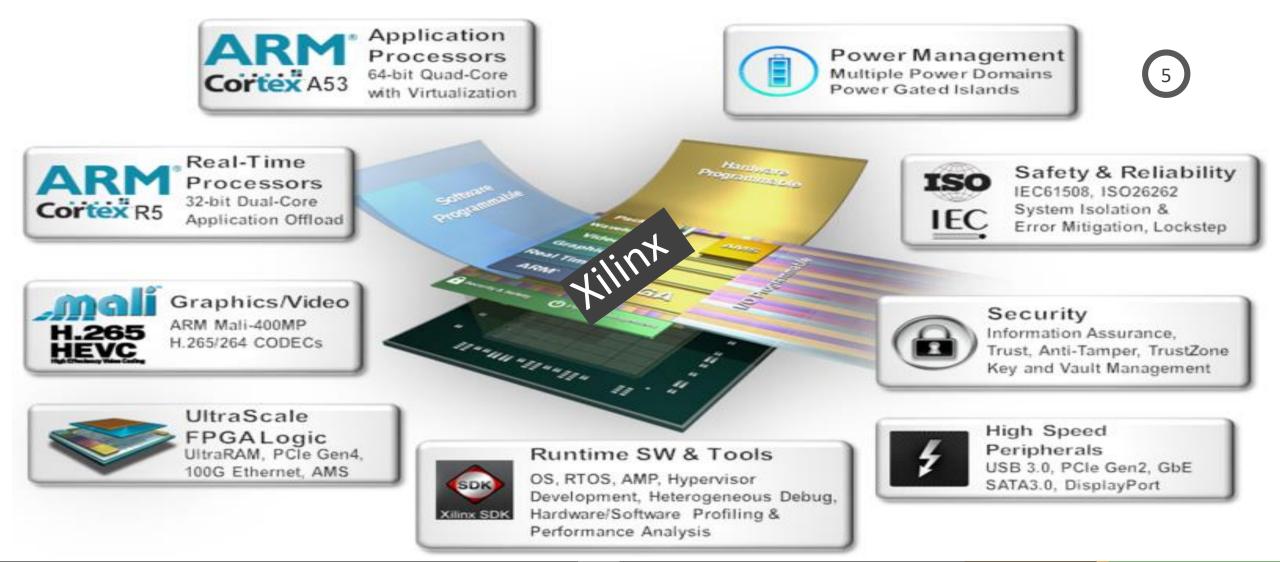

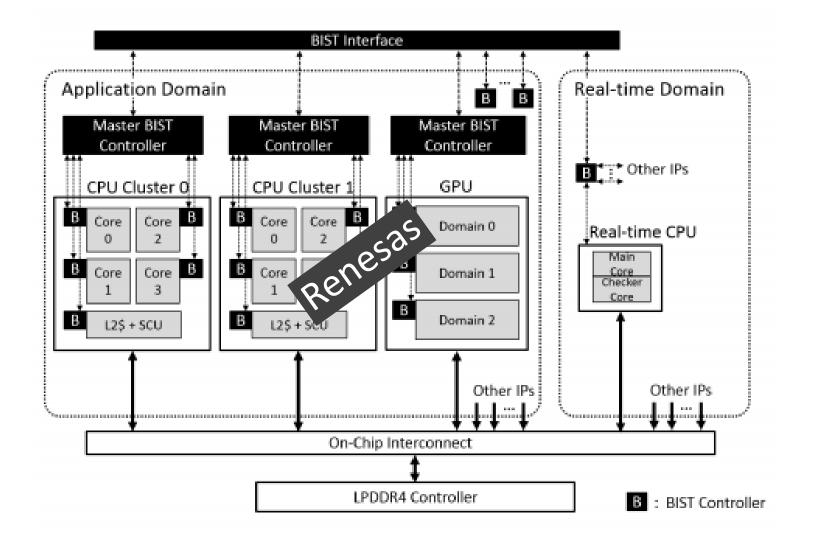

Heterogenous MPSoCs with Real-time Processors

Heterogenous MPSoCs with Real-time Processors

#### MOTIVATION

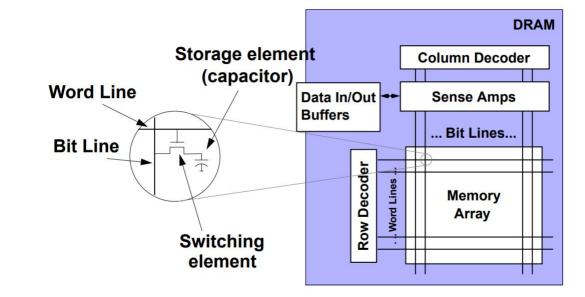

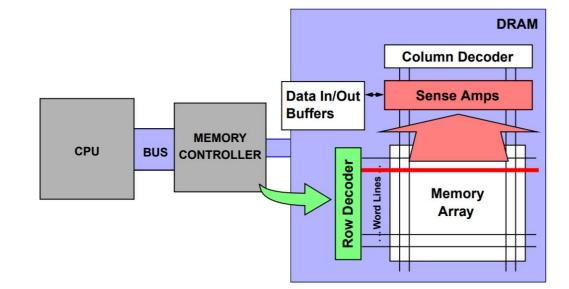

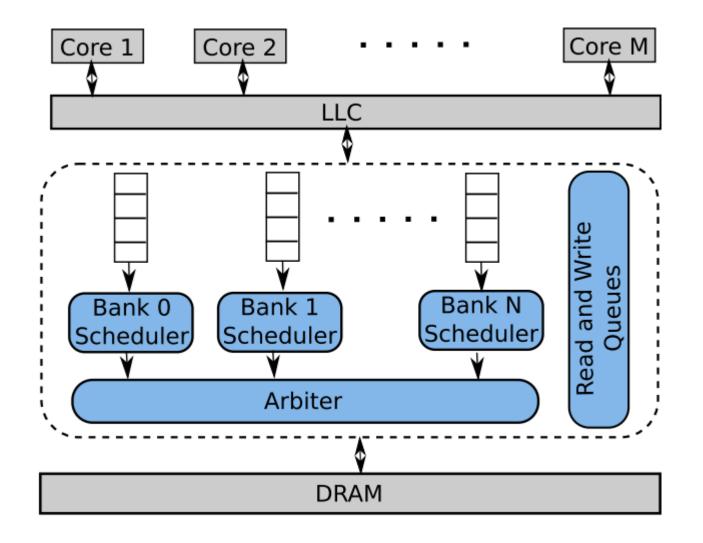

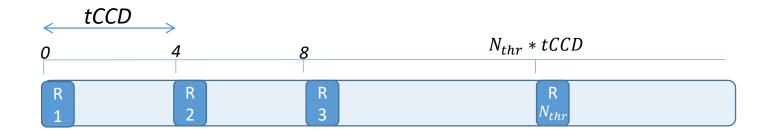

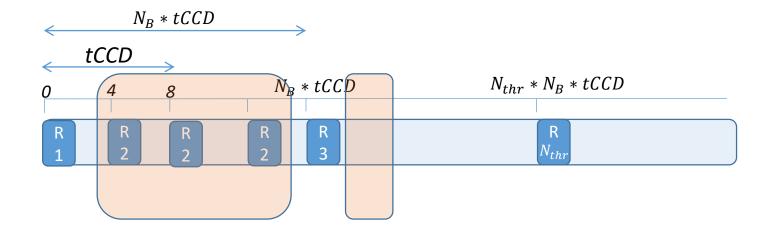

• DRAM Consists of multiple banks

## Background

- DRAM Consists of multiple banks

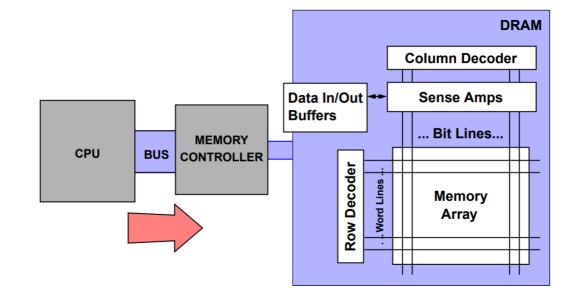

- The memory controller (MC) manages accesses to DRAM

- DRAM Consists of multiple banks

- The memory controller (MC) manages accesses to DRAM

- A request in general consists of:

- ACTIVATE command:

- Bring data row from cells into sense amplifiers

- DRAM Consists of multiple banks

- The memory controller (MC) manages accesses to DRAM

- A request in general consists of:

- ACTIVATE command:

- Bring data row from cells into sense amplifiers

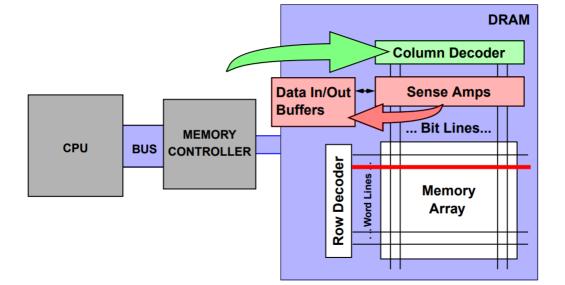

- RD/WR commands:

- To read/write from specific columns in the sense amplifiers

- DRAM Consists of multiple banks

- The memory controller (MC) manages accesses to DRAM

- A request in general consists of:

- ACTIVATE command:

- Bring data row from cells into sense amplifiers

- RD/WR commands:

- To read/write from specific columns in the sense amplifiers

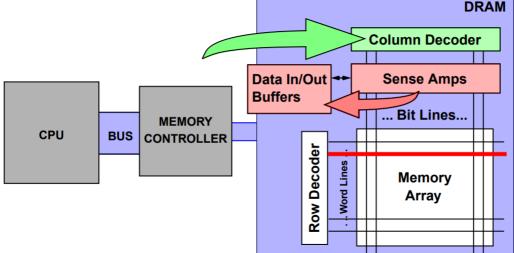

- PRECHARGE command:

- to write back a previous row in the sense amplifiers before bringing the new one

- DRAM Consists of multiple banks

- The memory controller (MC) manages accesses to DRAM

- A request in general consists of:

- ACTIVATE command:

- Bring data row from cells into sense amplifiers

- RD/WR commands:

- To read/write from specific columns in the sense amplifiers

- PRECHARGE command:

- to write back a previous row in the sense amplifiers before bringing the new one

6

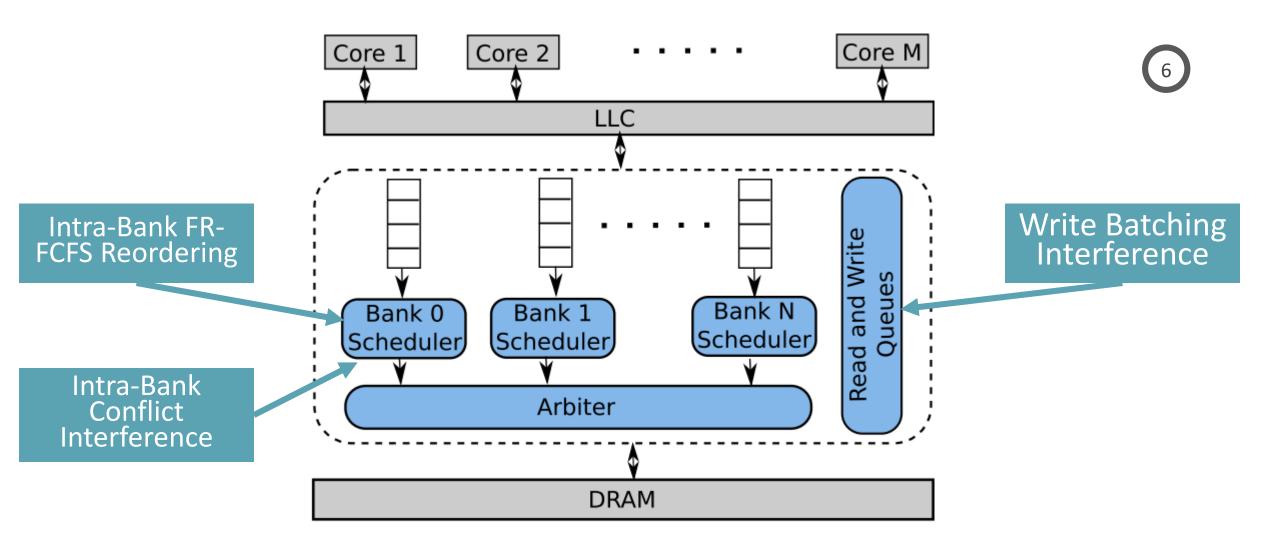

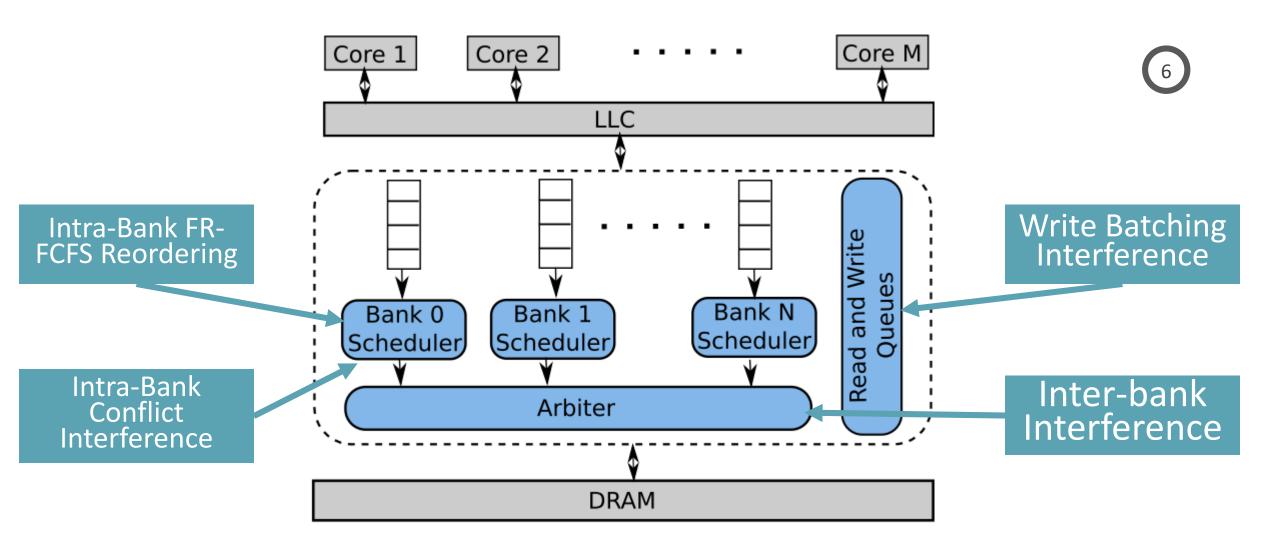

#### Background: Memory Controller

DRAM

6)

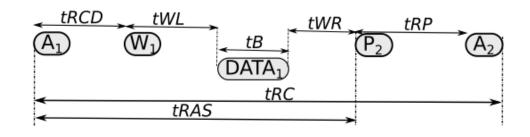

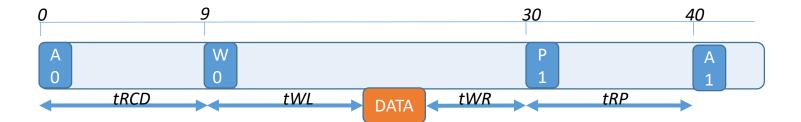

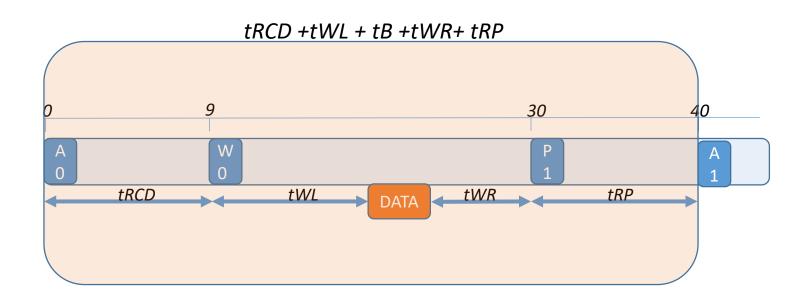

## **DRAM Delay Components**

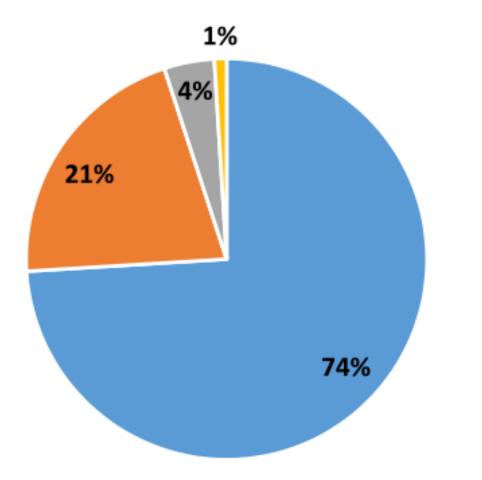

#### This paper:

We study the effect of the largest two components in a mixed criticality system

We derive both WCD bounds for critical cores and theoretical BW for non-critical cores

## **DRAM Delay Components**

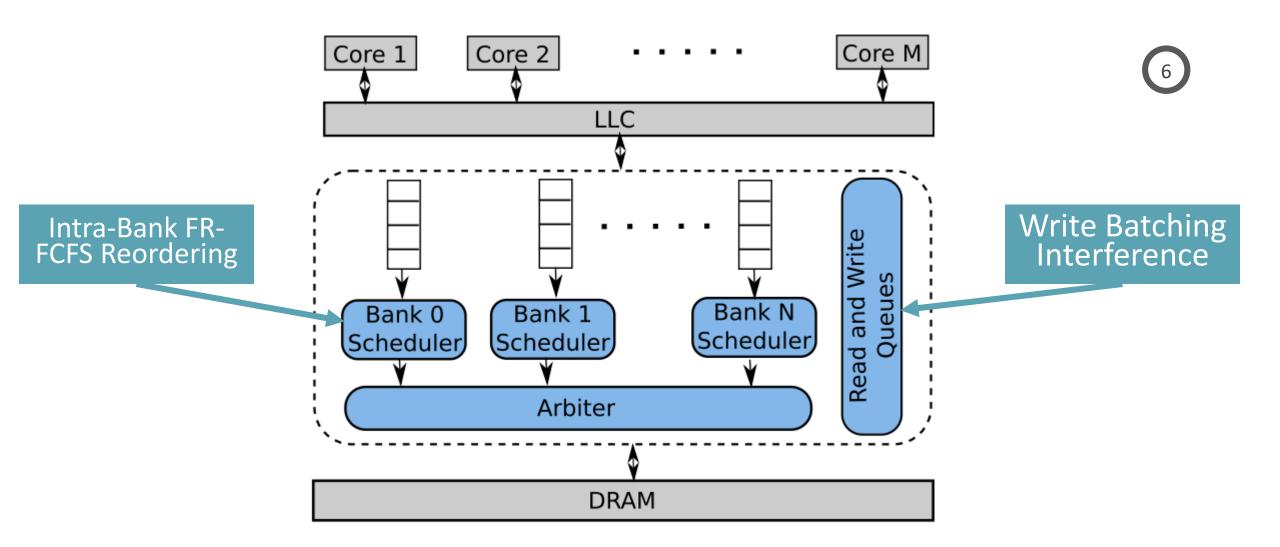

### FR-FCFS WCD

### FR-FCFS WCD

#### 6

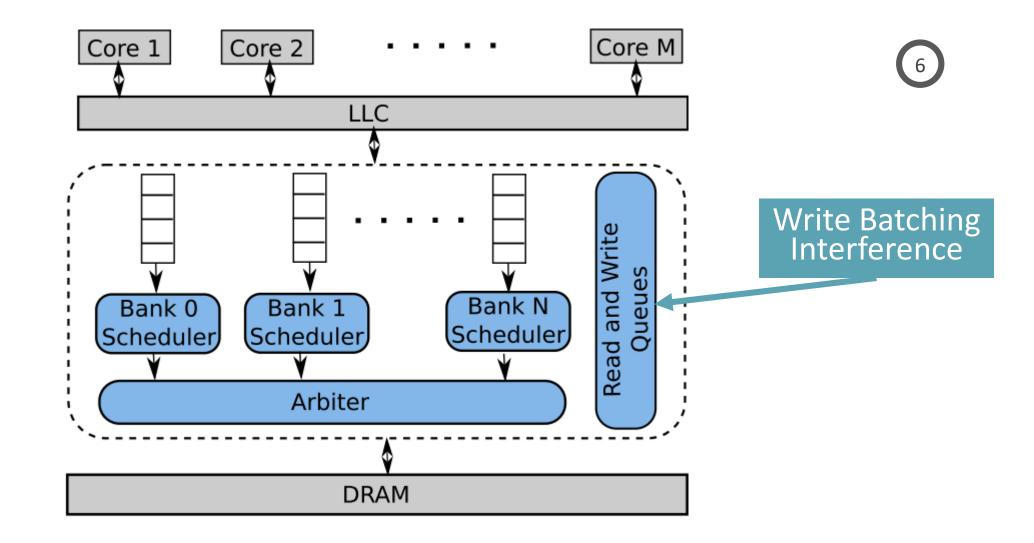

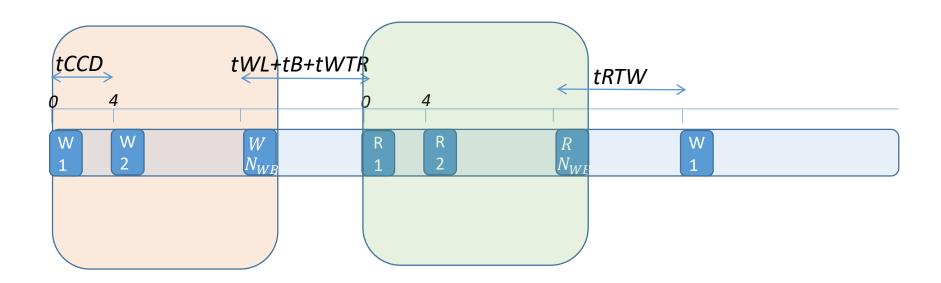

## Write Batching WCD

6

## Write Batching WCD

|  |  | 1 | 3 |

|--|--|---|---|

|  |  |   |   |

| proc       | 2 Processors<br>1 OOO and 1 in-order pipeline<br>a private 16KB L1<br>a shared 1MB L2 cache |  |

|------------|---------------------------------------------------------------------------------------------|--|

| DRAM       | DDR3-1600                                                                                   |  |

| Benchmarks | Latency and BW benchmarks                                                                   |  |

## **Evaluation Setup**

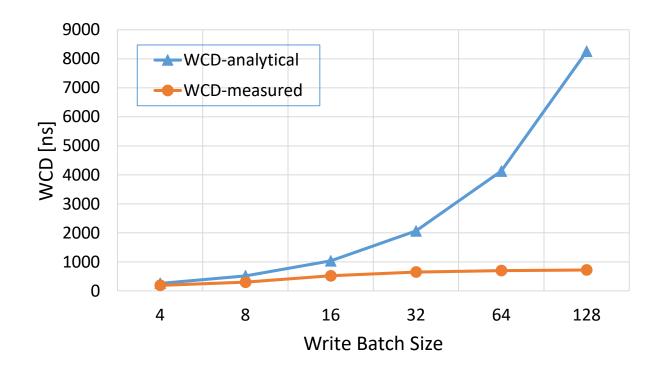

## Write Batching WCD

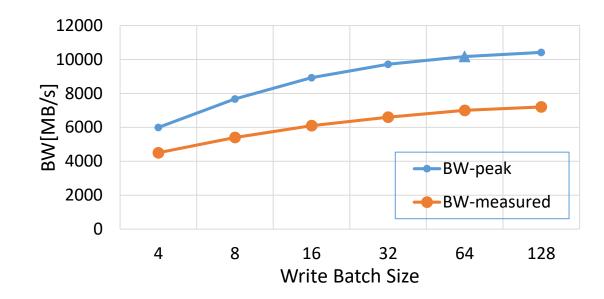

## Write Batching BW

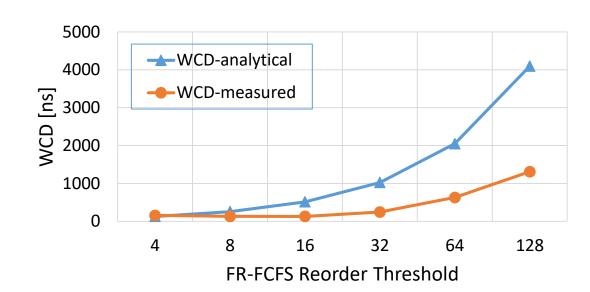

## FR-FCFS WCD

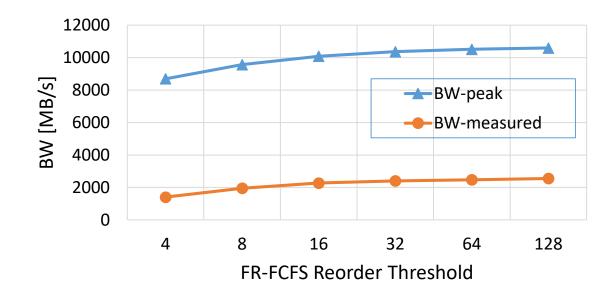

## FR-FCFS BW

#### Main Lessons:

- 1. We investigate the major sources of memory interference in COTS architectures upon deploying mixed criticality systems.

- 2. We identified two main contributors to this interference:

- Write batching and FR-FCFS arbitration.

- 3. Although theoretically increasing the amount of reordering done helps increasing the system peak BW, after certain point there are diminishing returns in practice

- 4. such increase also significantly increases worst-case delays

- Reaching a compromise point between BW and WCD to meet all requirements of MCS is the potential direction to explore. Such point will be application-dependent.

- 6. We provide analytical equations as well as experimental evaluation to help designers deciding this point

#### Main Lessons:

- 1. We investigate the major sources of memory interference in COTS architectures upon deploying mixed criticality systems.

- 2. We identified two main contributors to this interference:

- Write batching and FR-FCFS arbitration.

- 3. Although theoretically increasing the amount of reordering done helps increasing the system peak BW, after certain point there are diminishing returns in practice

- 4. such increase also significantly increases worst-case delays

- Reaching a compromise point between BW and WCD to meet all requirements of MCS is the potential direction to explore. Such point will be application-dependent.

- 6. We provide analytical equations as well as experimental evaluation to help designers deciding this point