# A Multiple-FPGA Parallel Computing Architecture for Real-time Simulation of Deformable Objects

# A MULTIPLE-FPGA PARALLEL COMPUTING ARCHITECTURE FOR REAL-TIME SIMULATION OF DEFORMABLE OBJECTS

BY

### SEYED BEHZAD MAHDAVIKHAH MEHRABAD, B.Sc.

### A THESIS

SUBMITTED TO THE DEPARTMENT OF ELECTRICAL & COMPUTER ENGINEERING

AND THE SCHOOL OF GRADUATE STUDIES

OF MCMASTER UNIVERSITY

IN PARTIAL FULFILMENT OF THE REQUIREMENTS

FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

© Copyright by Seyed Behzad Mahdavikhah Mehrabad, Aug 2009 All Rights Reserved Master of Applied Science (2009) (Electrical & Computer Engineering) McMaster University

Hamilton, Ontario, Canada

TITLE: A Multiple-FPGA Parallel Computing Architecture for

Real-time Simulation of Deformable Objects

AUTHOR: Seyed Behzad Mahdavikhah Mehrabad

B.Sc., (Electrical Engineering)

Sharif University of Technology, Tehran, Iran

SUPERVISOR: Dr. Shahin Sirouspour

NUMBER OF PAGES: xi, 125

# **Abstract**

In recent years there has been a growing interest in computer-based surgical planning, virtual-reality enabled training of medical procedures, and computer gaming all involving non-rigid deformable objects. High-fidelity simulations of haptic interaction with deformable objects is computationally demanding. The Finite Element Method (FEM) is known to produce relatively accurate solution for continuum mechanics-based models of soft-object deformation. Linear elastic FE models require solving a large sparse system of equations. The solution accuracy can be improved by increasing the resolution of the finite element mesh resulting in a larger number of equations and hence greater computational complexity. Depending on the mechanical characteristics of the soft-object, to maintain stability and high fidelity in haptic interaction, the update rate should be in the range of 100-1000Hz. This, for example, means that for a moderately-sized three-dimensional mesh of 6000 nodes, a set of 18000 linear equations must be solved within 1-10ms.

In this thesis, hardware-based parallel computing is proposed for finite-element (FE) analysis of soft-object deformation models. In particular, a distributed implementation of the (CG) algorithms on N Field Programmable Gate Array (FPGA) devices connected in a ring configuration is developed. This Parallel architecture can be utilized to solve the large system of equations arising from FE models at

high update rates required for stable haptic interaction. Massive parallelization of the computations is achieved by customizing the hardware architecture to the problem at hand and employing a large number of adaptive fixed-point computing units in parallel. The proposed hardware architecture satisfies three important criteria: (i) it meets the haptic rendering timing constraint by enabling an update rate of 400Hz; (ii) it attempts to simulate as many nodes as possible, given the available resources on the FPGA devices employed in this work and (iii) it is scalable both within an FPGA and also across multiple FPGA devices.

This research builds upon our group's earlier work in [1]. In that paper a novel highly parallelized single-FPGA architecture was proposed for solving system of equations arising from FEM using Conjugate gradient method. In this thesis, a multiple-FPGA architecture based on that design has been proposed. The contributions in the new multiple-FPGA design can be summarized as follows.

- proposing a novel method for expansion of conjugate gradient (CG) algorithm to multi processors.

- a new sparse matrix by vector multiplication unit, performing as the kernel of our hardware-based CG solver.

- proposing a novel storage format (SMVIS) for storing a vector, pre-multiplied by an sparse matrix which tremendously reduces the memory required vector storage.

- developing a new memory architecture for storing vectors in the CG algorithm, making the design capable of performing vector operations in the CG

algorithm regardless of their lengths.

• developing a novel communication scheme for Inter-FPGA communications in multiple-FPGA implementation of the CG algorithm.

An implementation of this scalable hardware accelerator on a quad-FPGA system has enabled real-time simulation of haptic interaction with a three-dimensional FE model of 6000 nodes at update rate of 400Hz. Both static and dynamic linear elastic models have been successfully simulated.

# **Contents**

| A۱ | Abstract |                                         |    |  |

|----|----------|-----------------------------------------|----|--|

| 1  | Intr     | roduction                               |    |  |

|    | 1.1      | Motivation                              | 1  |  |

|    | 1.2      | Problem Definition                      | 3  |  |

|    | 1.3      | Thesis Contributions                    | 6  |  |

|    | 1.4      | Thesis Outline                          | 8  |  |

|    | 1.5      | Related Publication                     | 8  |  |

| 2  | Lite     | rature Review                           | 10 |  |

|    | 2.1      | Deformable Object Modeling              | 10 |  |

|    |          | 2.1.1 Soft Object Modeling Methods      | 11 |  |

|    | 2.2      | Solvers for Linear Systems of Equations | 17 |  |

| 3  | Fini     | te Element Modeling                     | 22 |  |

|    | 3.1      | Basic Elasticity Concepts               | 24 |  |

|    | 3.2      | Principle of Minimum Potential Energy   | 28 |  |

|    | 3.3      | Applying Constraints                    | 36 |  |

|    | 3.4      | Dynamic FE Modeling                     | 37 |  |

| 4 | Con                      | jugate  | Gradient Algorithm                                    | 40 |

|---|--------------------------|---------|-------------------------------------------------------|----|

|   | 4.1                      | Algor   | ithms for Solving $\mathbf{K}\mathbf{x} = \mathbf{b}$ | 40 |

|   | 4.2                      | Fixed   | -Point Implementation of CG on Multiple FPGAs         | 42 |

| 5 | Mul                      | lti-FPG | A Design Scheme                                       | 51 |

|   | 5.1                      | An O    | verview of the Proposed Single-FPGA Design in [1]     | 52 |

|   | 5.2 Multiple FPGA Design |         | ple FPGA Design                                       | 55 |

|   |                          | 5.2.1   | Design I                                              | 59 |

|   |                          | 5.2.2   | Design II                                             | 60 |

|   |                          | 5.2.3   | Scaling up the Number of Nodes on Each FPGA           | 61 |

|   |                          | 5.2.4   | Scale the New Design to Multiple FPGAs                | 65 |

|   |                          | 5.2.5   | Design III                                            | 66 |

| 6 | Har                      | dware   | Architecture                                          | 72 |

|   | 6.1                      | Analy   | rsis of Hardware Limitations                          | 73 |

|   | 6.2                      | Data S  | Storage                                               | 75 |

|   |                          | 6.2.1   | Data Storage Formats                                  | 77 |

|   |                          | 6.2.2   | Memory Architecture                                   | 83 |

|   |                          | 6.2.3   | Memory Architecture for Storing Vectors               | 83 |

|   |                          | 6.2.4   | Storing K Matrix: Non-zero Values                     | 86 |

|   |                          | 6.2.5   | Storing K Matrix: Non-zero Indices                    | 89 |

|   | 6.3                      | Imple   | menting CG Algorithm On Multiple FPGAs                | 91 |

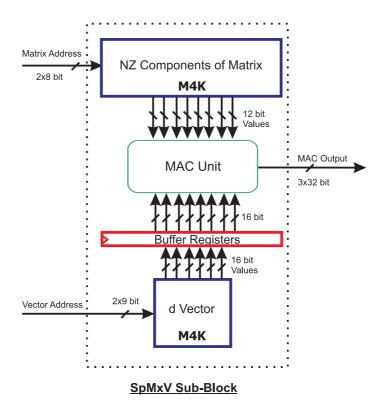

|   |                          | 6.3.1   | Sparse Matrix by Vector Multiplication                | 92 |

|   |                          | 6.3.2   | A Highly Parallelized Scheme for SpMxV                | 92 |

|   |                          | 6.3.3   | Vector by Vector Multiplication                       | 97 |

|                        |     | 6.3.4 Inter-FPGA Communication                  | 98  |  |

|------------------------|-----|-------------------------------------------------|-----|--|

|                        | 6.4 | Resource Usage                                  | 100 |  |

|                        | 6.5 | Timing Analysis                                 | 102 |  |

| 7 Experimental Results |     | erimental Results                               | 107 |  |

|                        | 7.1 | Performance Evaluation                          | 107 |  |

|                        | 7.2 | Hardware-in-the-Loop Haptic Simulation Platform | 111 |  |

| 8                      | Con | clusions and Future Work                        | 115 |  |

# **List of Figures**

| 1.1 | An example of employing haptic interfaces for modeling a soft-object.              |    |

|-----|------------------------------------------------------------------------------------|----|

|     | figure from [2]                                                                    | 2  |

| 2.1 | ChainMail model representation of 2D object before and after defor-                |    |

|     | mation (Figure from Sarah F.F. Gibson [3])                                         | 12 |

| 2.2 | Mass spring model of a 2D rectangular shape                                        | 13 |

| 3.1 | Strain-stress characteristics of a linear elastic material                         | 25 |

| 3.2 | Strain-stress characteristics of a non-linear elastic material                     | 26 |

| 3.3 | A 2D object with external possible forces applied to it. In this figure,           |    |

|     | s represents the surface traction b is the body force fp represents the            |    |

|     | point loads $\Gamma$ 1 and $\Gamma$ 2 refer to constraint and non-constraint nodes |    |

|     | of domain $\Omega$                                                                 | 27 |

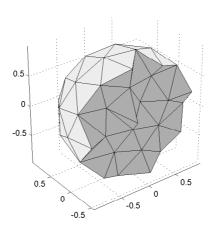

| 3.4 | Discretizing a sphere into tetrahedron elemental shapes                            | 31 |

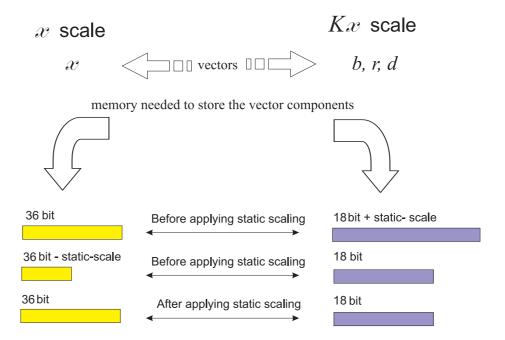

| 4.1 | Static Scaling. original figure with different bitwidths by Ramin Mafi             | 45 |

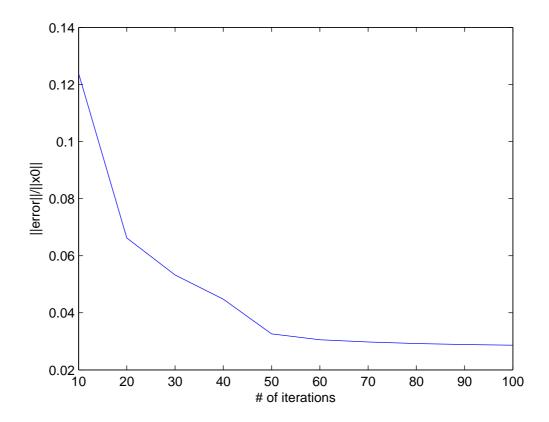

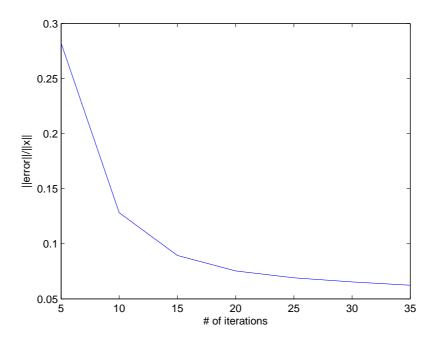

| 4.2 | Changes in the norm of error in fixed point implementation of the                  |    |

|     | CG as a function of the number of iterations                                       | 48 |

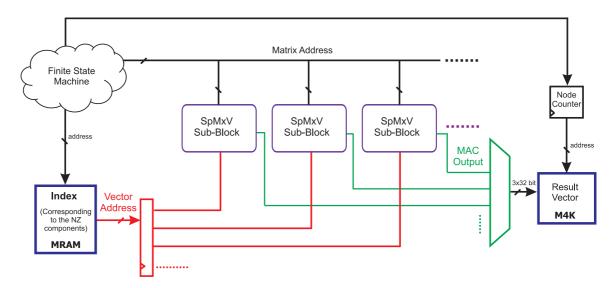

| 5.1 | The Connection Of MAC Units to Memory Blocks                                       | 54 |

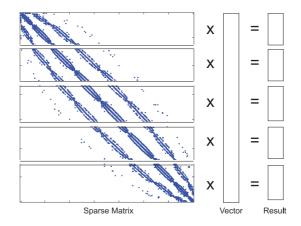

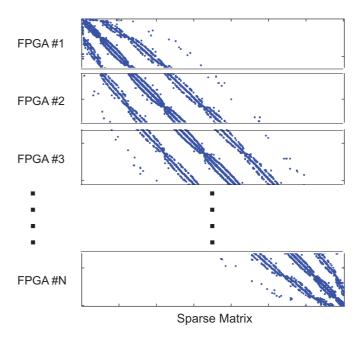

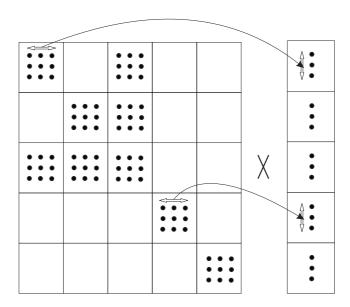

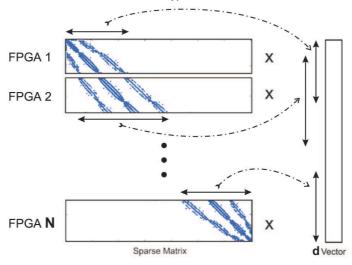

| 5.2 | Matrix Partitioning For Increased Parallelism                                      | 55 |

| 5.3 | Third Level of Parallelization                                                     | 56 |

| 5.4 | Portions of <b>K</b> matrix stored on each FPGA for performing first level |    |

|-----|----------------------------------------------------------------------------|----|

|     | of parallelization                                                         | 58 |

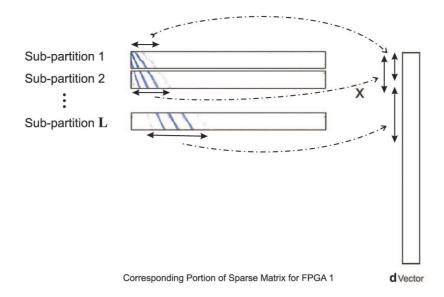

| 5.5 | Partial storage of the vector d for FPGA#1; Note that the correspond-      |    |

|     | ing elements of the vector for each sub-partition is marked by arrows.     | 59 |

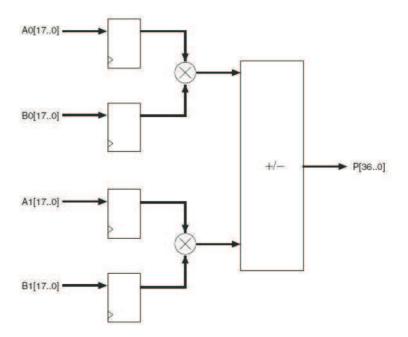

| 6.1 | Basic two-multiplier adder building block                                  | 74 |

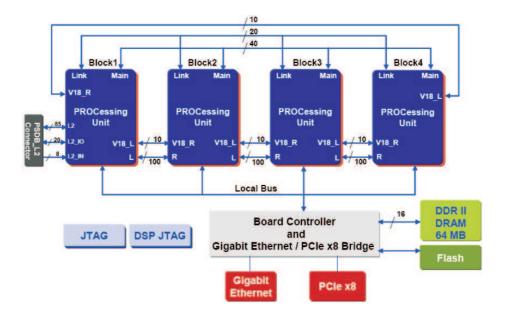

| 6.2 | ProcStar III system block diagram [4]                                      | 75 |

| 6.3 | A sample matrix used to demonstrate data storage formats                   | 78 |

| 6.4 | Performing sparse matrix by vector multiplication for rows 0 and           |    |

|     | 9 concurrently demands reading data from different locations of d          |    |

|     | vector                                                                     | 81 |

| 6.5 | The sample matrix and vector used to demonstrate SMVIS format              | 82 |

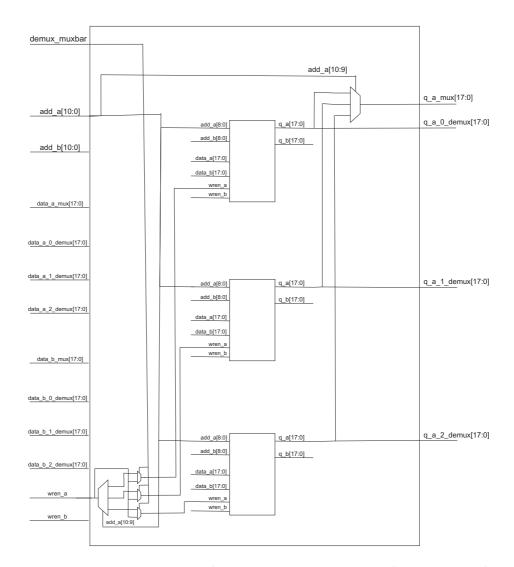

| 6.6 | Memory architecture for one dimension (out of x, y or z) of vectors,       |    |

|     | wiring for port a (inputs and outputs with "_a" term in their names)       |    |

|     | has been depicted in this figure and port b has similar wirings. Ports     |    |

|     | with names including "data_" are input ports and those with term           |    |

|     | $^{\prime\prime}q_{-}^{\prime\prime}$ are output ports                     | 84 |

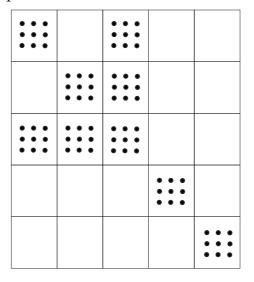

| 6.7 | 3*3 non-zero blocks for a matrix representing a mesh with $6$ nodes        | 87 |

| 6.8 | Memory architecture for storing NZ_values vectors of each subpar-          |    |

|     | tition                                                                     | 88 |

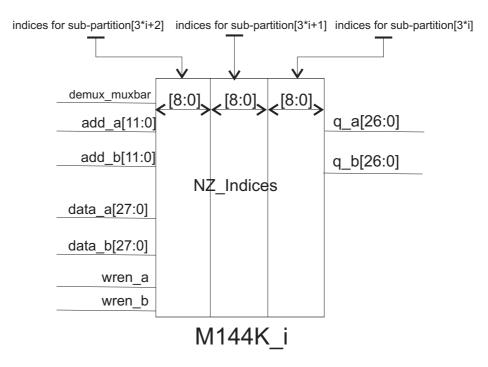

| 6.9 | Memory architecture for <i>nz_indices</i> storage in M144k rams. Ports     |    |

|     | including the term "data_" in their names are input ports and those        |    |

|     | with " $q_{\scriptscriptstyle\perp}$ " are output ports                    | 91 |

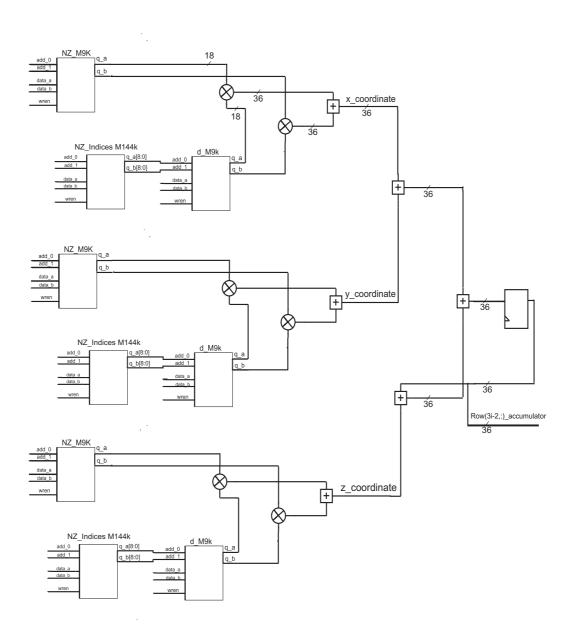

| 6.10 | Data path for K*d multiplication for row (3i-2,:), the same architec-              |

|------|------------------------------------------------------------------------------------|

|      | ture exists for rows (3i-1,:) and (3i,:) for each sub-partition. In this           |

|      | figure, d_M9k refers to M9ks storing <b>d</b> vector values for sub-partitions. 94 |

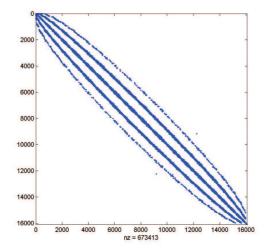

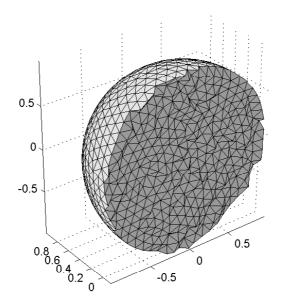

| 6.11 | The K matrix arising from performing FE analysis on an sphere in                   |

|      | our tests                                                                          |

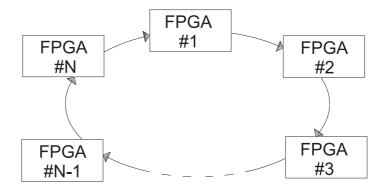

| 6.12 | The communication scheme in multi-FPGA architecture. Arrows                        |

|      | show the direction of the data flow                                                |

| 6.13 | Portions of d vector needed for each FPGA for performing Kxd mul-                  |

|      | tiplication d vector                                                               |

| 6.14 | Compilation report for an FPGA in our current design                               |

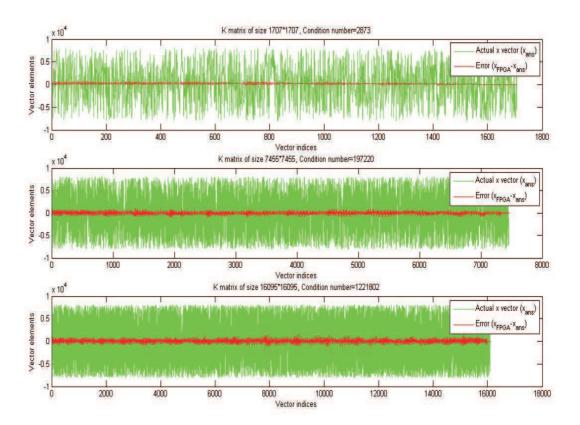

| 7.1  | Changes in the norm of error in FPGA result as function of number                  |

|      | of iterations                                                                      |

| 7.2  | A transverse section of the spherical mesh associated with the largest             |

|      | matrix with 5365 nodes in our tests                                                |

| 7.3  | Error in FPGA solution compared to the real $x$ vector for three dif-              |

|      | ferent matrix sizes                                                                |

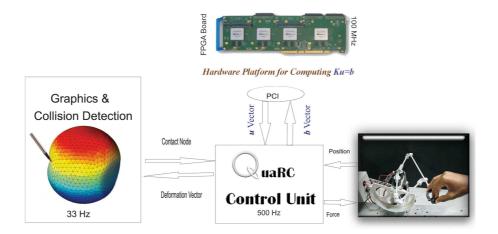

| 7.4  | The block diagram of haptic-enabled simulator with hardware-based                  |

|      | accelerator                                                                        |

# Chapter 1

# Introduction

# 1.1 Motivation

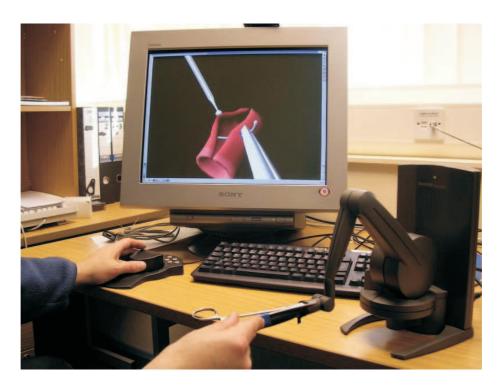

In the early 20th century, psychophysicists introduced the word haptics from the Greek *haptesthai* meaning to touch in order to label the subfield of their studies that addressed human touch-based perception and manipulation [5]. In the early 1990s a new usage of the word haptics began to emerge. "The confluence of several emerging technologies made virtualized haptics, or computer haptics, possible" [6], [5]. Computer haptics allows a user to interact with the virtual objects, receiving kinesthetic, force and tactile feedback. This interaction between user and the virtual environments is fulfilled using bidirectional human-machine interfaces called *haptic devices* which allow users to receive force-feedback based on an interaction model. Fig. 1.1 illustrates an example for such haptic interaction with a virtual soft-object utilizing a haptic device.

Modern computers have the capability for visual and auditory interactions with their users. The next generation of computer interfaces will add the haptic feel

Figure 1.1: An example of employing haptic interfaces for modeling a soft-object. figure from [2]

to the computers, allowing their users to feel and touch the virtual objects. Such computer interactions have been already developed in simple forms such as vibrations and force feedback in computer games using rudimentary joysticks or racing wheels. The current force feedback in these applications is predominantly from interaction with rigid objects. Modeling of such interactions is relatively straightforward and has been extensively studied in the literature [7]. The ultimate form of computer haptics would involve simulating interactions with both deformable and rigid objects.

Real-time haptic rendering of deformable objects can be helpful in applications involving interaction with a non-rigid soft object. It is especially of a great interest in gaming, surgical training and surgery planning.

In surgical training, having a realistic simulation of biological soft-tissue allows

surgeon to rehearse operation without exposing the patient to undue risk. This application of soft-tissue modeling has become more relevant since the emergence of robotics-assisted in minimally invasive surgery. The novelty of such systems for most surgeons demands extend training to acquire the required skills. Such training can be enabled by virtual-reality based systems involving haptics and visual feedback. Moreover in surgical planning for procedures such as needle insertion, pre-operative plans usually need to be updated in real time due to soft-tissue deformations or organ movements during the operation. In such cases, a simulator can allow the surgeon to examine different task scenarios using the latest information available and choose the best course of action.

### 1.2 Problem Definition

Real-time haptic and deformation rendering of soft objects can be challenging due to massive computations that most be performed within a very short time to achieve the required high simulation update rate. Violating a minimum update rate can degrade the quality and accuracy of the simulation and even lead to interaction instability when haptic feedback is involved. This accentuates the need for powerful computational engine capable of performing these necessary computations within the permissible time.

Continuum mechanics based models can be utilized to accurately model softobject deformation. Such a modeling approach will produce boundary condition Partial Differential Equations (PDEs) which generally do not have a closed-form solution except in special cases [8]. A numerical method such as the FEM can be employed to find an approximate solutions for these PDEs. The application of the FEM to linear elastic deformation models will result in a large sparse set of equations in the form of  $\mathbf{K}\mathbf{x} = \mathbf{b}$ , where  $\mathbf{K}$  is the stiffness matrix,  $\mathbf{b}$  is the load vector and  $\mathbf{x}$  is the vector of unknown deformations. In the FEM, the object is represented with a mesh of nodes forming 2D (e.g. triangular) or 3D (e.g. tetrahedral) elements. The total number of nodes determines the size of K matrix which would be 3n\*3n for a 3D model, where n is the total number of nodes in the mesh. As can be presumed intuitively, increasing the number of nodes in the mesh would improve the accuracy of the approximate solution obtained with the FE method.

While an update rate as low as 15-30Hz would be acceptable for graphics rendering, stable haptics interaction with virtual objects would require update rates in the range of 100-1000Hz. This higher update rate needed for haptics rendering imposes a stringent timing constraint on the simulation. The main computational problem in simulating FE-based deformation models is in solving the set of linear equations  $\mathbf{K}\mathbf{x} = \mathbf{b}$  in real time. To obtain an accurate solution to the deformation problem using the FEM, a high-resolution mesh must be used in the simulation, usually involving several thousands nodes. For example in this thesis a FE mesh of 6000 nodes is used to represent the object resulting in a K matrix of size 18000\*18000. Solving such system of equations in real time (1-10miliseconds) using state-of-the-art conventional CPUs is impractical. For this purpose, we propose a hardware-based highly parallelized solver for the FE-based equations. This solver, find the solution to the sparse system of Kx = b employs the CG method.

A critical decision in hardware implementation of the CG algorithm is the choice

between fixed-point and floating point computing. Using floating point representation of numbers will in a high hardware cost, limiting the achievable parallelism. On the other hand fixed-point implementation will reduce the dynamic range of values' representation which can be problematic specially for iterative methods by increasing relative error. This can result in numerical instability. We utilize a custom fixed-point implementation of the CG algorithm proposed by mafi et.al in [1]. More details about our fixed-point implementation and it's numerical stability analysis is given in Chapter 4. In this approach customized fixed-point computing can greatly increase the parallelism without noticeable decrease in accuracy.

Another problem concerns the scalability of the utilized solver for the system of equations Kx = b. Accuracy of the FEM, to a large extend, depends on the number of nodes in FE mesh. For example, typical meshes for biological soft-tissue may involve several thousand nodes. On the other hand, due to insufficient resources available on any processor, non of the current available processors (CPUs, GPUs, FPGAs, etc.) are powerful enough to solve such big set of equations in expected time frame.

Taking these into account, utilization of multiple-processors for solving such system of equations is inevitable. The scalability of the hardware architecture for the solver is important in two senses:

1. The hardware design utilized for doing the computations should be scalable on multiprocessors.

Thus breaking down the computations involved such that it creates the minimum overlap among the processors both in data and timing sense is necessary. This means that there should be a minimum amount of data needed to

be shared between the processors for less memory usage on each processor and moreover to reduce the communication required among them. In addition minimizing the timing overhead requires that the processors should work such that none of them be idle at any time waiting for results from other processors.

The proposed architecture design should be scalable in a way that it can take advantage of newer FPGA devices that will have greater amount of on-chip memory and DSP resources

### 1.3 Thesis Contributions

The main premise of this work is that the steps involved in the FE simulation of object deformation can be classified as: (i) performing algorithmically complex but computationally inexpensive routines; (ii) solving a large linear system of equations. The latter can be delegated to a customized parallel-computing platform whereas the former can be simply executed on a conventional computer.

In [1], we developed an FPGA-based accelerator for solving a sparse system of equations using the iterative method of Conjugate Gradient [9]. In this thesis, the hardware solution will be generalized to a multiple-FPGA configuration with increased parallelism in order to solve larger FE problems using the Conjugate Gradient (CG) method.

It is worth mentioning that although this architecture has been developed mainly for modeling soft-tissues using linear models which result in equations in the form Kx = b, it can be also utilized for some non-linear deformation models by solving

an incremental form of such equations. This incremental form of these equations can be derived as described in [10].

The main contributions of this thesis are in:

proposing a novel highly parallelized, scheme for fixed point CG implementation on an FPGA with a new sparse matrix by vector multiplication unit, vector by vector operation unit and a new memory architecture comparing to [1].

this design is scalable to multi processors with linear increase in resource usage by increase in number of FPGAs.

- Proposing a new storage method for storing a dense vector, pre-multiplied by a sparse matrix (Sparse matrix vector Indexing Scheme(SMVIS)) which dramatically decreases the memory usage while parallelizing the matrix by vector multiplication by performing multiplication for some rows at the same time.

- proposing a novel method for performing the CG method on multiple processors.

- proposing a novel architecture for implementing multi-processor CG method on multiple FPGAs. The implementation on 4 Stratix III Altera devices yields 302 Giga Operations per Second and a memory bandwidth of 7.257 TB/s while doing the matrix by vector multiplication.

Designing a novel communication scheme for required inter-FPGA data exchanges.

## 1.4 Thesis Outline

The rest of this thesis is organized as follows:

In the Chapter 2 a brief review of the prior work is presented, Chapter 3 introduces the finite element method and formulations, Chapter 4 briefly discusses the fixed-point implementation of the Conjugate Gradient method. In Chapter 5 the algorithm for the expansion of the design on multiple FPGAs is described. Chapter 6 presents the proposed hardware architecture employed for carrying CG on multiple FPGAs. Chapter 7 covers the system performance and experimental results and Finally, the thesis is concluded in Chapter 8 where some possible directions for future research are also discussed.

# 1.5 Related Publication

- R. Mafi, S. Sirouspour, B. Moody, B. Mahdavikhah, K. Elizeh, A. Kinsman,

N. Nicolici, M. Fotoohi and D. Madill, "Hardware-based Parallel Computing for Real-time Haptic Rendering of Deformable Objects" IROS 2008. IEEE/RSJ International Conference on Intelligent Robots and Systems Volume, Issue, 22-26

Sept. 2008 Page(s):4187 4187, Digital Object Identifier 10.1109/IROS.2008.4651242.

- Ramin Mafi, Shahin Sirouspour, Behzad Mahdavikhah, Brian Moody, Kaveh

Elizeh, Adam Kinsman and Nicola Nicolici, "A Parallel Computing Platform

for Real-time Haptic Interaction with Deformable Bodies" submitted to the *IEEE Transactions on Haptics*(revised).

# Chapter 2

# Literature Review

This chapter presents an overview of related works on real-time modeling of soft tissue deformation. At first we will have a survey on different deformable body models described in the literature and as will be explained in we have chosen FEM based continuum mechanics modeling in our application. This would be followed by an introduction to different mathematical methods and computational platforms for real-time FEM based modeling of soft tissue deformation. The last section will review the efforts done for FEM based modeling of soft tissue by employing multi processors.

# 2.1 Deformable Object Modeling

In this section some of the most common methods used for deformable body modeling are briefly introduced and then we will focus on finite element based continuum mechanics based model, which is the core model used for our simulation.

# 2.1.1 Soft Object Modeling Methods

Deformable object models are used to find the new formation of a deformable body after applying external or internal forces on it. There has been a considerable research in modeling of real-time interaction with non-rigid deformable objects, e.g. see [11,12]. Generally soft object modeling methods are divided into two groups, physical based models and non-physical models. Non-physical models are based on heuristic geometric techniques or use simplified physical principals to obtain an acceptable model of the tissue. [13,14]. For more details the reader is referred to [15].

Two popular non-physics based models are:

- Spline modeling: In this approach, both planar and 3D curves and surfaces are represented by a set of control points. The deformation of the object is then defines as a function of these control points. By varying the positions of these points or adding or removing or changing the weight of some of these points the new formation of the complex objects would be determined [15,16]. As a result of inaccuracy of this model model due to it's non-physics base modeling, this model is no longer used [15].

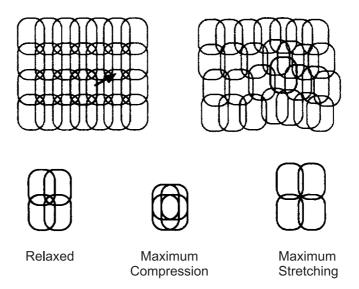

- ChainMail modeling: In this approach, the soft tissue is represented with cubic lattices, where each of the cubs an move slightly with respect to its neighbors and the position of cubes are finally adjusted by minimizing the total potential energy. ChainMail has very low computational cost but it is not realistic and imposes severe constraints on what mesh topology may be used [17]. Moreover, simultaneous multiple contact points in this model

result in an extensive computational cost for determining the propagation of the imposed displacements on the elements [11]. Fig. 2.1.1 depicts the ChainMail model representation of a 2D object.

Figure 2.1: ChainMail model representation of 2D object before and after deformation (Figure from Sarah F.F. Gibson [3]).

The physical methods are based on solving the equations from physics principles or more specifically the theory of elasticity considering material properties. These models are computationally demanding because they require solving partial differential equations. Physically based models result in more accurate and realistic results. Terzopoulos [18], Waters [19] and Platt [20] showed the advantages of the physically-based models on previous computer animation techniques [21]. Physical based models can be divided into following categories:

- Mass Spring models

- Linear Green Function (GF) models

- Continuum mechanics-based models

### **Mass Spring Models**

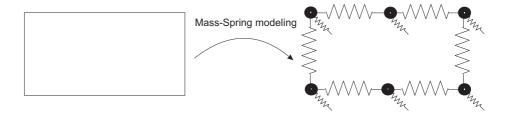

Mass Spring models represent the object with a mesh of nodal concentrated masses with a network of massless springs connecting the nodes together. Also each nodal mass is connected to its initial position with a damper element. Fig. 2.2 illustrates the mass-spring representation of a 2D rectangle. The elastic behavior of the springs can be changed to match physical properties of the material. The springs can have linear behavior, but non-linear or volumetric material properties may also be used [22, 23].

Figure 2.2: Mass spring model of a 2D rectangular shape

Therefore for node N of the mesh we can write the equation of motion:

$$\mathbf{M}\ddot{\mathbf{x}} + \mathbf{b}\dot{\mathbf{x}} + \sum_{i} \mathbf{F_{i}} = \mathbf{F_{ext}}$$

(2.1)

where x,  $\ddot{x}$  and  $\dot{x}$  are position, velocity and acceleration of the node respectively, M denotes the mass connected to node N,  $F_i$  represents the internal force exerted to node N from node i which is connected to node N through a spring connector. Also,  $F_{\rm ext}$  is the total external force applied to node N. After assemblage and writing the equations for all of the nodes in a matrix format we will come up with Eq. 2.2 for the dynamic case which will reduce to Eq. 2.3 for a static case.

$$\mathbf{M}\ddot{\mathbf{x}} + \mathbf{C}\dot{\mathbf{x}} + \mathbf{K}\mathbf{x} = \mathbf{f} \tag{2.2}$$

$$\mathbf{K}\mathbf{x} = \mathbf{f} \tag{2.3}$$

Here **M** and  $\mathbf{C} \in \mathbb{R}^{3n}$  are diagonal matrices for mass and damping and  $\mathbf{K} \in \mathbb{R}^{3n}$  is a sparse stiffness matrix.

Mass-spring model is the simplest and the least computationally intensive physical based method but it not necessarily accurate. Moreover, most of systems based on mass-spring models are not convergent [12].

That is, as the mesh is refined, the simulation does not converge on the true solution. Instead, the behavior of the model is dependent on the mesh resolution and topology. In practice, spring constants are often chosen arbitrarily, and one can say little quantitatively about the material being modeled. Utilizing learning algorithms to find model parameters is an interesting approach in mass-spring models. e.g. [24, 25] and references therein. Despite all efforts, the integration of realistic tissue properties into parameters of mass-spring model is not a trivial task. The construction of an optimal network of springs in 3D is a complicated process and particle systems can become oscillatory or even unstable under certain conditions [26].

Another deficiency of Mass-spring modeling is that large mass-spring-damper meshes can impede rapid global propagation of deformations resulting in a localized deformation [11].

### Linear Green Function (GF) Models

One of the earliest approaches introduced in [27] uses Greens functions (GFs) and fast low-rank updates based on Capacitance Matrix Algorithms. GFs form a basis for describing all possible deformations of a linear elastic model. This method works based on a huge amount of pre-computations assuming a linear deformation model. It uses a look-up table for different deformations and applies superposition principle. This approach is not suitable for objects with nonlinear elastic models and for large number of nodes and contact nodes. [27].

### **Continuum Mechanics Based Models**

Constitutive models based on continuum mechanics have been proposed to accurately model soft-object deformation [28]. Continuum mechanics provides a physics based-model for modeling soft object deformation. In continuum mechanics a material is known to have definite densities of mass, momentum, and energy in the mathematical sense. The mechanics of such a material continuum is continuum mechanics [29]. Therefore, for such an object the continuum model establishes a set of relationships between the shape of the body, constraints and internal deformations within this solid and the external forces applied to it. The behavior of the tissue would be governed by equations arising from continuum mechanics. Such modeling approach yields partial differential equations involving the deformation filed, applied forces to the object, and a set of boundary conditions. These equations are defined by physical principals such as the laws of conservation of mass, the balance of momenta and the balance of energy, as well as the constitutive equation that mathematically expresses the mechanical property of the body

material [30]. The continuum equations are obtained by computational methods for solving the continuum mechanics based equations of the body.

Some of the most common computational methods for finding solution to continuum based models are:

- Finite Difference Method: In this method continuous derivatives in PDEs are substituted by finite difference equations in related domain. As a result of this process, the PDEs will reduce to a set of algebraic equations [31]. The applications of this method are limited because the discretization of objects with irregular geometry becomes extremely dense. [14]

- Boundry Element Method(BEM): This approach transforms the integral of the motion equations for a volume in surface integrals using Green-Gauss theorem. Thus this method is considerably faster than other modeling methods since it will only deal with 2D equations. One drawback of this method is that it requires homogeneity of the object [12] which is not always the case in biological tissue material. Furthermore, it does not allow volumetric changes to the object which means it can not compute the displacement of any interior point. So it will be incapable of simulating medical operations such as cutting or suturing.

- Finite Element Method(FEM): This method can be used to discretize the model in the spatial domain in the absence of an analytical solution to such problems in most cases. This is achieved by partitioning the object into small elementary shapes and then derive the equations of motion for each element as a function of the mesh node displacements [32].

FEM is applicable to solve PDEs in irregular grids. In this method the object

is divided into some elemental shapes e.g. triangles in 2D space or tetrahedrons in a 3D space, then the formulation for each element is done based upon the Principle of Minimum Potential Energy. After this step for each element the relation between stress, strain and nodal displacements has been determined. The next step in FEM is assemblage, in which the equations relating the external and internal forces and nodal displacements are derived for the whole object. Thus the continues problem in 3D spatial domain converts to a set of discrete set of unknown position equations [12], which can be solved more easily by numerical methods. However, the need to manipulate large matrices and solve large numbers of differential equations imposes performance difficulties to apply FEM to real time interactive haptic feedback applications. [33]. In [34] and [35] interpolation of forces is proposed for calculation of high rate haptic fedback from a low rate model. The other approach to speed up run-time simulation is to isolate some procedures of the real-time computation, precompute them and later combine precomputed results with states of a simplified run-time model [33].

# 2.2 Solvers for Linear Systems of Equations

For performing the matrix by vector operation on a CPU, the memory bandwidth limit would be the bottleneck, which lowers the performance of CPU down to 10-33% of their peak performance while doing matrix by vector operation [36]. The situation is even worse when the matrix is sparse [36].

In general, there has been a prevailing tendency in the research community towards using algorithmic software-based solutions for addressing the problem of real-time object deformation simulation. Notable exceptions to this trend are a number of papers proposing parallel computing using multiple-CPU computer clusters [37] or Graphics Processing Units (GPU) [38].

CPU and GPU architectures are bounded by their maximum computational and memory bandwidth. Their efficiency mainly depends on the implemented operations. In the case of sparse matrix by vector operations, both computational and memory bandwidth efficiency are low in GPUs and CPUs [39].(computational band width refers to the measure of amount of operations a processor can do in the unit of time).

In the last few years, FPGAs have significantly advanced both in terms of speed and resources, i.e. the number of arithmetic units, programmable logic cells and embedded memories. Such solution offers a real advantage over networked parallel computers by providing enormous computation power in a compact and relatively inexpensive package. Compared with general-purpose GPUs, FPGA-based custom computing architectures can provide greater parallelism by tailoring the hardware computing unit to the problem at hand.

In [40], the authors have presented fast algorithms for the solution of large linear equation systems as they typically arise in finite element discretisations. They used both GPU and FPGA devices for implementing solvers for these systems, using Emulated and mixed precision solvers. The emulation utilizes two single float numbers to achieve higher precision by using lower precision processing elements, while the mixed precision iterative refinement computes residuals and updates the solution vector in double precision but solves the residual systems in single precision using CG or multigrid solver.

They show that implementation of the emulation technique on GPU is significantly slower for the PDE problem than the mixed precision iterative refinement on FPGA.

Elkurdi et al. [41] presented an architecture and implementation of an FPGA-based sparse matrix by vector multiplier (SMVM) for use in the iterative solution of large, sparse systems of equations arising from FEM applications, their architecture benefits from a hardware-oriented matrix striping algorithm utilizing the matrix structure. The implemented SMVM-pipeline prototype contains 8 Processing elements(PEs) and is clocked at 110 MHz obtaining a peak performance of 1.76 GFLOPS. For 8 GB/s of memory bandwidth typical of recent FPGA systems, this architecture can achieve 1.5 GFLOPS sustained performance. Mafi [42] proposed a highly parallelized hardware implementation of CG algorithm. In that design they utilized a novel fixed point method for representation of floating point numbers with static and dynamic scaling to mitigate quantization errors. This design works on a single FPGA and achieves 18 GOPs for implementation on a Stratix II EP2S60.

It is worth mentioning that hardware-based solutions for sparse matrix by vector multiplication and for solving linear systems of equations have been discussed in a few previous papers, e.g. see [43,44]. These approaches, which use floating point operations, are rather abstract and cannot be scaled to solve practical problems using existing FPGA devices. Floating-point implementations have a high hardware cost, severely limiting the parallelism and thus the performance of the hardware accelerator. In contrast, the proposed hardware architecture reaches a

good tradeoff among error, calculation time and hardware cost by using a novel, modified type of fixed point operations and utilizing fixed-point computing units. A key novelty of the proposed solution is in its ability to continuously supply data operands to a large number of computing units within a scalable architecture. The hardware solver is largely independent of the FE mesh configuration and can be scaled up based on available FPGA resources to solve problems of larger size.

Due to the properties of computation intensiveness and computation locality, it is very attractive to implement FEM on multi processors. For this objective two general approaches can be considered. One is exploiting domain decomposition methods to subdivide the physical domain into smaller regions or subdividing the large linear systems into smaller subsystems whose solution can be used to produce a pre-conditioner for the system of equations that results from discretizing the PDE on the entire domain. [45]. The second is to apply multi processing methods for solving equations from the single level equations, that is performing the computations involved in single level equations on multiple processors.

Generally all domain decomposition methods, require iteration on solution to system of linear equations on each sub-domain in order to find the result for interface nodes, located between two sub-partitions. Aside from convergence issues, this makes them slower comparing to the second method which only requires one time of solving a set of linear equations.

Another significant disadvantage of the domain decomposition methods is that the mesh levels must be generated offline. This prohibits, for example, local mesh refinement when tissue is cut. [46]

Ulrike et al. [47] performed the parallel implementation of CG algorithm on Cedar(4 multiple processor clusters which are connected through an inter connection network). They achieved a speed of 38 milliseconds for 1 CG iteration for n=255, where n is the dimension of matrix. The performance is worse for a multi processor architecture with 16 processors working in parallel which diminishing to 5% of the peak performance of whole system. [36]

A floating point implementation of sparse matrix by vector multiplication on multi FPGAs has also been proposed by delorimier et al. [36], in this design they project 1.5 double precision Gflops/FPGA for a single VirtexII-6000-4 and 12 double precision Gflops for 16 Virtex IIs (750Mflops/FPGA).

In this thesis, a parallel computing platform is proposed that employs multiple Field Programable Gate Array (FPGA) devices to greatly speed up the calculations in the FE-based deformation analysis. In the proposed method a customized fixed-point operation proposed by Mafi et al. in [48].

The implementation on 4 Stratix III Altera devices achieves a peak performance of 302 GOPs(giga operations per second) and a memory bandwidth of 7.257 TB/s while doing the matrix by vector multiplication.

# Chapter 3

# **Finite Element Modeling**

As discussed in Chapter 2, for modeling the soft-object deformations, we use Finite Element Method to obtain physical modeling of the object based on continuum mechanics differential equations. In this chapter the formulation of the Finite Element Method will be presented for both static and dynamic simulations. In our haptic simulator, the user interacts with a virtual object using a force feed-back haptic interface. The simulation uses a model of interaction to calculate the object motion/deformation as well as the interaction force. In an impedance-type simulation, the haptic device imposes its displacement on the virtual object at the contact point and in response the deformation of the entire body and interaction force are computed by the model.

In finite element method we need to take some steps for discretizing the PDEs governing the object behavior to some linear equations coming from assemblage of the equations for elemental shapes constituting the object. The steps (quoted from [49]) are as follows:

- 1. "The continuum is separated by imaginary lines or surfaces into a number of 'finite elements'.

- The elements are assumed to be interconnected at a discrete number of nodal points situated on their boundaries. The displacements of these nodal points will be the basic unknown parameters of the problem.

- 3. A set of functions is chosen to uniquely define the state of displacement within each 'finite element' in terms of its nodal displacements.

- 4. The displacement functions now uniquely define the state of strain within an element in terms of the nodal displacements. These strains together with nodal initial strains and the constitutive properties of the material, will define the state of stress throughout the element and on the boundaries.

- 5. A system of forces concentrated at the nodes and equilibrating the boundary stresses and any distributed loads is determined, resulting in a stiffness relationship of the form of equation 3.1.

$$\mathbf{K}\mathbf{x} = \mathbf{f} \tag{3.1}$$

This approach is also known as Displacement formulation [50,51].

One of the most important and challenging steps in finite element analysis is the derivation of the finite element characteristics [52]. In stress and structural analysis, the finite element characteristics can be derived by applying the principle of minimum potential energy.

This approach will result in the stiffness (or displacement) method, wherein the

primary unknowns are the nodal displacements.

The material used in this section are mostly borrowed from [28, 32, 52] and the reader is referred to them for more details.

# 3.1 Basic Elasticity Concepts

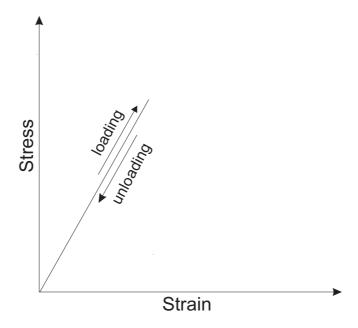

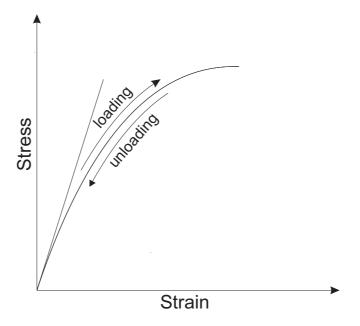

Generally the term **stress** in elasticity theory refers to the force per unit area. The term **strain** refers to elongation per unit length [52]. An elastic object will return to its natural shape (the formation it had before applying the force on it) after releasing the force being exerted on it, if the applied stress would have been less than its elastic limit. The elastic objects are divided into two types, linear elastic and nonlinear elastic materials. Linear elastic materials have a stress-strain characteristic as shown in Fig. 3.1 and some non-linear objects have a stress-strain characteristic as shown in Fig. 3.2. In the following sections first modeling for static linear elastic models would be presented and then it will be expanded to dynamic modeling of linear objects.

### **Kinematic Relations**

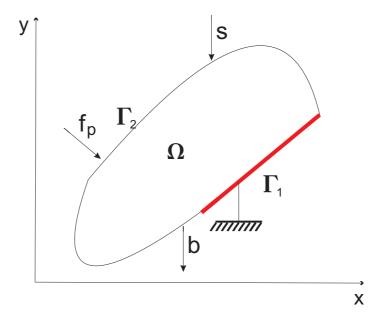

The modeled tissue will be defined in 3D spatial domain as  $\Omega$ .  $\Omega$  consists of the particles with positions  $\mathbf{x} = [\mathbf{x}\mathbf{y}\mathbf{z}]$  while the tissue is not deformed.  $\Omega$  is made by two partitions,  $\Gamma_1$  and  $\Gamma_2$ , where the nodes which are in  $\Gamma_1$  are constraint nodes, that is before and after deformation their location does not change but nodes in  $\Gamma_2$  will be displaced when the object is under stress. These displacements are referred as  $\mathbf{u} = [\mathbf{u}\mathbf{v}\mathbf{w}]$ . Therefore, the new position of the particle  $\mathbf{x}$  after deformation would

Figure 3.1: Strain-stress characteristics of a linear elastic material

be  $\mathbf{x} + \mathbf{u}$ .

Fig. 3.3 illustrates a 2D object and its partitions in xy plane. In this figure s corresponds to surface traction forces, b represents body force and  $f_p$  shows the external forces applied to the object. For small deformations stress and strain are related to each other as:

$$\epsilon_{xx} = \frac{\partial u}{\partial x} \ \epsilon_{yy} = \frac{\partial v}{\partial y} \ \epsilon_{zz} = \frac{\partial w}{\partial z}$$

$$\epsilon_{xy} = \frac{\partial u}{\partial y} + \frac{\partial v}{\partial x}$$

$$\epsilon_{yz} = \frac{\partial w}{\partial y} + \frac{\partial v}{\partial z}$$

$$\epsilon_{zx} = \frac{\partial u}{\partial z} + \frac{\partial w}{\partial x}$$

(3.2)

Therefore, the relationship between the strain vector  $\epsilon = [\epsilon_{xx} \; \epsilon_{yy} \; \epsilon_{zz} \; \epsilon_{xy} \; \epsilon_{yz} \; \epsilon_{zx}]^T$

Figure 3.2: Strain-stress characteristics of a non-linear elastic material

and the displacement vector  $\mathbf{u}^T = [u\ v\ w]$  can be expressed as in Equation 3.3, where the  $\mathbf{L}$  is known as the strain-displacement matrix.

L matrix is a linear operator and is derived as in Equation 3.4.

$$\epsilon = \mathbf{L}\mathbf{u} \tag{3.3}$$

$$\mathbf{L} = \begin{bmatrix} \frac{\partial}{\partial x} & 0 & 0\\ 0 & \frac{\partial}{\partial y} & 0\\ 0 & 0 & \frac{\partial}{\partial z}\\ \frac{\partial}{\partial y} & \frac{\partial}{\partial x} & 0\\ 0 & \frac{\partial}{\partial z} & \frac{\partial}{\partial y}\\ \frac{\partial}{\partial z} & 0 & \frac{\partial}{\partial x} \end{bmatrix}$$

(3.4)

Hook's law states that the normal stress  $\sigma$  is proportional to normal strain  $\epsilon$  in a

Figure 3.3: A 2D object with external possible forces applied to it. In this figure, s represents the surface traction b is the body force fp represents the point loads  $\Gamma$ 1 and  $\Gamma$ 2 refer to constraint and non-constraint nodes of domain $\Omega$ .

uniaxial state of stress, or:

$$\sigma = E\epsilon \tag{3.5}$$

where E is known as Young's modulus, the elastic modulus or the modulus of elasticity. Hook's law in this form is of rather limited use. A much more general version of hook's law is given by Equation 3.6 [49,52].

$$\sigma = D(\epsilon - \epsilon_0) + \sigma_0 \tag{3.6}$$

where **D** is referred to as the material property matrix,  $\sigma$  the stress vector,  $\epsilon$  the strain vector,  $\epsilon_0$  the self-strain vector, and  $\sigma_0$  the initial or residual stress vector. In 3D the  $\epsilon$  is defined as before and  $\epsilon_0$ ,  $\sigma$ ,  $\sigma_0$  are defined as in Equation 3.7 and the **D** for a linear elastic isotropic material is given by [49] as in Equation 3.8. In this

equation the  $\mu$  represents poisson's ratio. In addition the material property matrix D is symmetric [52].

$$\epsilon_{0} = \left[\epsilon_{xx0} \ \epsilon_{yy0} \ \epsilon_{zz0} \ \epsilon_{xy0} \ \epsilon_{yz0} \ \epsilon_{zx0}\right]^{T}$$

$$\sigma = \left[\sigma_{xx} \ \sigma_{yy} \ \sigma_{zz} \ \sigma_{xy} \ \sigma_{yz} \ \sigma_{zx}\right]^{T}$$

$$\sigma_{0} = \left[\sigma_{xx0} \ \sigma_{yy0} \ \sigma_{zz0} \ \sigma_{xy0} \ \sigma_{yz0} \ \sigma_{zx0}\right]^{T}$$

$$(3.7)$$

$$D = \frac{E}{(1+\mu)(1-2\mu)} \begin{pmatrix} 1-\mu & \mu & \mu & 0 & 0 & 0\\ \mu & 1-\mu & \mu & 0 & 0 & 0\\ \mu & \mu & 1-\mu & 0 & 0 & 0\\ 0 & 0 & 0 & \frac{1-2\mu}{2} & 0 & 0\\ 0 & 0 & 0 & 0 & \frac{1-2\mu}{2} & 0\\ 0 & 0 & 0 & 0 & 0 & \frac{1-2\mu}{2} \end{pmatrix}$$

(3.8)

The initial vector  $\sigma_0$  represents pre-stresses that are known to exist in a material before it is loaded. The FEM or any other method can not predict these parameters and they must be determined by analyst. The self-strain vector  $\epsilon_0$  may be a result of crystal growth, shrinkage or most common temperature changes.

### 3.2 Principle of Minimum Potential Energy

The total potential energy ( $\Pi$ ) is defined to be the sum of internal potential energy, the strain energy ( $U_i$ ), and the external potential energy from external forces ( $U_e$ ) [52], or:

$$\Pi = U_i + U_e \tag{3.9}$$

For conservative systems the loss in the external potential energy is equal with the work done by external forces.

$$U_e = -W_e \quad \Rightarrow \quad \Pi = U_i - W_e \tag{3.10}$$

The principle of minimum total potential energy states that  $\Pi$  must be minimum for stable equilibrium, therefore the first variation of the total potential energy (as a result of variation in displacement) should be zero. That is,

$$\delta\Pi = \delta U_i - \delta W_e = 0 \quad \Rightarrow \quad \delta U_i = \delta W_e \tag{3.11}$$

Moreover, using the matrix notation form for strain and stress vector for the strain energy we will have:

$$\delta U_i = \int_V (\delta \epsilon)^T \sigma dV \tag{3.12}$$

As shown in Fig.3.3, generally three types of external forces are applied to the body, s which represents the surface traction e.g. the hydrostatic pressure (force per unit area) on the water filled side of a dam, the body force b (per unit volume) and up to N point loads  $f_p$ . The first variation of the work done by these three external forces is

$$\delta W_e = \int_V (\delta \mathbf{u})^T b dV + \int_S (\delta \mathbf{u})^T \mathbf{s} dS + \sum_{p=1}^N (\delta \mathbf{u})^T \mathbf{f}_p$$

(3.13)

where the body force, **b**, the surface traction vector, **s**, the point load  $\mathbf{f}_p$  and the  $(\delta \mathbf{u})^T$  are given by Equation 3.14.

$$\mathbf{b} = [b_x b_y b_z]^T$$

$$\mathbf{s} = [s_x s_y s_z]^T$$

$$\mathbf{f}_p = [f_{px} f_{py} f_{pz}]^T$$

$$\delta \mathbf{u}^T = [\delta u \ \delta v \ \delta w]^T$$

(3.14)

Equations 3.6, 3.11, 3.12, 3.13 will result in

$$\int_{V} (\delta \epsilon)^{T} \sigma dV = \int_{V} (\delta \mathbf{u})^{T} \mathbf{b} dV + \int_{S} (\delta u)^{T} \mathbf{s} dS + \sum_{p=1}^{N} (\delta \mathbf{u})^{T} \mathbf{f}_{p}$$

(3.15)

$$\int_{V} (\delta \epsilon)^{T} \mathbf{D} \epsilon dV = \int_{V} (\delta \epsilon)^{T} \mathbf{D} \epsilon_{0} dV - \int_{V} (\delta \epsilon)^{T} \sigma_{0} dV + \int_{V} (\delta \mathbf{u})^{T} \mathbf{b} dV

+ \int_{S} (\delta u)^{T} \mathbf{s} dS + \sum_{p=1}^{N} (\delta \mathbf{u})^{T} \mathbf{f}_{p}$$

(3.16)

Now by discretizing the region into some elemental shapes as in Fig. 3.2, the integrations for the object can be interpreted

$$\int_{V} (\delta \epsilon)^{T} \mathbf{D} \sigma dV = \sum_{e=1}^{M} \int_{V^{e}} (\delta \epsilon)^{T} \mathbf{D} \sigma dV$$

$$\int_{S} (\delta u)^{T} \mathbf{s} dS = \sum_{e=1}^{M} \int_{S^{e}} (\delta u)^{T} \mathbf{s} dS +$$

(3.17)

where  $S^e$  and  $V^e$  denote the surface and volume for an element and M is the total number of elements. Now we can write Equation 3.15 for each of the finite elements as in

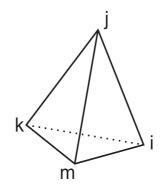

Figure 3.4: Discretizing a sphere into tetrahedron elemental shapes

$$\int_{V^e} (\delta \epsilon)^T \mathbf{D} \sigma dV = \int_{V^e} (\delta \mathbf{u})^T \mathbf{b} dV + \int_{S^e} (\delta u)^T \mathbf{s} dS + \sum (\delta \mathbf{u})^T \mathbf{f}_p$$

(3.18)

Here  $f_p$  are the external point loads applied to each node of the element.

For a 3D elemental shape e.g the tetrahedron in Fig. 3.4, we can relate the x, y and z components of the displacement vector u of an element to the x, y and z components of the displacement vector for each of its nodes using the shape functions N as follows

$$u = N_{i}(x, y, z)u_{i} + N_{j}(x, y, z)u_{j} + N_{k}(x, y, z)u_{k} + N_{m}(x, y, z)v_{m}$$

$$v = N_{i}(x, y, z)v_{i} + N_{j}(x, y, z)v_{j} + N_{k}(x, y, z)v_{k} + N_{m}(x, y, z)v_{m}$$

$$w = N_{i}(x, y, z)w_{i} + N_{j}(x, y, z)w_{j} + N_{k}(x, y, z)w_{k} + N_{m}(x, y, z)v_{m}$$

(3.19)

where  $u_i$ ,  $u_j$ ,  $u_k$ ,  $u_m$  are the x components of nodal displacements and in a similar way elements with v and w in their names are associated with y and z components. Moreover  $N_i$ ,  $N_j$ ,  $N_k$  and  $N_m$  are the four shape functions. Now if we define u and  $a^e$  as in Equation 3.20, we can obtain 3.21, with shape function N defined in Equation 3.22.

$$\mathbf{u} = [u \ v \ w]^T$$

$$\mathbf{a}^e = [u_i v_i w_i \ u_j v_j w_j \ u_k v_k w_k \ u_m v_m w_m]^T$$

(3.20)

$$\mathbf{u} = \mathbf{N}\mathbf{a}^e \tag{3.21}$$

$$\mathbf{N} = \begin{pmatrix} N_i & 0 & 0 & N_j & 0 & 0 & N_k & 0 & 0 & N_m & 0 & 0 \\ 0 & N_i & 0 & 0 & N_j & 0 & 0 & N_k & 0 & 0 & N_m & 0 \\ 0 & 0 & N_i & 0 & 0 & N_j & 0 & 0 & N_k & 0 & 0 & N_m \end{pmatrix}$$

(3.22)

combining Equations 3.3 and 3.21, we can define matrix  $\mathbf{B} = \mathbf{L}\mathbf{N}$  as the *strain-nodal displacement matrix* and therefore:

$$\epsilon = \mathbf{B}\mathbf{a}^e \tag{3.23}$$

$\bf L$  is a linear operator and if the shape function  $\bf N$  only contains linear functions (in  $\bf x$   $\bf y$  and  $\bf z$ ) then the  $\bf B$  matrix contains constant elements. Thus

$$\delta \epsilon = \delta(\mathbf{B}\mathbf{a}^e) = \mathbf{B}\delta\mathbf{a}^e \tag{3.24}$$

and

$$(\delta \epsilon)^T = (\mathbf{B} \delta \mathbf{a}^e)^T = (\delta \mathbf{a}^e)^T \mathbf{B}^T$$

(3.25)

More over for  $(\delta \mathbf{u})^T$  we will have:

$$(\delta \mathbf{u})^T = (\mathbf{N}\delta \mathbf{a}^e)^T = (\delta \mathbf{a}^e)^T \mathbf{N}^T$$

(3.26)

By substituting Equations 3.25 and 3.26 in 3.18 we can get:

$$(\delta \mathbf{a}^e)^T)\left\{\int_{V^e} (\mathbf{B}^T \sigma dV) - \int_{V^e} (\mathbf{N})^T \mathbf{b} dV - \int_{S^e} (\mathbf{N})^T \mathbf{s} dS - \sum (\mathbf{N})^T \mathbf{f}_p\right\} = 0$$

(3.27)

The term  $\delta a^e$  represents the first variation of the nodal displacements which must satisfy the displacement boundary conditions, therefore in any event  $\delta a^e$  is non-zero [52]. So it can be concluded that in general

$$\int_{V^e} (\mathbf{B}^T \sigma dV) - \int_{V^e} (\mathbf{N})^T \mathbf{b} dV - \int_{S^e} (\mathbf{N})^T \mathbf{s} dS - \sum (\mathbf{N})^T \mathbf{f}_p = 0$$

(3.28)

Therefore, for a linear elastic material for which Equation 3.6 applies, considering Equation 3.28, we can write:

$$\{\int_{V} \mathbf{B}^{T} \mathbf{D} \mathbf{B} dV\} \mathbf{a}^{e} - \int_{V} \mathbf{B}^{T} \mathbf{D} \epsilon_{0} dV + \int_{V} \mathbf{B}^{T} \sigma_{0} dV - \int_{V} \mathbf{N}^{T} \mathbf{b} dV - \int_{S} \mathbf{N}^{T} \mathbf{s} dS - \sum_{v} \mathbf{N}^{T} \mathbf{f}_{p} = 0$$

$$(3.29)$$

Finally, this equation can be written in the form

$$\mathbf{K}^e \mathbf{a}^e = \mathbf{f}^e \tag{3.30}$$

where

$$\mathbf{f}^e = \mathbf{f}_{\epsilon 0}^e - \mathbf{f}_{\sigma 0}^e + \mathbf{f}_b^e + \mathbf{f}_s^e + \mathbf{f}_{PL}^e \tag{3.31}$$

and matrix K is

$$\mathbf{K}^e = \int_V \mathbf{B}^T \mathbf{D} \mathbf{B} dV = \mathbf{B}^T \mathbf{D} \mathbf{B} V \tag{3.32}$$

V is the volume of the element which for the tetrahedron depicted in Fig. 3.2 is given by Equation 3.33.

$$V = \frac{1}{6} det \begin{pmatrix} 1 & x_i & y_i & z_i \\ 1 & x_j & y_j & z_j \\ 1 & x_k & y_k & z_k \\ 1 & x_m & y_m & z_m \end{pmatrix}$$

(3.33)

The five elemental force vectors are given by

$$\mathbf{f}_{\epsilon 0}^{e} = \int_{V} \mathbf{B}^{T} \mathbf{D} \epsilon_{0} dV$$

$$\mathbf{f}_{\sigma 0}^{e} = \int_{V} \mathbf{B}^{T} \sigma_{0} dV$$

$$\mathbf{f}_{b}^{e} = \int_{V} \mathbf{N}^{T} \mathbf{b} dV$$

$$\mathbf{f}_{s}^{e} = \int_{S} \mathbf{N}^{T} \mathbf{s} dS$$

$$\mathbf{f}_{PL}^{e} = \sum_{S} \mathbf{N}^{T} \mathbf{f}_{p}$$

$$(3.34)$$

$\mathbf{K}^e$  is called the *elemental stiffness matrix*. Now the only remaining step is the assemblage of the global equations based on the elemental equations. For the global stiffness and force matrix we have:

$$\mathbf{K} = \sum global(\mathbf{K}^e)$$

$$\mathbf{f} = \sum global(\mathbf{f}^e)$$

(3.35)

where global() is a mapping function from element node numbers to global node numbers. For the tetrahedral elements like the one shown in Fig. 3.2, the global stiffness matrix can be obtained through following two steps as in Equations 3.36 and 3.37.

$$K^{e} = \begin{pmatrix} K_{i,i}^{e} & K_{i,j}^{e} & K_{i,k}^{e} & K_{i,m}^{e} \\ K_{j,i}^{e} & K_{j,j}^{e} & K_{j,k}^{e} & K_{j,m}^{e} \\ K_{k,i}^{e} & K_{k,j}^{e} & K_{k,k}^{e} & K_{k,m}^{e} \\ K_{m,i}^{e} & K_{m,i}^{e} & K_{m,k}^{e} & K_{m,m}^{e} \end{pmatrix}$$

(3.36)

Using the elemental stiffnes matrices, we can assemble the global stiffness matrix

as 3.37.

$$\mathbf{K} = \begin{pmatrix} \mathbf{K_{1,1}} & \mathbf{K_{1,2}} & \mathbf{K_{1,3}} & \cdots & \mathbf{K_{1,N}} \\ \mathbf{K_{2,1}} & \mathbf{K_{2,2}} & \mathbf{K_{2,3}} & \cdots & \mathbf{K_{2,N}} \\ \mathbf{K_{3,1}} & \mathbf{K_{3,2}} & \mathbf{K_{3,3}} & \cdots & \mathbf{K_{3,N}} \\ \vdots & \vdots & \vdots & \vdots & \vdots \\ \mathbf{K_{N,1}} & \mathbf{K_{N,2}} & \mathbf{K_{N,3}} & \cdots & \mathbf{K_{N,N}} \end{pmatrix}$$

$$\mathbf{K_{I,J}} = \sum_{e=1}^{M} \mathbf{K_{I,J}}^{e} \quad I = 1 : N, J = 1 : N$$

(3.37)

where M is the maximum number of elements and N is the maximum number of nodes in these equations.  $K_{I,J}^e$  will be assumed a null matrix if element e does not consist nodes I and J. It should be noted that I and J indices here refer to node numbers in global node numbering.

## 3.3 Applying Constraints

Without the substitution of a minimum number of constraint nodes to prevent rigid body movements of the structure, it is impossible to solve this system. The reason is that the displacements cannot be uniquely determined by the forces in such a situation. This obvious physical fact will interpret as singularity of **K** matrix in mathematics aspect [49]. Therefore, some of the nodes need to be fixed to predetermined positions. To this end, the global stiffness matrix has to change. The change is applied by making the corresponding rows and columns to that node zeros and making the diagonal elements one. Then the force vector should

be modified to reflect the change in stiffness matrix, only the elements of force vector corresponding to the fixed nodes will not change. For example assume that we want to make  $N^{th}$  node fixed, that is the displacement vector for  $\mathbf{u}^N = [u_N v_N w_N]$  will be set to zero, in the global stiffness matrix all the elements in the rows and columns with indexes 3N-2, 3N-1, 3N should be set to zero except the diagonal elements which will be set to ones, Equation 3.38 illustrates the changes in K matrix and f vector after applying changes to row and column 3N.

$$\mathbf{K} = \begin{pmatrix} k_{1,1} & \cdots & k_{1,3N-1} & 0 \\ \vdots & \vdots & \vdots & \vdots \\ k_{3N-1,1} & \cdots & k_{3N-1,3N-1} & 0 \\ 0 & \cdots & 0 & 1 \end{pmatrix} \mathbf{u} = \mathbf{f} = \begin{pmatrix} f_1 - w_N^0 k_{1,3N} \\ \vdots \\ f_{3N-1} - w_N^0 k_{3N-1,3N} \\ w_N^0 \end{pmatrix}$$

(3.38)

## 3.4 Dynamic FE Modeling

In static analysis of FE, we came up with the equation  $\mathbf{K}\mathbf{u}=\mathbf{f}$ , hence we neglected the terms in force resulting from the acceleration and velocity while the general formula for obtaining the force is:

$$M\ddot{\mathbf{u}} + C\dot{\mathbf{u}} + K\mathbf{u} = \mathbf{R} \tag{3.39}$$

Where **M**, **C** and **K** are mass, damping and stiffness matrices respectively and **R** is the external load vector defined as

$$\mathbf{R}(t) = \mathbf{F}_I(t) + \mathbf{F}_D(t) + \mathbf{F}_E(t) \tag{3.40}$$

Where  $\mathbf{F}_I(t)$  corresponds to inertia forces,  $\mathbf{F}_I(t) = \mathbf{M}\ddot{u}$ ,  $\mathbf{F}_D(t)$  represents the damping forces  $\mathbf{F}_D(t) = \mathbf{C}\dot{u}$  and  $\mathbf{F}_E(t)$  are the elastic forces,  $\mathbf{F}_E(t) = \mathbf{K}u$ . [32]

the decision that which of the dynamic or static models should be used is an engineering judgement because dynamic analysis would increase the computational effort needed to solve the equations. Equation 3.39 is a second order differential equation with constant coefficients [53,54].

In the following we will describe the *Newmark* direct integration method which we have applied in our dynamic simulation.

#### The Newmark Method

In the Newmark integration scheme the following assumptions are used:

$$\dot{\mathbf{u}}^{t+\Delta t} = \dot{\mathbf{u}}^t + [(1-\delta)\ddot{\mathbf{u}}^t + \delta\ddot{\mathbf{u}}^{t+\Delta t}]\Delta t$$

$$\mathbf{u}^{t+\Delta t} = \mathbf{u}^t + \dot{\mathbf{u}}^t \Delta t + [(\frac{1}{2} - \alpha)\ddot{\mathbf{u}}^t + \alpha^{t+\Delta t}\ddot{\mathbf{u}}^t]\Delta t^2$$

(3.41)

Where  $\alpha$  and  $\delta$  are parameters that can be determined to obtain stability and accuracy. In general these parameters should satisfy the conditions [32]:

$$\delta \geqslant 0.5$$

$$\alpha \geqslant 0.25(0.5 + \delta)^2$$

(3.42)

Newmark originally proposed the trapezoidal rule for unconditionally stable scheme with  $\delta=0.5$  and  $\alpha=0.25$ .

Also  $\Delta t$  in the simulation should not be bigger than a certain value  $\Delta t_{cr}$  in order to maintain stability. This value is determined by the characteristics of the worst

element in the mesh.

For solving the dynamic equation after finding the **K**, **M** and **C** matrices and determining parameter values we form  $\hat{\mathbf{K}} = \mathbf{K} + a_0 \mathbf{M} + a_1 \mathbf{C}$  then at each step of the simulation we have to do the following tasks [32]:

1. calculate effective loads at time  $t + \Delta t$

$$\hat{\mathbf{R}}^{t+\Delta t} = \mathbf{R}^{t+\Delta t} + \mathbf{M}(a_0 \mathbf{u}^t + a_2 \dot{\mathbf{u}}^t + a_3 \ddot{\mathbf{u}}^t) + \mathbf{C}(a_1 \mathbf{u}^t + a_4 \dot{\mathbf{u}}^t + a_5 \ddot{\mathbf{u}}^t)$$

(3.43)

2. solve displacements at time  $t + \Delta t$ :

$$\hat{\mathbf{K}}\mathbf{u} = \hat{\mathbf{R}}^{t+\Delta t}$$

3. calculate accelerations and velocities at time  $t + \Delta t$

$$\ddot{\mathbf{u}}^{t+\Delta t} = a_0(\mathbf{u}^{t+\Delta t}) + a_2\dot{\mathbf{u}}^t + a_3\ddot{\mathbf{u}}^t$$

$$\dot{\mathbf{u}}^{t+\Delta t} = \dot{\mathbf{u}}^t + a_6\ddot{\mathbf{u}}^t + a_7\ddot{\mathbf{u}}^{t+\Delta t})$$

(3.44)

Where  $a_0$  to  $a_7$  are defined as:

$$a_0 = \frac{1}{\alpha \Delta t^2} \quad a_1 = \frac{\delta}{\alpha \Delta t} \quad a_2 = \frac{1}{\alpha \Delta t} \quad a_3 = \frac{1}{2\alpha} - 1$$

$$a_4 = \frac{\delta}{\alpha} - 1 \quad a_5 = \frac{\Delta t}{2} (\frac{\delta}{\alpha} - 2) \quad a_6 = \Delta t (1 - \delta) \quad a_7 = \delta \Delta t$$

$$(3.45)$$

## Chapter 4

# **Conjugate Gradient Algorithm**

As shown in Chapter 3, the application of the FEM to a linear elastic deformation model will result in a large but sparse system of equations in the form of:

$$\mathbf{K}\mathbf{u} = \mathbf{b} \tag{4.1}$$

In this chapter we will discuss different solvers for such equations and will review our fixed point implementation of CG algorithm which is based on the method proposed by Mafi et al. in [48].

## 4.1 Algorithms for Solving Kx = b

For solving linear systems of equations, in principle, there are two choices: direct methods and iterative methods, each having some advantages over the other depending on the matrix type and application of interest, several direct and iterative methods have been developed for solving large and sparse systems of equations [55, 56]. One of the main advantages of iterative methods in the case of sparse systems is their lower memory consumption since only the non-zero elements of the matrix need to be stored. This reduces the usage of memory resources from an  $O(N^2)$  to O(N), where N is the size of the matrix. However this is not necessarily the case in direct methods. For example, direct methods based on matrix factorization can lead to the decomposition of a sparse matrix into new matrices which are not as sparse as the original matrix. Furthermore, iterative methods lend themselves for hardware-based parallelization better than direct methods [55]. It should also be noted that in haptics applications, even when a linear elastic model is used, matrix K can change depending on the contact node [1]. Moreover, nonlinear FE modeling of deformation can lead to a matrix K which would be dependent on the deformation X. Therefore, this precludes the possibility of performing off-line calculations to obtain the inverse matrix or its factorization. Among the the iterative techniques, the Conjugate Gradient (CG) method is probably the most suitable method for our application. The system of equations generated by the FEM is a sparse, symmetric and positive definite as required by the original CG algorithm. From a numerical perspective, the CG method is usually more robust and less computationally intensive than some other more general it-

erative methods such as BiCGStab or GMRES [55,57].

# 4.2 Fixed-Point Implementation of CG on Multiple FP-GAs

In [1], we proposed an adaptive fixed-point implementation of the Conjugate Gradient (CG). Compared to floating-point operations, fixed-point calculations use significantly less hardware resources allowing for much greater parallelization of the computations. Static and dynamic scalings were proposed to reduce inaccuracies due to quantization errors and to avoid data overflows.

In this thesis the same method has been applied for the CG implementation with increased resolution for vectors and scalars which results in more accuracy of results. A pseudo-code of the CG algorithm for solving  $\mathbf{K}\mathbf{x} = \mathbf{b}$  for  $\mathbf{x}$  is given below. Here #m is the maximum number of iterations and  $\varepsilon$  is the error tolerance. Theoretically, getting the results from the CG algorithm requires m = length of b vector, but in our simulation we could obtain acceptable results in less CG iterations as will be discussed in this section.

1. x = init; %initial guess for solution of Kx=b

2.  $b = b/Static\_factor$ ; %static scaling for b vector

3.  $\mathbf{r} = \mathbf{b} - \mathbf{K} * \mathbf{x}$ ; %residue

4. d = r; %initial "search direction"

5. cntr = 1;

6. rr = r' \* r;

7. rr0 = rr;

- 8.  $dyn_{-}factor = 0$ ;

- 9.  $dyn_{-}flag = 0$ ;

- 10. while  $(rr > \varepsilon^2 * rr0 \& cntr < \#m)$

- 11. if (rr < dynamic scaling threshold) dyn\_flag=1, dyn\_factor=dyn\_factor+1; % applying dynamic scaling

- 12.  $\alpha = \text{static\_factor * rr / } (\mathbf{d' * K * d});$

- 13.  $\alpha = \alpha << \text{dyn_flag};$  %dynamic scaling effect on  $\alpha$

- 14.  $\mathbf{x} = \mathbf{x} + (\alpha * \mathbf{d}) >> dyn_-factor;$  %update approximate solution, applying dynamic scaling

- 15.  $\mathbf{rn} = \mathbf{r} \alpha/static\_factor * \mathbf{K} * \mathbf{d};$  %update the residue

- 16. rrn = rn' \* rn;

- 17.  $\beta = (rrn/rr) >> (2 * dyn_-flag);$

- 18.  $\mathbf{d} = \mathbf{rn} + \beta * \mathbf{d}$ ; %update search direction

- 19. r = rn;

- 20. rr = rrn;

- 21. if (dyn\_flag==1) dyn\_flag=0;

- 22. cntr = cntr + 1;

- 23. *end*

For fixed point Implementation of CG algorithm we utilize the same approach as proposed by Mafi et.al in [1]. The numerical stability and convergence of this method has been proved in the same reference. In this method two different types of scaling have been utilized to improve its numerical accuracy, reliability and convergence rate. Namely *static scaling* and the *dynamic scaling*. In our implementation the elements of **K** matrix as well as **b** vector are defined as 18 bits. **x** vector elements have 36 bits. These bit widthes have been chosen considering limitations imposed by FPGA resources while trying to maximize number of nodes handled by each FPGA and accuracy of results. More details on choosing bit widthes will be presented later in this chapter.

One can note that without proper scaling, the result of the multiplication Kx with the given bitwidths for the K and x can easily overflow the 18-bit vector b. To tackle this problem, the proposed static scaling scheme, vectors  $\mathbf{b}$ ,  $\mathbf{r}$  and  $\mathbf{d}$  are scaled down by static scaling factor  $2^m$ . This is performed by scaling down  $\mathbf{b}$  vector which is performed in Step 2 of the CG algorithm. To compensate for this scaling down when updating  $\mathbf{x}$  vector in Step 12, the value used for  $\alpha$  is up scaled with the static scaling factor. The proper choice of scaling factor m generally depends on the norm of the actual matrix  $\mathbf{K}$ . Fig. 4.1 The static scaling method saves us a huge amount of memory due to less memory bits needed compared to non-scaled approach for storing the values of the vectors. However it may result in loss of some bits of data in LSB position for b vector.

Moreover by looking at the pseudo code of the CG, one can observe that as the algorithm nears the actual solution, the vectors  $\mathbf{r}$  and  $\mathbf{d}$  will become smaller down

Figure 4.1: Static Scaling. original figure with different bitwidths by Ramin Mafi to the values comparable with quantization errors. Hence as the size of vector becomes smaller, quantization errors can significantly alter its direction. In the CG algorithm, the updated **d** vector in each iteration is supposed to be a new basis vector for the span of K matrix and by updating **x** vector, we add the projection of the actual solution on new **d** vector direction to vector **x**. In this algorithm, **r** vector is used to find the length of this projected vector.

Therefore, such errors in  $\mathbf{r}$  and  $\mathbf{d}$  vector results in  $\mathbf{x}$  vector updates leading the  $\mathbf{x}$  to wrong directions. This will make quantization errors significant. To mitigate this problem, a dynamic scaling has been employed which scales up  $\mathbf{r}$  and  $\mathbf{d}$  when  $\|r\|$  falls down a certain value. This up-scaling of  $\mathbf{r}$  and  $\mathbf{d}$  vectors will decrease relative error in these vectors caused by quantization errors. Finally, for correct update in  $\mathbf{x}$  the added vector to  $\mathbf{x}$  in Step 14 of the pseudo code would be scaled down by the same factor. For further details on the fixed point CG implementation the reader is

referred to [42].

The bitwidth selections for the matrix and various vectors in the implementation of CG are illustrated in Table. 4.1. As will be addressed in Section 6.1, the data bitwidths have been chosen to be multiples of 9. On the other hand, increase in data bitwidths will reduce quantization errors and increase accuracy but will increase resource usage of the FPGAs, resulting in reduced size of K matrix. For a compromise between the accuracy of the fixed-point implementation results and the size of FE mesh we chose the bitwidth for vectors to be 18. Obviously **Kd** would need more bits. Due to our experiments to avoid over flows in **Kd**, it requires 36 bits. Finally the reason to choose 36 bitwidth for x vector is to get more accurate results from our fixed-point divider unit which calculates  $\alpha$  and  $\beta$  values. For his objective we up-scale the dividend, resulting in up-scaled  $\alpha$  and  $\beta$  coefficients. For compensation, we should down-scale the resulted  $\alpha$  and  $\beta$ , But for getting more accuracy in results, while updating x vector in the algorithm we use the same upscaled version of  $\alpha$  in step 14 of the pseudo code. Hence, to avoid overflow in x vector its bitwidth is chosen to be 36 instead of 18. This will increase accuracy in x vector by using 9 more M9k memory blocks in our design which is a negligible increase in resource usage of the FPGA.

The fixed-point CG algorithm for solving system of 1707 equations has been implemented using the bitwidth assignment in Table. 4.1 and Matlab's fixed point toolbox. The error in the result vector is depicted in Table. 4.2 for different number of iterations. Fig. 4.2 also depicts the change in norm of the error as a function of the number of iterations. It is observed that after performing 30 CG iterations, the relative error in x vector drops under 5%. Furthermore, in Chapter 7, monte

|          | bitwidth |

|----------|----------|

| K        | 18       |

| X        | 36       |

| r        | 18       |

| b        | 18       |

| d        | 18       |

| Kd       | 36       |

| rr       | 64       |

| dkd      | 64       |

| $\alpha$ | 18       |

| $\beta$  | 18       |

|          |          |

Table 4.1: Bitwidths assigned for scalars, vectors and K matrix in the fixed-point implementation of the CG

carlo type simulations have been carried out for test of numerical stability of this platform. In those tests the dynamic scaling is set to a smaller value which results in faster convergence before 30 iterations and slower rate afterwards.

It is worth mentioning that for this simulation the initial guess for  $\mathbf{x}$  vector has been set to zero, while in haptic simulation in each simulation step we use the result of the previous simulation step as the initial guess. This starting point for  $\mathbf{x}$  vector is often more close to the actual result, and will result in a more precise answer for  $\mathbf{x}$  vector in a fixed number of CG iterations. The reason for the last obtained  $\mathbf{x}$  vector being a good initial guess for the  $\mathbf{X}$  vector of the next step is that, because of the high update rate (100-1000Hz) the deformation changes in the object caused by the human operator is usually small during a sample time. Thus the new deformation vector would be close to the deformation vector in the last simulation step.

Figure 4.2: Changes in the norm of error in fixed point implementation of the CG as a function of the number of iterations