## **Dynamically-Scheduled Machines**

• In a **Statically-Scheduled machine**, the compiler schedules all instructions to avoid data-hazards: the ID unit may require that instructions can issue together without hazards, otherwise the ID unit inserts **stalls** until the hazards clear

• This section will deal with **Dynamically-Scheduled machines**, where **hardwarebased** techniques are used to detect are remove avoidable data-hazards automatically, to allow '**out-of-order**' execution, and improve performance

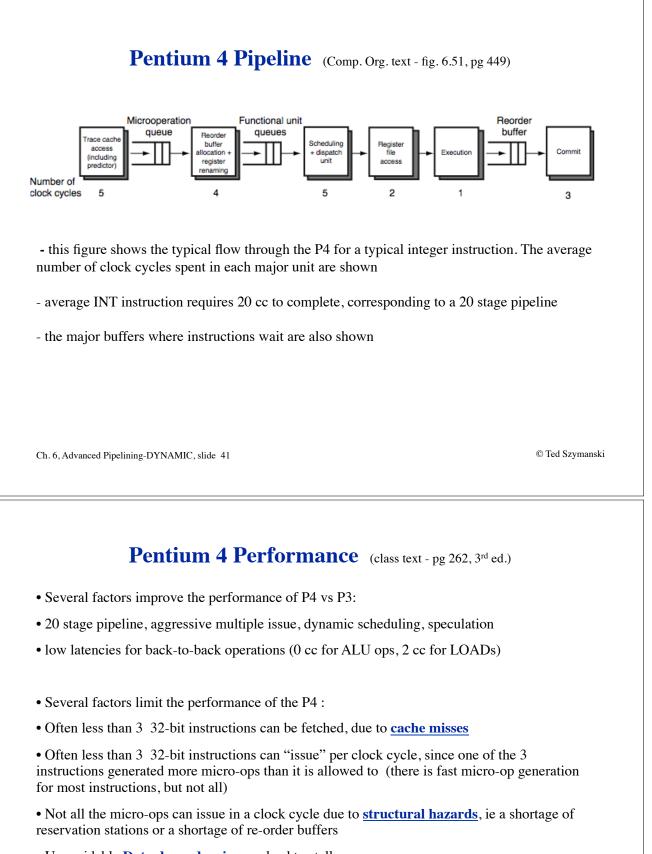

• Dynamic scheduling used in the Pentium III and 4, the AMD Athlon, the MIPS R10000, the SUN Ultra-SPARC III; the IBM Power chips, the IBM/Motorola PowerPC, the HP Alpha 21264, the Intel Dual-Core and Quad-Core processors

• In contrast, **static multiple-issue** with compiler-based scheduling is used in the Intel IA-64 **Itanium** architectures

• In 2007, the dual-core and quad-core Intel processors use the Pentium 5 family of **dynamically-scheduled** processors. The Itanium has had a hard time gaining market share.

Ch. 6, Advanced Pipelining-DYNAMIC, slide 1

© Ted Szymanski

#### **Dynamic Scheduling - the Idea**

(class text - pg 168, 171, 5th ed.)

| DIVD | <b>F0</b> , F2, F4        |                                      |

|------|---------------------------|--------------------------------------|

| ADDD | F10, <mark>F0</mark> , F8 | - data hazard, stall issue for 23 cc |

| SUBD | F12, F8, F14              | - SUBD inherits 23 cc of stalls      |

• ADDD depends on DIVD; in a static scheduled machine, the **ID unit** detects the hazard and causes the basic pipeline to stall for 23 cc

• The SUBD instruction cannot execute because the pipeline has stalled, even though SUBD does not logically depend upon either previous instruction

• suppose the machine architecture was re-organized to let the SUBD and subsequent instructions "<u>bypass</u>" the previous stalled instruction (the ADDD) and proceed with its execution -> we would allow "**out-of-order**" execution

• however, out-of-order execution would allow out-of-order completion, which may allow RW (Read-Write) and WW (Write-Write) data hazards

• a RW and WW hazard occurs when the reads/writes complete in the wrong order, destroying the data. We would need to handle these hazards.

#### **Dynamic Scheduling - the Idea**

(class text, pg. 169)

| DIVD | <b>F0</b> , F2, F4                |

|------|-----------------------------------|

| ADDD | <b>F6</b> , <b>F0</b> , <b>F8</b> |

| SUBD | <b>F8</b> , F10, F14              |

| MULD | <b>F6</b> , F10, F8               |

• there is a RW data hazard between ADDD and SUBD (ADDD reads **F8**, SUBD writes **F8**, even though there is no logical flow of information between the instructions); if they execute in the wrong order the program is incorrect; in a **statically-scheduled machine**, the **ID Unit** will stall to preserve order of R & W

• there is an WW data-hazard between ADDD and MULD (both write **F6**, even though there is no logical flow of information between the two instructions); if they execute in the wrong order the program is incorrect; in a **statically scheduled machine**, the **ID Unit** will stall to preserve order of W & W

• these problems can be solved, and this code sequence can execute as fast as possible, by using "Tomasulo's algorithm" (also called "Dynamic Scheduling")

Ch. 6, Advanced Pipelining-DYNAMIC, slide 3

© Ted Szymanski

#### **Dynamic Scheduling - the Idea**

| DIVD | <b>F0</b> , F2, F4                                                       |

|------|--------------------------------------------------------------------------|

| ADDD | <b>F6</b> , <b>F0</b> , <b>F8</b> - unavoidable data hazard, stall 23 cc |

| SUBD | <b>F8</b> , F10, F14                                                     |

| MULD | <b>F6</b> , F10, <b>F8</b>                                               |

• Here is the same example ; in a static machine, the **ID unit** will stall the **ADDD** until the hazards clear

• suppose we create some temporary registers, called nF6 and nF8, and we "rename" the second occurrences of F6 and F8 to use these new registers; this sequence avoids the hazards, and is logically equivalent (gives the same answer):

| DIVD | <b>F0</b> , F2, F4        |

|------|---------------------------|

| ADDD | F6, <b>F0</b> , <b>F8</b> |

| SUBD | n <b>F8</b> , F10, F14    |

| MULD | nF6, F10, <b>nF8</b>      |

• we can now let the SUBD and MULD instructions execute **out-of-order**, since there are no RW or WW hazards

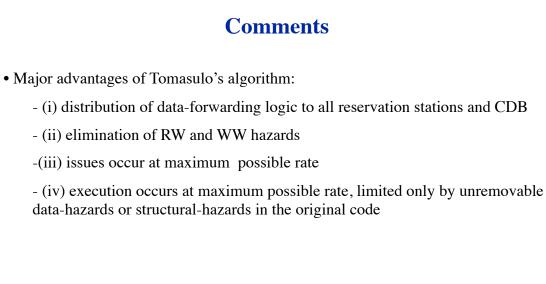

## **Tomasulo's Algorithm = Dynamic Scheduling**

• Most advanced CPUs (PowerPC, MIPS, Pentium) now implement **Tomasulo's** algorithm, originally proposed in 1960s for large supercomputers

• Basic ideas:

- (i) hardware can unroll loops and execute multiple iterations optimally, without compiler loop unrolling and scheduling

- (ii) hardware automatically bypasses "data hazards" without stalling pipelines whenever possible

- (iii) hardware **issues** instructions at maximum rate without data hazard stalls; ID **never stalls due to data-hazards**; it only stalls due to **structural-hazards**

• hardware performs "**register-renaming**" function automatically, eliminating RW and WW data-hazards - this is probably the trickiest part of

Ch. 6, Advanced Pipelining-DYNAMIC, slide 5

© Ted Szymanski

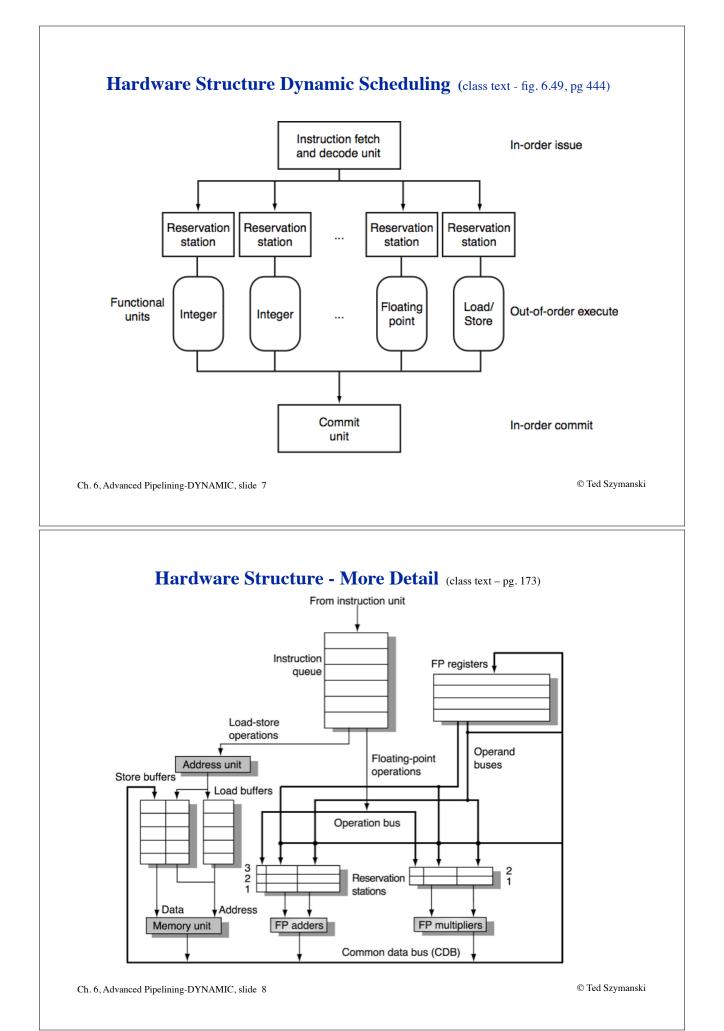

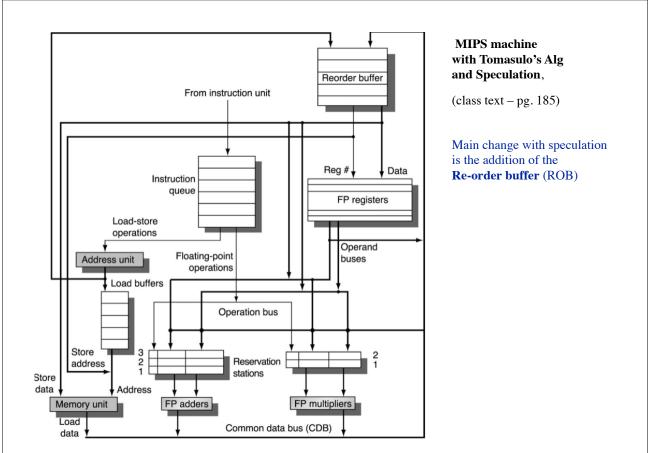

# Hardware Organization (class text - pg. 173,174)

• How "dynamic scheduling" is accomplished:

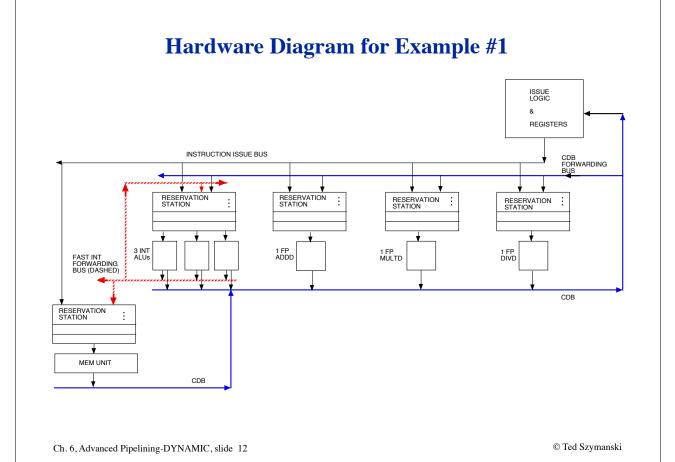

- (i) several Functional Units (FUs), i.e., MULT, DIV, SRT, ADD/SUB, etc

- (ii) each **Functional Unit** contains a "**Reservation Station**", which queues several instructions to be performed and their operands if they are ready. If operands are not ready, it queues pointers to other **FU**s that will **produce** the operands (these pointers are called "**tags**")

-(iii) as an instruction is **issued** at the **Instruction Queue (ID stage)**, its (**operands** are **pre-fetched**) **OR** (**tags** are **pre-fetched**) from the registers and stored along with the instruction in the appropriate Reservation Station

- basically, an instruction copies its operands when it issues, and takes its operands with it to the reservation station, if the operands are ready; if the operand(s) are not ready, the instruction takes an 'I-owe-you' (IOU or "pointer" or 'tag') for the operand and will capture the operand once it is computed using the IOU

- an operand can move directly from a "**producer**" FU to a "**consumer**" RS, bypassing the register file and removing all data-hazards

## **Dynamic Scheduling : Tomasulo's Algorithm**

- (iv) new results computed in a Functional Unit are **broadcasted** to all Reservation Stations (via a broadcast over the "**Common Data Bus**"), and written back to registers at same time

- Net affect: to eliminate all the RW and WW **data hazards** involved with reading and writing to registers; this solution relies upon broadcasting results as they become available to all Reservation Stations who took an **IOU** for the result

• Tomasulo's algorithm decouples instruction **issue** from instruction **execution**; the algorithm will keep issuing instructions (in the ID stage) as long as there is room in the Reservation Stations; it <u>never stalls</u> instruction issues due to data-hazards

• Instruction Issues will only stall if a Reservation Station is full (structural hazard)

• A data hazard cannot cause instruction issues to stall in **dynamic-scheduling**; Compare with a **linear static-scheduled pipeline**: If a LOAD results in a cache miss, the entire pipeline must stall until the memory read is completed, which can take 100s cc. The entire pipeline must stall, because the Load cannot move into the Write-Back stage until it is ready to write. Other instructions must stall, because they cannot "**bypass**" the Load.

Ch. 6, Advanced Pipelining-DYNAMIC, slide 9

© Ted Szymanski

#### Three Basic Steps (ref text - pg. 174)

• 3 main steps to complete an instruction, each can take many clock cycles:

• (1) **ISSUE**: get instruction from Instruction Queue; if there is an empty Reservation Station for the instruction (ie ADD, MULT, DIV), then issue the instruction to the RS, and fetch its operands if they are available and forward to the RS; otherwise, forward a "tag" (a pointer to the FU that will generate the operand(s)) to RS (this implements "*register renaming*"). If there is no empty RS for the instruction, we have a structural-hazard and must stall pipeline

• (2) **EXECUTE**: at every RS: if operand is not ready, monitor the CDB waiting for that register to be written by the correct producer; copy the result into the RS when it appears on the CBD using the **IOU** (or **tag**) When both operands are ready, execute the instruction if FU is not busy, or label instruction as ready to execute if the FU is busy

• (3) **WRITE RESULT**: at every FU: when a result is computed, write it over the Common Data Bus to the destination register and to any waiting Reservation Stations that have an IOU for that operand

• all WW and RW data-hazards are automatically avoided, through the register renaming process

• data structures to implement the logic are distributed through the Reservation Stations

|                                   | xample -          | #1- Sequ           | ience of       | f Instruct          | tions                          |

|-----------------------------------|-------------------|--------------------|----------------|---------------------|--------------------------------|

|                                   | _                 |                    |                |                     |                                |

| Single-Iss                        | Je, Dvna          | mic Sche           | edulina        |                     |                                |

|                                   |                   |                    | <b>j</b>       |                     |                                |

| Assumptions:                      |                   |                    |                |                     |                                |

| (1) FP ADDER is a 4               | stage pipeline, I | FP MULT is an 8 s  | stage pipeline |                     |                                |

| (2) FP DIV is a 24 st             | age unit, non-p   | ipelined           |                |                     |                                |

| (3) Write-Back (WB)               | takes 1 cc        |                    |                |                     |                                |

| (3) FP Data forward               | ng occurs in Wr   | rite-Back (WB) co  | C              |                     |                                |

| except for intege                 | er forwarding (w  | which takes 0 cc)  |                |                     |                                |

| (4) the EX column sl              | nows the execu    | tion times in the  | integer ALU u  | nit, and the FP uni | ts, to save space              |

| (5) Multiple Integer A            | LU units, to av   | oid structural haz | zards          |                     |                                |

| (6) Mem read/write                | take 1 cc (we h   | nave perfect men   | nory with cac  | ne hits)            |                                |

| (7) Reservation-stat              | ions are infinite | ly deep (there ar  | e no structura | l hazards)          |                                |

|                                   |                   |                    |                | Forwarding/         |                                |

| Instruction                       | Issue cc          | Execute cc         | Mem cc         | Write-Back cc       | Hazard                         |

| LD <b>F6</b> , 34(R2)             | 1                 | 2                  | 3              | 4                   |                                |

|                                   | 2                 | 2                  | 4              | 5                   |                                |

| LD F2, 45(R3)<br>MULTD F0, F2, F4 | 3                 | 613                | 4              | 14                  | wait for F2, forwarded in cc 5 |

| SUBD F8, F6, F2                   | 4                 | 69                 |                | 14                  | wait for F2, forwarded in cc 5 |

| DIVD F10, F0, F6                  |                   | 1538               |                | 39                  | wait for F0, forwarded in cc 1 |

| ADDD F6, F8, F2                   | 6                 | 1114               |                | 15                  | wait on F8, forwarded in cc 1  |

| ADDD FO, FO, FZ                   | 0                 | 1114               |                | 15                  | wait off Fo, forwarded in cc 1 |

•

Ch. 6, Advanced Pipelining-DYNAMIC, slide 13

© Ted Szymanski

# **Example #2 - Concept of 'Tags' for Operands**

|              | EXAMPLE: INI            | TIAL STAT         | E, Registers        | (and 'I | OU's for Opera     | ands)         |                 |               |         |

|--------------|-------------------------|-------------------|---------------------|---------|--------------------|---------------|-----------------|---------------|---------|

|              |                         |                   |                     |         |                    | Register      | Valid           | Producer      | Write-# |

|              | instruction             | Operand A         | Operand B           |         |                    |               |                 |               |         |

| Instruction  |                         |                   |                     | 1       | FO                 | 0             | 1               |               |         |

| Queue        |                         |                   |                     |         | F2                 | 20            | 1               |               |         |

|              | MULTD F6,F8,F12         | F8                | F12                 |         | F4                 | 60            | 1               |               |         |

| j+3          |                         | F8                | F12                 |         | F6                 | 0             | 1               |               |         |

| j+2          | MULTD F12,F6,F8         |                   | F8                  |         | F8                 | 0             | 1               |               |         |

| j+1          | SUBD F8,F6,F2           | F6                | F2                  | 1       | F10                | 0             | 1               | 1             |         |

| j            | ADDD F6,F4,F2           | F4                | F2                  | 1       | F12                | 0             | 1               | [             |         |

| -            |                         |                   |                     |         | F14                | 0             | 1               | 1             |         |

| ID Unit      |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

| Consider the | e state of the register | rs on the left, a | as the instructions | issue.  | together, a (produ | cer and write | -#) form an 'I( | OU' for an op | erand   |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              | RESERVATION-STATI       | ON                |                     |         | RESERVATION-STA    | TION          |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     | _       |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 | 4             |         |

|              |                         |                   |                     | 4       |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 | 1             |         |

|              |                         |                   |                     |         |                    | _             |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              |                         |                   |                     |         |                    |               |                 |               |         |

|              | FP ADD/SUB PIPELIN      |                   |                     |         | FP MULT Pipeline   |               |                 |               |         |

• state of registers, before any instruction has issued.

|              | EXAM       | PLE: FIN     | AL STATE.         | Registers (a     | and 'IOU | 's for Operand      | ls)                 |                  |               |         |

|--------------|------------|--------------|-------------------|------------------|----------|---------------------|---------------------|------------------|---------------|---------|

|              |            |              | ,                 |                  |          |                     |                     |                  |               |         |

|              |            |              |                   |                  |          |                     | Register            | Valid            | Producer      | Write-# |

|              | instruct   | ion          | Operand A         | Operand B        |          |                     |                     |                  |               |         |

| Instruction  |            |              |                   |                  |          | F0                  | 0                   | -                |               |         |

| Queue        |            |              |                   |                  |          | F2                  | 20                  | -                |               |         |

|              | MULTD      | F6,F8,F12    |                   | F12              |          | F4                  | 60                  |                  |               |         |

| j+3          | ADDD       | F6,F8,F12    |                   | F12              |          | F6                  | 0                   |                  | FP-MULTD      |         |

| j+2          |            | F12,F6,F8    |                   | F8               |          | F8                  | 0                   |                  | FP-SUB        | _       |

| j+1          |            | F8,F6,F2     | F6                | F2               |          | F10                 | 0                   |                  |               | _       |

| j            | ADDD       | F6,F4,F2     | F4                | F2               |          | F12                 | 0                   | -                | FP-MULT       | _       |

|              |            |              |                   |                  |          | F14                 | 0                   | 1                |               |         |

| ID Unit      |            |              |                   |                  |          |                     |                     |                  |               |         |

|              |            |              |                   |                  |          |                     |                     |                  |               |         |

| C            |            |              |                   | the least street | 1        |                     |                     |                  |               |         |

| Consider the | e state or | the register | s on the left, as | the instructions |          | producer, a registe | r and a write #)    | form on ITOUI fo |               |         |

|              |            |              |                   |                  |          | FP-ADD(F6,1) denote |                     |                  |               |         |

|              |            |              |                   |                  | Example: | rP-ADD(r6,1) denote | s the first write i | o ro by the re-  | ADD TUTICUOTA | arumic  |

|              | DESEDV     | ATION-STATI  | ON                |                  |          | RESERVATION-STAT    | ION                 |                  |               |         |

|              | KEDEK      |              |                   |                  |          | RESERVATION STAT    | 1011                |                  |               |         |

|              |            |              |                   |                  |          |                     |                     |                  |               |         |

|              |            |              |                   |                  | 1        |                     |                     |                  | 1             |         |

|              |            |              |                   |                  |          |                     |                     |                  | 1             |         |

|              | ADDD       | F6,F8,F12    | FP-ADD(F6,1)      | FP-MULT(F12,1)   | 1        |                     |                     |                  |               |         |

|              | SUBD       | F8,F6,F2     | FP-ADD(F6,1)      | 20               | 1        | MULTD F6,F8.F12     | FP-SUB(F8,1)        | FP-MULT(F12,1)   |               |         |

|              | ADDD       | F6,F4,F2     | 60                | 20               | 1        | MULTD F12,F6,F8     | FP-ADD(F6,1)        | FP-SUB(F8,1)     | 1             |         |

|              |            |              |                   |                  |          |                     |                     | /                |               |         |

|              |            |              |                   |                  |          |                     |                     |                  |               |         |

|              |            |              |                   |                  |          |                     |                     |                  |               |         |

|              | FP ADD/    | SUB PIPELIN  | IE                |                  |          | FP MULT Pipeline    |                     |                  |               |         |

• we assume no functional unit has started execution yet, since we are trying to show the data forwarding using IOUs

Ch. 6, Advanced Pipelining-DYNAMIC, slide 15

© Ted Szymanski

## **Dynamic Loop Unrolling** (text, pg 179)

• Consider the loop to multiply a vector by a scalar in F31;

| Loop: | LD   | F0, 0(R1)   | ; R1 = pointer to element in memory   |

|-------|------|-------------|---------------------------------------|

|       | MULD | F4, F0, F31 | ; add scalar in F2, store in F4       |

|       | SD   | 0(R1), F4   | ; store into memory                   |

|       | SUBI | R1, R1, #8  | ; dec pointer by 8 bytes (size of FP) |

|       | BNEZ | R1, Loop    |                                       |

• lets assume "cancelling branches-PREDICT-TAKEN" (ie predict that branches are always taken)

• Tomasulo's algorithm will <u>unroll the loop and issue as many instructions as it can</u>, until it encounters a **structural-hazard** - effectively decouples the issue from the computation !

• hardware dynamically unrolls the loop and eliminates all RW and WW data-hazards

• Tomasulo's algorithm does not require many temporary FP registers to store intermediate results, since intermediates are <u>implicitly stored</u> in the Reservation Station Buffers. Recall that when the compiler unrolled the loop, we needed many extra FP registers to avoid RW and WW hazards.

# Example #3 - Automatic Loop Unrolling, Single Issue

(Example done in class, 2012)

|               | Accum   | nptions (same a   | s before)      |                  |                  |                   |                          |               |

|---------------|---------|-------------------|----------------|------------------|------------------|-------------------|--------------------------|---------------|

|               |         | assumptions:      | sbeiblej       |                  |                  |                   |                          |               |

|               |         | sume 'Cancelling  | -Branchos w    | ith PREDICT      | TAKEN" Accum     | o IE unit undat   | os BC and                |               |

|               | (0) //5 | sume cancelling   |                |                  | of the loop in t |                   | es re anu                |               |

|               | (0) 40  | ourse instruction |                |                  |                  |                   | branch is resolved       |               |

|               | (9) AS  | sume instruction  |                | -SPECULATIVE     |                  | IIIII AFTER UNE L | Staticit is resolved     |               |

|               | (10) T  | here are 2 MEM    |                |                  | execution)       |                   |                          |               |

|               |         | All writebacks ar |                |                  | Para pipalipad   | and take 2 co     |                          |               |

|               |         |                   |                |                  |                  | and take 2 cc     | •                        |               |

|               | (12) A  | ssume CDB has     | infinite capao | city for writeba | ICKS             |                   |                          |               |

|               | Instru  | ction             | Issue          | Execute          | Mem              | Write-Back        | Hazard                   |               |

|               |         |                   |                |                  |                  |                   |                          |               |

| loop          | LD      | F0, 0(R1)         | 1              | 2                | 34               | 56                |                          |               |

|               | MULD    | F4,F0,F2          | 2              | 714              |                  | 1516              | wait for F0              |               |

| 1st iteration | SD      | F4,0(R1)          | 3              | 4                | 1718             |                   | wait for F4              |               |

|               | SUBI    | R1,R1, #-8        | 4              | 5                |                  | 67                |                          |               |

| *             | BNE     | R1,loop           | 5              | 6                |                  |                   | R1 forwarded in 0 cc     |               |

|               | LD      | F0, 0(R1)         | 6              | 7                | 89               | 1011              | execution starts after t | anch resolved |

|               |         | F4,F0,F2          | 7              | 1219             |                  | 2021              | wait for F0              |               |

| 2nd iteration |         | F4,0(R1)          | 8              | 9                | 2223             | 201122            | wait for F4              |               |

|               | SUBI    |                   | 9              | 10               | 22.120           | 1112              |                          |               |

|               | BNE     | R1,loop           | 10             | 11               |                  |                   |                          |               |

|               | LD      | F0, 0(R1)         | 11             | 12               | 1314             | 1516              |                          |               |

|               |         | F4,F0,F2          | 12             | 1724             |                  | 2526              | wait for F0              |               |

|               | SD      | F4,0(R1)          | 13             | 14               | 2728             |                   | wait for F4              |               |

|               | SUBI    |                   | 14             | 15               |                  | 1617              |                          |               |

|               | BNE     | R1,loop           | 15             | 16               |                  |                   |                          |               |

Ch. 6, Advanced Pipelining-DYNAMIC, slide 17

© Ted Szymanski

# **Concept of 'Steady-State' Performance**

• Referring to last slide, lets examine loop iterations, to see if a 'steady-state' is reached

• Here is a definition of '**steady-state**' for a loop: The '**STATE**' of the machine remains constant, when viewed at recurring event times in each loop iteration. The state includes the number of queued instructions in the reservation stations.

• A '**recurrent event time**' is defined as the clock cycle when any event for a recurring instruction starts or ends, ie, the issue clock cycle for the same instruction in every loop, or the start of the execution for the same instruction in every loop

• The '**STATE**' of the machine includes: (a) the number of instructions queued in each type of Reservation Station.

• If a Steady-State is reached, then we can **estimate the machine performance** using this formula:

• (performance) = (Flops per iteration/clock cycles per iteration) \* (Clock Rate)

• This is an estimate, because it ignores the times to **fill-up** the pipelines at the beginning of a loop, and it ignores the time to **flush** the pipelines at the end of a loop

• For large loops, these **fill-up and flush** times become negligible and the performance estimate is quite accurate

### **Dynamic Loop Unrolling - Comments**

- Referring to last slide, lets examine loop iterations, to see if a 'steady-state' is reached

- The 1st LD starts EX in each loop iteration at times: 2, 7, 12,

- The 1st LD starts MEM in each loop iteration at times: 3, 8, 13,

- The 1st LD starts WB in each loop iteration at times: 5, 10, 15,

• Define **'Delta-T (j, j-1)**' as the difference between the starting clock cycle of 2 identical recurring events in loops (j) and (j-1)

- lets pick an recurring event = cc that the 1st LD starts EX stage in each iteration

- Observe that **Delta-T** (2, 1) = 5 cc

- Observe that **Delta-T** (3, 2) = 5 cc

- Observe that loop 3 appears to be have reached a steady state

• the ending state of the machine for iteration 3 is the same as the ending state of the machine for iteration 2, except all cc's are shifted by +5 cc: The queues in the reservation stations do not grow.

• Lets add another loop iteration to our table and see:

Ch. 6, Advanced Pipelining-DYNAMIC, slide 19

|               |        | nptions (same    | as before)      |                  |                  |                         |                                        |

|---------------|--------|------------------|-----------------|------------------|------------------|-------------------------|----------------------------------------|

|               |        | assumptions:     |                 |                  |                  |                         |                                        |

|               | (8) As | sume 'Cancellii  |                 |                  | TAKEN". Assume   |                         | es PC and                              |

|               |        |                  |                 |                  | of the loop in t |                         |                                        |

|               | (9) As | sume instruction |                 |                  |                  | ntil <u>AFTER</u> the b | branch is resolved                     |

|               |        |                  |                 | -SPECULATIVE     | ' execution)     |                         |                                        |

|               |        | here are 2 MEI   |                 |                  |                  |                         |                                        |

|               |        |                  |                 |                  | B are pipelined  | and take 2 cc           |                                        |

|               | (12) A | ssume CDB ha     | s infinite capa | city for writeba | icks             |                         |                                        |

|               | Instru | ction            | Issue           | Execute          | Mem              | Write-Back              | Hazard                                 |

|               |        |                  |                 |                  |                  |                         |                                        |

| loop          | LD     | F0, 0(R1)        | 1               | 2                | 34               | 56                      |                                        |

|               | MULD   | F4,F0,F2         | 2               | 714              |                  | 1516                    | wait for F0                            |

| 1st iteration | SD     | F4,0(R1)         | 3               | 4                | 1718             |                         | wait for F4                            |

|               | SUBI   | R1,R1, #-8       | 4               | 5                |                  | 67                      |                                        |

| *             | BNE    | R1,loop          | 5               | 6                |                  |                         | R1 forwarded in 0 cc                   |

|               | LD     | F0, 0(R1)        | 6               | 7                | 89               | 1011                    | execution starts after branch resolved |

|               |        | F4,F0,F2         | 7               | 1219             |                  | 2021                    | wait for F0                            |

| 2nd iteration |        | F4,0(R1)         | 8               | 9                | 2223             |                         | wait for F4                            |

|               |        | R1,R1, #-8       | 9               | 10               | 22.125           | 1112                    | Huicion 14                             |

|               | BNE    | R1,loop          | 10              | 11               |                  |                         |                                        |

|               | LD     | F0, 0(R1)        | 11              | 12               | 1314             | 1516                    | execution starts after branch resolved |

|               | MULD   | F4,F0,F2         | 12              | 1724             |                  | 2526                    | wait for F0                            |

|               | SD     | F4,0(R1)         | 13              | 14               | 2728             |                         | wait for F4                            |

|               | SUBI   | R1,T1, #-8       | 14              | 15               |                  | 1617                    |                                        |

|               | BNE    | R1,loop          | 15              | 16               |                  |                         |                                        |

|               | LD     | F0, 0(R1)        | 16              | 17               | 1819             | 2021                    | execution starts after branch resolved |

|               | MULD   | F4,F0,F2         | 17              | 2229             |                  | 3031                    | wait for F0                            |

|               | SD     | F4,0(R1)         | 18              | 19               | 3233             |                         | wait for F4                            |

|               | SUBI   | R1,T1, #-8       | 19              | 20               |                  | 2122                    |                                        |

|               | BNE    | R1,loop          | 20              | 21               |                  |                         |                                        |

• this loop has reached a 'steady-state'. For loop iterations  $j \ge 2$ , Delta-T = 5 clock cycles.

• the number of instructions queued in each Reservation Station will remain constant, at the same recurring event time within each loop iteration => the queue of instructions in RS does not grow or diminish, but remains constant

Ch. 6, Advanced Pipelining-DYNAMIC, slide 20

| <ul> <li>Program : A LOOP of the f</li> </ul>                                                                                                                                                                                |                                                                                                                                          |                                                                             |                                     |                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------|----------------------------|

| This example illustrates the po                                                                                                                                                                                              | wer of Tomasulo's a                                                                                                                      | gorithm, to fetch                                                           | and issue instructions.             |                            |

| and it also illustrates a long se                                                                                                                                                                                            |                                                                                                                                          |                                                                             |                                     |                            |

|                                                                                                                                                                                                                              |                                                                                                                                          |                                                                             |                                     |                            |

| Assumptions (Data)                                                                                                                                                                                                           |                                                                                                                                          |                                                                             |                                     |                            |

| <ul> <li>N = loop counter in R3,</li> </ul>                                                                                                                                                                                  |                                                                                                                                          |                                                                             |                                     |                            |

| · R1 points to the start of ver                                                                                                                                                                                              | ctor X in memory                                                                                                                         |                                                                             |                                     |                            |

| · 2 is a floating point scalar in                                                                                                                                                                                            | register F2                                                                                                                              |                                                                             |                                     |                            |

|                                                                                                                                                                                                                              |                                                                                                                                          |                                                                             |                                     |                            |

| Assumptions (Hardware):                                                                                                                                                                                                      |                                                                                                                                          |                                                                             |                                     |                            |

| <ul> <li>assume a 8 stage MULD unit,</li> </ul>                                                                                                                                                                              |                                                                                                                                          |                                                                             |                                     |                            |

| <ul> <li>assume branch-prediction, P</li> </ul>                                                                                                                                                                              |                                                                                                                                          |                                                                             |                                     |                            |

| <ul> <li>assume NON-SPECULATIVE e</li> </ul>                                                                                                                                                                                 |                                                                                                                                          |                                                                             | nust wait for branch re             | esolution before execution |

| <ul> <li>assume branches are resolved</li> </ul>                                                                                                                                                                             |                                                                                                                                          | in 1 cc                                                                     |                                     |                            |

|                                                                                                                                                                                                                              |                                                                                                                                          |                                                                             |                                     |                            |

| <ul> <li>assume a single issue maching</li> </ul>                                                                                                                                                                            |                                                                                                                                          |                                                                             |                                     |                            |

| <ul> <li>assume many FUs and deep r</li> </ul>                                                                                                                                                                               | reservation-stations,                                                                                                                    |                                                                             |                                     |                            |

| <ul> <li>assume many FUs and deep r</li> </ul>                                                                                                                                                                               | reservation-stations,                                                                                                                    |                                                                             |                                     |                            |

| <ul> <li>assume many FUs and deep r</li> <li>assume that result forwardi</li> </ul>                                                                                                                                          | reservation-stations,                                                                                                                    |                                                                             |                                     |                            |

| assume many FUs and deep r     assume that result forwardi     Observations:                                                                                                                                                 | reservation-stations,<br>ng over the CDB Writ                                                                                            |                                                                             |                                     |                            |

| <ul> <li>assume many FUs and deep r</li> <li>assume that result forwardi</li> <li>Observations:</li> <li>there are 6 instructions per</li> </ul>                                                                             | reservation-stations,<br>ng over the CDB Writ<br>loop iteration                                                                          | e-Back takes 1 cc                                                           |                                     |                            |

| <ul> <li>assume many FUs and deep r</li> <li>assume that result forwardi</li> <li>Observations:</li> <li>there are 6 instructions per</li> <li>after 6*N clock cycles, loop</li> </ul>                                       | reservation-stations,<br>ng over the CDB Writ<br>loop iteration<br>instructions must st                                                  | e-Back takes 1 cc                                                           |                                     |                            |

| <ul> <li>assume many FUs and deep n</li> <li>assume that result forwardi</li> <li>Observations:</li> <li>there are 6 instructions per</li> <li>after 6*N clock cycles, loop</li> <li>due to the Cancelling-Branch</li> </ul> | reservation-stations,<br>ng over the CDB Writ<br>loop iteration<br>instructions must st<br>-Predict-Taken scher                          | e-Back takes 1 cc<br>op issuing<br>ne, the machine ca                       | an start issuing the pro            | oper instruction in cc. 7  |

| <ul> <li>assume many FUs and deep n</li> <li>assume that result forwardi</li> <li>Observations:</li> <li>there are 6 instructions per</li> <li>after 6*N clock cycles, loop</li> <li>due to the Cancelling-Branch</li> </ul> | reservation-stations,<br>ng over the CDB Writ<br>loop iteration<br>instructions must st<br>-Predict-Taken scher                          | e-Back takes 1 cc<br>op issuing<br>ne, the machine ca                       | an start issuing the pro            | oper instruction in cc. 7  |

| <ul> <li>assume many FUs and deep r</li> <li>assume that result forwardi</li> <li>Observations:</li> <li>there are 6 instructions per</li> </ul>                                                                             | reservation-stations,<br>ng over the CDB Writ<br>loop iteration<br>instructions must st<br>-Predict-Taken scher<br>ns, and each is NOT d | e-Back takes 1 cc<br>op issuing<br>ne, the machine ca<br>ata-dependent on t | an start issuing the protious MULD; | oper instruction in cc. 7  |

| сс |                              | Instruc  | tion            | Issue      | Execute       | Mem         | Write-Bacl     | Hazard       | I                   |                |

|----|------------------------------|----------|-----------------|------------|---------------|-------------|----------------|--------------|---------------------|----------------|

| 1  | loop                         | LD       | F0, 0(R1)       | 1          | 2             | 3           | 4              |              |                     |                |

| 2  |                              | MULD     | F0,F0,F2        | 2          | 512           |             | 13             | wait for FO, | WB in cc 4          |                |

| 3  |                              | SD       | F0, 0(R1)       | 3          | 4             | 14          |                | wait for FO, | WB in cc 13         |                |

| 4  |                              | ADDI     | R1,R1, #8       | 4          | 5             |             | 6              |              |                     |                |

| 5  |                              | ADDI     | R3,R3,#-1       | 5          | 6             |             | 7              |              |                     |                |

| 6  |                              | BGEZ     | R3, loop        | 6          | 8             |             |                | wait for R3, | WB in cc 7          |                |

| 7  |                              | LD       | F0, 0(R1)       | 7          | 9             | 10          | 11             | wait for bra | nch resolution , be | fore execution |

| 8  |                              | MULD     | F0,F0,F2        | 8          | 1219          |             | 20             | wait for FO, | WB in cc 11         |                |

| 9  |                              | SD       | F0, 0(R1)       | 9          | 10            | 21          |                | wait for FO, | WB in cc 20         |                |

| 10 |                              | ADDI     | R1,R1, #8       | 10         | 11            |             | 12             |              |                     |                |

| 11 |                              | ADDI     | R3,R3,#-1       | 11         | 12            |             | 13             |              |                     |                |

| 12 |                              | BGEZ     | R3, loop        | 12         | 14            |             |                | wait for R3, | WB in cc 13         |                |

| 13 |                              | LD       | F0, 0(R1)       | 13         | 15            | 16          | 17             | wait for bra | nch resolution , be | fore execution |

| 14 |                              | MULD     | F0,F0,F2        | 14         | 1825          |             | 26             | wait for FO, | WB in cc 17         |                |

| 15 |                              | SD       | F0, 0(R1)       | 15         | 16            | 27          |                | wait for FO, | WB in cc 26         |                |

| 16 |                              | ADDI     | R1,R1, #8       | 16         | 17            |             | 18             |              |                     |                |

| 17 |                              | ADDI     | R3,R3,#-1       | 17         | 18            |             | 19             |              |                     |                |

| 18 |                              | BGEZ     | R3, loop        | 18         | 20            |             |                | wait for R3, | WB in cc 19         |                |

| 19 |                              | LD       | F0, 0(R1)       | 19         | 21            | 22          | 23             | wait for bra | nch resolution , be | fore execution |

| 20 |                              | MULTD    | F0,F0,F2        | 20         | 2431          |             | 32             | wait for FO, | WB in cc 23         |                |

| 21 |                              | SD       | F0, 0(R1)       | 21         | 22            | 33          |                | wait for FO, | WB in cc 32         |                |

| 22 |                              | ADDI     | R1,R1, #8       | 22         |               |             |                |              |                     |                |

| 23 |                              | ADDI     | R3,R3,#-1       | 23         |               |             |                |              |                     |                |

| 24 |                              | BGEZ     | R3, loop        | 24         |               |             |                |              |                     |                |

| _  |                              |          |                 |            |               |             |                |              |                     |                |

|    |                              |          |                 |            | · ·           |             |                |              | ation, in the ste   | eady st        |

| _  | Lets pick                    | one recu | urring instruc  | tion, such | as the MUL    | D, and lool | k at its execu | ution times  | 6.                  |                |

|    | • Q3: in it                  | teration | j, for j>=2, tl | ne MULTD s | starts at tir | ne 6*j cc,  | and ends 7 c   | c later      |                     |                |

|    | <ul> <li>Q4: in 1</li> </ul> | 00-th it | eration, MULT   | D starts e | execute at o  | c. 16*100   | ) =600 cc, fi  | nishes in c  | c. 600+7 cc.        |                |

| <ul> <li>Program : A LOOP of the feature</li> </ul>                                                                          | orm x[j] = x[j] ^ x[j                                            | - ]^X[]-2]^^X[ ]                                   |                        |                      |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------|------------------------|----------------------|

| This example illustrates the po                                                                                              | wer of Tomasulo's                                                | algorithm, to fetch and i                          | ssue instructions.     |                      |

| and it also illustrates a long se                                                                                            |                                                                  |                                                    |                        |                      |

|                                                                                                                              |                                                                  |                                                    |                        |                      |

| Assumptions (Data)                                                                                                           |                                                                  |                                                    |                        |                      |

| <ul> <li>N = loop counter in R3,</li> </ul>                                                                                  |                                                                  |                                                    |                        |                      |

| <ul> <li>R1 points to the start of vec</li> </ul>                                                                            | ctor X in memory                                                 |                                                    |                        |                      |

|                                                                                                                              |                                                                  |                                                    |                        |                      |

|                                                                                                                              |                                                                  |                                                    |                        |                      |

| Assumptions (Hardware):                                                                                                      |                                                                  |                                                    |                        |                      |

| <ul> <li>assume a 8 stage MULD unit,</li> </ul>                                                                              |                                                                  |                                                    |                        |                      |

| <ul> <li>assume branch-prediction, P</li> </ul>                                                                              |                                                                  |                                                    |                        |                      |

| <ul> <li>assume NON-SPECULATIVE e</li> </ul>                                                                                 |                                                                  |                                                    | wait for branch resolu | tion before executin |

| <ul> <li>assume branches are resolved</li> </ul>                                                                             |                                                                  | Il in 1 cc                                         |                        |                      |

| <ul> <li>assume a single issue maching</li> </ul>                                                                            |                                                                  |                                                    |                        |                      |

| <ul> <li>assume many FUs and deep r</li> </ul>                                                                               |                                                                  |                                                    | tural hazards          |                      |

| <ul> <li>assume that result forwarding</li> </ul>                                                                            | ng over the CDB Wr                                               | ite-Back takes 1 cc                                |                        |                      |

|                                                                                                                              |                                                                  |                                                    |                        |                      |

| Oh                                                                                                                           |                                                                  |                                                    |                        |                      |

|                                                                                                                              | In one the second term                                           |                                                    |                        |                      |

| • there are 6 instructions per                                                                                               |                                                                  | ten isovier                                        |                        |                      |

| <ul> <li>after 6*N clock cycles, loop</li> </ul>                                                                             | instructions must s                                              |                                                    | art issuing the proper | instruction in co. 7 |

| <ul> <li>there are 6 instructions per</li> <li>after 6*N clock cycles, loop</li> <li>due to the Cancelling-Branch</li> </ul> | instructions must s<br>-Predict-Taken sch                        | eme, the machine can st                            | <b>v</b> , , ,         | instruction in cc. 7 |

| <ul> <li>there are 6 instructions per</li> <li>after 6*N clock cycles, loop</li> <li>due to the Cancelling-Branch</li> </ul> | instructions must s<br>-Predict-Taken sch                        | eme, the machine can st                            | <b>v</b> , , ,         | instruction in cc. 7 |

| • there are 6 instructions per                                                                                               | instructions must s<br>-Predict-Taken sch<br>ns, and each is NOT | eme, the machine can st<br>data-dependent on the p | <b>v</b> , , ,         | instruction in cc. 7 |

| 1           | nstruc   | tion                            | Issue                | Execute                        | Mem                                       | Write-Bac                                           | Hazard                                                         |                                                                                   |                                                                                                                                                                                                                                                                                    |

|-------------|----------|---------------------------------|----------------------|--------------------------------|-------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ρL          | D        | F2, 0(R1)                       | 1                    | 2                              | 3                                         | 4                                                   |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| •           | MULD     | F0,F0,F2                        | 2                    | 512                            | -                                         | 13                                                  | wait for FO, WB in cc 4                                        |                                                                                   |                                                                                                                                                                                                                                                                                    |

| 5           | SD       | F0, 0(R1)                       | 3                    | 4                              | 14                                        |                                                     | wait for FO, WB in cc 1                                        |                                                                                   |                                                                                                                                                                                                                                                                                    |

| 1           | ADDI     | R1,R1, #8                       | 4                    | 5                              |                                           | 6                                                   |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| /           | ADDI     | R3,R3,#-1                       | 5                    | 6                              |                                           | 7                                                   |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| E           | BGEZ     | R3, loop                        | 6                    | 8                              |                                           |                                                     | wait for R3, WB in cc 7                                        |                                                                                   |                                                                                                                                                                                                                                                                                    |

| L           | D        | F2, 0(R1)                       | 7                    | 9                              | 10                                        | 11                                                  | wait for branch resolut                                        | ion, before execu                                                                 | ution                                                                                                                                                                                                                                                                              |

| N           | MULD     | F0,F0,F2                        | 8                    | 1421                           |                                           | 22                                                  | wait for FO, WB in cc 1                                        | 3                                                                                 |                                                                                                                                                                                                                                                                                    |

| 5           | SD       | F0, 0(R1)                       | 9                    | 10                             | 23                                        |                                                     | wait for FO, WB in cc 2                                        | 2                                                                                 |                                                                                                                                                                                                                                                                                    |

| 1           | ADDI     | R1,R1, #8                       | 10                   | 11                             |                                           | 12                                                  |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| 1           | ADDI     | R3,R3,#-1                       | 11                   | 12                             |                                           | 13                                                  |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| E           | 3GEZ     | R3, loop                        | 12                   | 14                             |                                           |                                                     | wait for R3, WB in cc 1                                        | 3                                                                                 |                                                                                                                                                                                                                                                                                    |

| L           | D        | F2, 0(R1)                       | 13                   | 15                             | 16                                        | 17                                                  | wait for branch resolut                                        | ion, before exect                                                                 | ution                                                                                                                                                                                                                                                                              |

| N           | MULD     | F0,F0,F2                        | 14                   | 2330                           |                                           | 31                                                  | wait for FO, WB in cc 2                                        |                                                                                   |                                                                                                                                                                                                                                                                                    |

| 5           | SD       | F0, 0(R1)                       | 15                   | 16                             | 32                                        |                                                     | wait for FO, WB in cc 3                                        | 1                                                                                 |                                                                                                                                                                                                                                                                                    |

| 1           | ADDI     | R1,R1, #8                       | 16                   | 17                             |                                           | 18                                                  |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| 1           | ADDI     | R3,R3,#-1                       | 17                   | 18                             |                                           | 19                                                  |                                                                |                                                                                   |                                                                                                                                                                                                                                                                                    |

| E           | BGEZ     | R3, loop                        | 18                   | 20                             |                                           |                                                     | wait for R3, WB in cc 1                                        | 9                                                                                 |                                                                                                                                                                                                                                                                                    |