## "Switches and Networks in VHDL -A Class Example"

Monday, Tuesday - Sept 16,17, 2013

Prof. Ted Szymanski Dept. of ECE McMaster University

4DM4 Switch-in-VHDL, 2013, Page I

(c) Prof. Ted Szymanski

## **Switches and Networks**

• Switches and Interconnection networks are used in many computing systems:

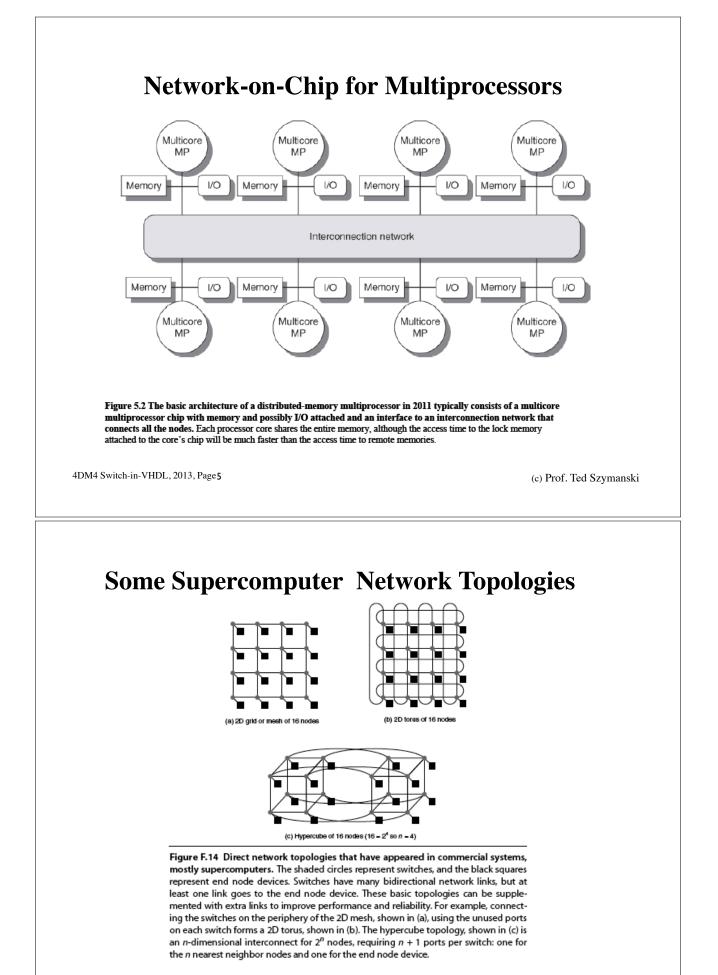

• Single-chip multiprocessors use a 'Network-on-Chip' (NoC)

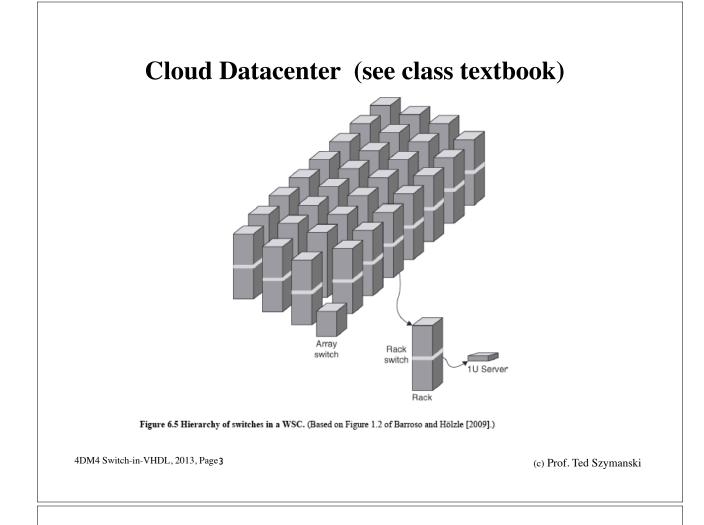

• Cloud data-centers use networks of 10Gbit Ethernet switches spanning tens to hundreds of meters

• Internet routers use basic switches with 100s of Gbit/sec bandwidth, with a control processor to run Internet protocols

• Let take a look at basic a basic switch

4DM4 Switch-in-VHDL, 2013, Page2

(c) Prof. Ted Szymanski

## Pictures: A Google DataCenter

4DM4 Switch-in-VHDL, 2013, Page4

(c) Prof. Ted Szymanski

```

Recall: 2-to-1 Multiplexer - Behavioural Entity

Entity mux21 is

Port (a, b, s: in STD LOGIC;

c : out STD LOGIC);

End entity mux21;

b 1 c

-- an architecture definition without using a process statement

Architecture mux21_arch1 of mux21 is

begin

c \le a when s = 0' else b;

end mux21 arch;

-- using a process statement to generate combinational logic

Architecture mux21 arch2 of mux21 is

begin

MUX : Process (a, b, s)

begin

VHDL rule: 'If-then-else' statement

if (s = '1') then

c \leq b;

must be in a process.

else

c <= a;

end

end process MUX;

end architecture mux21_arch2;

4DM4 Switch-in-VHDL, 2013, Page7

(c) Prof. Ted Szymanski

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

- C

use ieee.std_logic_unsigned.all;

use work.all;

entity mux21 is

generic(width : integer := 16);

port(

а

: in std_logic_vector(width-1 downto 0);

: in std_logic_vector(width-1 downto 0);

b

sel

: in std_logic;

: out std_logic_vector(width-1 downto 0)

q

);

end mux;

architecture mux21_arch1 of mux21 is

begin

q \ll a when (sel = '0') else b;

end architecture rtl;

```

(c) Prof. Ted Szymanski

4DM4 Switch-in-VHDL, 2013, Page8