### Architecture of Block-RAM-Based Massively Parallel Memory Structures:

#### **Multi-Ported Memories and Content-Addressable Memories**

by

Ameer M. S. Abdelhadi

### A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### **Doctor of Philosophy**

in

# THE FACULTY OF GRADUATE AND POSTDOCTORAL STUDIES

(Electrical and Computer Engineering)

The University of British Columbia (Vancouver)

September 2016

© Ameer M. S. Abdelhadi, 2016

### Abstract

Since they were first introduced three decades ago, Field-Programmable Gate Arrays (FPGAs) have evolved from being merely used as glue-logic to implementing entire compute accelerators. These massively parallel systems demand highly parallel memory structures to keep pace with their concurrent nature since memories are usually the bottleneck of computation performance. However, the vast majority of FPGA devices provide dual-ported SRAM blocks only. In this dissertation, we propose new ways to build area-efficient, high-performance SRAM-based parallel memory structures in FPGAs, specifically Multi-Ported Random Access Memory and Content-Addressable Memory (CAM).

While parallel computation demands more RAM ports, leading Multi-Ported Random Access Memory techniques in FPGAs have relatively large overhead in resource usage. As a result, we have produced new design techniques that are near-optimal in resource overhead and have several practical advantages. The suggested method reduces RAM usage by over 44% and improves clock speed by over 76% compared to the best of previous approaches. Furthermore, we propose a novel switched-ports technique that allows further area reduction if some RAM

ports are not simultaneously active. A memory compiler is proposed to generalize the previous approach and allow generating Multi-Switched-Ports Random Access Memory.

Content-Addressable Memories (CAMs), the hardware implementation of associative arrays, are capable of searching the entire memory space for a specific value within a single clock cycle. CAMs are massively parallel search engines accessing all memory content to compare with the searched pattern simultaneously. CAMs are used in a variety of scientific fields requiring high-speed associative searches. Despite their importance, FPGAs lack an area-efficient CAM implementation. We propose a series of scalable, area-efficient, and high-performance Binary Content-Addressable Memories (BCAMs) based on hierarchical search and data compression methods. Compared to current RAM-based BCAM architectures, our BCAMs require a maximum of 18% the RAM storage while enhancing clock speed by 45% on average, hence exhibiting a superior single-cycle search rate.

As a result, we can build faster and more cost-effective accelerators to solve some of the most important computational problems.

## Preface

The major contributions of this dissertation have also been published in journal papers and conference proceedings [1–5] as outlined below.

For all of these publications, I proposed the ideas, carried out the research, performed all of the design methodology and implementation, conducted the experiments, data generation and the analysis of the results. Furthermore, I prepared the manuscripts for these publications under the supervision of Prof. Lemieux, who also provided editorial support for all of these manuscripts and provided advice on the research design methodology.

- Multi-ported memories

- Modular Multi-Ported SRAM-based Memories [1]

Published in the 2014 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays (FPGA 2014). Parts of this publication appear in Chapter 3.

Modular Switched Multi-ported SRAM-based Memories [2]

Accepted for publication in ACM Transactions on Reconfigurable Tech-

nology and Systems (TRETS) Special Issue on Reconfigurable Components with Source Code. Parts of this publication appear in Chapter 4.

A Multi-Ported Memory Compiler Utilizing True Dual-port BRAMs

[3]

To be published in the 2016 IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM 2016). Parts of this publication appear in Chapter 4.

- Content-addressable memories

- Deep and Narrow Binary Content-Addressable Memories using FPGA-based BRAMs [4]

Published in the 2014 International Conference on Field-Programmable Technology (ICFPT 2014). Parts of this publication appear in Chapter 5.

- Modular SRAM-based Binary Content-Addressable Memories [5]

Published in the 2015 IEEE International Symposium on Field-Programmable

Custom Computing Machines (FCCM 2015). Parts of this publication

appear in Chapter 6.

- [1] A. M. S. Abdelhadi and G. G. F. Lemieux. Modular Multi-Ported SRAM-Based Memories. In ACM/SIGDA International Symposium on Fieldprogrammable Gate Arrays (FPGA), pages 35–44, February 2014

- [2] Ameer M.S. Abdelhadi and Guy G.F. Lemieux. Modular Switched Multi-Ported SRAM-Based Memories. ACM Transactions on Reconfigurable Technology and Systems (TRETS), 9(3):22:1–22:26, July 2016

- [3] A. M. S. Abdelhadi and G. G. F. Lemieux. A Multi-Ported Memory Compiler Utilizing True Dual-Port BRAMs. In *IEEE International Symposium* on Field-Programmable Custom Computing Machines (FCCM), pages 200–207, May 2016

- [4] A. M. S. Abdelhadi and G. G. F. Lemieux. Deep and Narrow Binary Content-Addressable Memories Using FPGA-Based BRAMs. In *International Conference on Field-Programmable Technology (FPT)*, pages 318–321, December 2014

- [5] A. M. S. Abdelhadi and G. G. F. Lemieux. Modular SRAM-Based Binary Content-Addressable Memories. In *IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM)*, pages 207– 214, May 2015

# **Table of Contents**

| Abstract  | t       | •••    | ••    | ••   | •   | ••  | •   | ••  | •   | •   | •    | ••   | •  | •   | •   | •   | •   | •  | •  | • | •    | • | • | • | •   | ii    |

|-----------|---------|--------|-------|------|-----|-----|-----|-----|-----|-----|------|------|----|-----|-----|-----|-----|----|----|---|------|---|---|---|-----|-------|

| Preface   |         | •••    | ••    | ••   | •   | ••  | •   | ••  | •   | •   | •    | •••  | •  | •   | •   | •   | •   | •  | •  | • | •    | • | • | • | •   | iv    |

| Table of  | Conter  | nts .  | ••    |      | •   | ••  | •   | ••  | •   | •   | •    | ••   | •  | •   | •   | •   | • • | •  | •  | • | •    | • | • | • | •   | vii   |

| List of T | ables . | •••    | ••    |      | •   | ••  | •   | ••  | •   | •   | •    | ••   | •  | •   | •   | •   | • • | •  | •  | • | •    | • | • | • | •   | xiii  |

| List of A | bbrevi  | ations | 5.    | ••   | •   | ••  | •   | ••  | •   | •   | •    |      | •  | •   | •   | •   | • • | •  | •  | • | •    | • | • | • | •   | XV    |

| List of N | otatior | ns     | ••    | ••   | •   | ••• | •   | ••  | •   | •   | •    |      | •  | •   | •   | •   | •   | •  | •  | • | •    | • | • | • | •   | XX    |

| Acknow    | ledgme  | ents . | ••    | ••   | •   | ••• | •   | ••  | •   | •   | •    | ••   | •  | •   | •   | •   | •   | •  | •  | • | •    | • | • | • | • 3 | cxiii |

| Dedicati  | on      | •••    | ••    | ••   | •   | ••• | •   | ••  | •   | •   | •    | ••   | •  | •   | •   | •   | •   | •  | •  | • | •    | • | • | • | •   | XXV   |

| 1 Intro   | ductio  | n      | ••    | ••   | •   |     | •   | ••• | •   | •   | •    |      | •  | •   | •   | •   | •   | •  | •  | • | •    | • | • | • | •   | 1     |

| 1.1       | Motiva  | tion . |       |      |     |     | •   |     | •   | •   | •    |      |    |     |     | •   | •   |    | •  |   |      | • |   |   |     | 1     |

|           | 1.1.1   | Mult   | i-Poi | rtec | l R | anc | lon | n A | 100 | ces | ss I | Me   | em | 101 | rie | s ( | M   | PF | RA | M | (Is) | ) |   |   |     | 3     |

|           | 1.1.2   | Cont   | ent-A | Add  | lre | ssa | ble | Μ   | en  | no  | rie  | es ( | C. | AI  | Ms  | 5)  | •   |    |    |   |      | • |   |   |     | 4     |

|   | 1.2  | Thesis Statement and Research Goals6 |                                                                    |      |  |  |  |  |  |

|---|------|--------------------------------------|--------------------------------------------------------------------|------|--|--|--|--|--|

|   | 1.3  | Resear                               | Research Problem: On the feasibility of Parallel memory structures |      |  |  |  |  |  |

|   |      | in FPGAs                             |                                                                    |      |  |  |  |  |  |

|   |      | 1.3.1                                | Multi-Ported Random Access Memories (MPRAMs)                       | 7    |  |  |  |  |  |

|   |      | 1.3.2                                | Content-Addressable Memories (CAMs)                                | 8    |  |  |  |  |  |

|   | 1.4  | Resear                               | rch Contributions                                                  | 10   |  |  |  |  |  |

|   |      | 1.4.1                                | Invalidation-Based Live-Value Table (I-LVT)                        | 10   |  |  |  |  |  |

|   |      | 1.4.2                                | Switched Ports                                                     | 11   |  |  |  |  |  |

|   |      | 1.4.3                                | 2-Dimensional Hierarchical Search BCAM (2D-HS-BCAM)                | 12   |  |  |  |  |  |

|   |      | 1.4.4                                | Indirectly Indexed Hierarchical Search BCAM (II-HS-BCAM)           | ) 13 |  |  |  |  |  |

|   | 1.5  | Resear                               | rch Methodology and Evaluation Metrics                             | 13   |  |  |  |  |  |

|   |      | 1.5.1                                | Verilog Description                                                | 13   |  |  |  |  |  |

|   |      | 1.5.2                                | Simulation and Synthesis                                           | 14   |  |  |  |  |  |

|   |      | 1.5.3                                | Results Collection                                                 | 15   |  |  |  |  |  |

|   |      | 1.5.4                                | BRAM Packing Approximation                                         | 15   |  |  |  |  |  |

|   | 1.6  | Disser                               | tation Organization                                                | 16   |  |  |  |  |  |

| 2 | Bacl | karoun                               | d and Related Work                                                 | 18   |  |  |  |  |  |

| 4 |      |                                      |                                                                    |      |  |  |  |  |  |

|   | 2.1  | RAM                                  | Multi-Porting Techniques in Embedded Systems                       | 18   |  |  |  |  |  |

|   |      | 2.1.1                                | Register-based RAM                                                 | 19   |  |  |  |  |  |

|   |      | 2.1.2                                | RAM Multi-Pumping                                                  | 19   |  |  |  |  |  |

|   |      | 2.1.3                                | Multi-Read RAM: Bank Replication                                   | 21   |  |  |  |  |  |

|   |      | 2.1.4                                | Multi-Write RAM: Emulation via Multi-banking                       | 21   |  |  |  |  |  |

|   | 2.2  | Multi-j  | ported SRAM-based Memories: Prior Work                 | 23 |

|---|------|----------|--------------------------------------------------------|----|

|   |      | 2.2.1    | LVT-Based Multi-ported RAM                             | 23 |

|   |      | 2.2.2    | Multi-Ported Random Access Memories with True Dual-    |    |

|   |      |          | Ports                                                  | 25 |

|   |      | 2.2.3    | XOR-Based Multi-Ported RAM                             | 26 |

|   | 2.3  | FPGA     | Based Binary Content-Addressable Memories (BCAMs) .    | 29 |

|   |      | 2.3.1    | Register-Based BCAMs                                   | 31 |

|   |      | 2.3.2    | Brute-Force Approach via Transposed Indicators RAM     |    |

|   |      |          | (TIRAM)                                                | 32 |

|   |      | 2.3.3    | BCAM Pattern Width Cascading and Scaling               | 35 |

|   |      | 2.3.4    | Reconfiguration Memory Based Content-Addressable Mem-  |    |

|   |      |          | ories (RCAMs)                                          | 37 |

|   |      | 2.3.5    | Algorithmic Heuristics                                 | 39 |

|   |      | 2.3.6    | Vendor Support for BCAMs                               | 40 |

| 3 | Mul  | ti-Porte | d Random Access Memories via Invalidation-Based Live-  |    |

|   | Valu | e Table  | (I-LVT)                                                | 42 |

|   | 3.1  | Introdu  | iction                                                 | 43 |

|   | 3.2  | Invalid  | ation Table                                            | 44 |

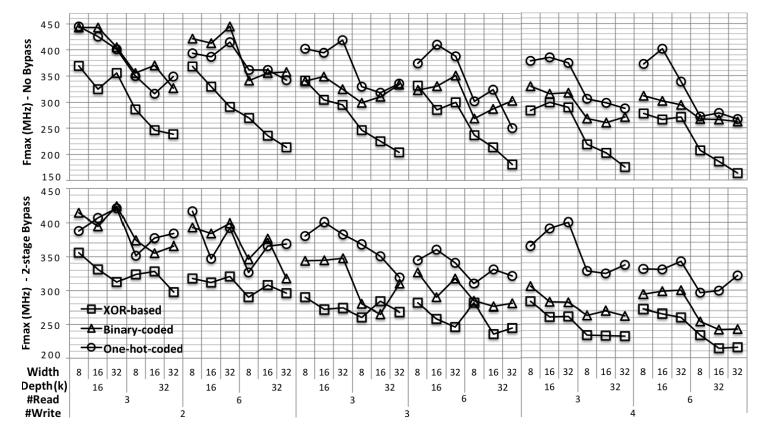

|   |      | 3.2.1    | Bank ID Embedding: Binary-Coded Bank IDs and Selectors | 46 |

|   |      | 3.2.2    | Mutually-Exclusive Conditions: Thermometer-Coded Bank  |    |

|   |      |          | IDs with One-hot-Coded Selectors                       | 52 |

|   |      | 3.2.3    | Data Dependencies and Bypassing                        | 55 |

|   |     | 3.2.4    | Initializi | ng Multi-Ported RAM Content              | 58  |

|---|-----|----------|------------|------------------------------------------|-----|

|   |     | 3.2.5    | Compari    | son and Discussion                       | 60  |

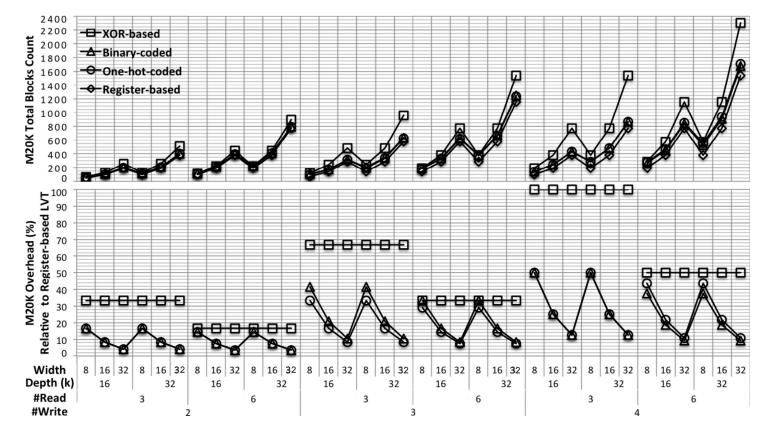

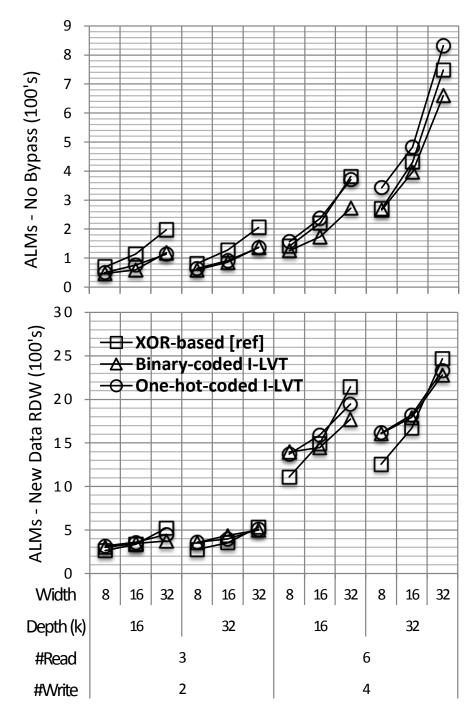

|   |     |          | 3.2.5.1    | SRAM Usage based on RAM Architecture     | 60  |

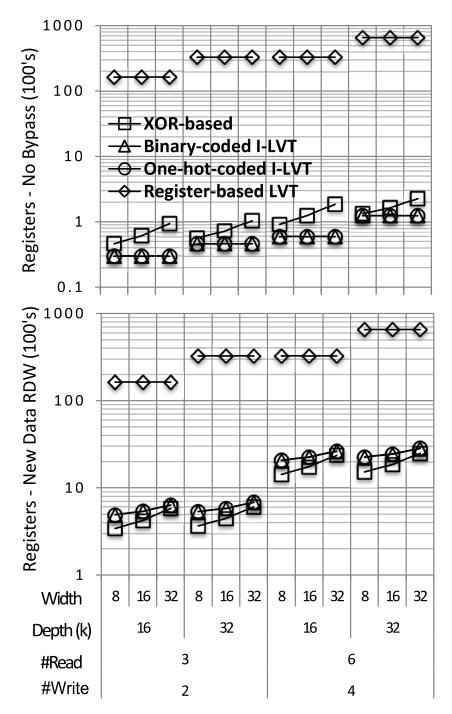

|   |     |          | 3.2.5.2    | Register Usage based on RAM Architecture | 62  |

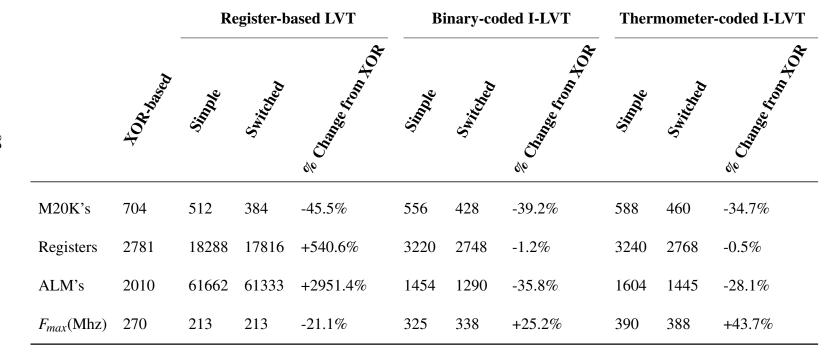

|   | 3.3 | Experi   | imental Re | esults                                   | 68  |

|   | 3.4 | Conclu   | usions     |                                          | 75  |

| 4 | Mul | ti-Porte | ed Rando   | m Access Memories with Switched Ports    | 77  |

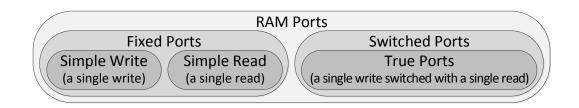

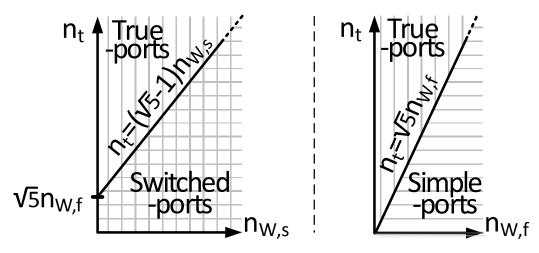

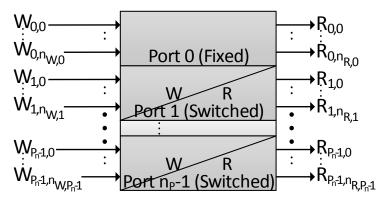

|   | 4.1 | RAM      | Port Class | ification                                | 79  |

|   | 4.2 | Multi-   | Ported Me  | emories with Single Switched-Port        | 81  |

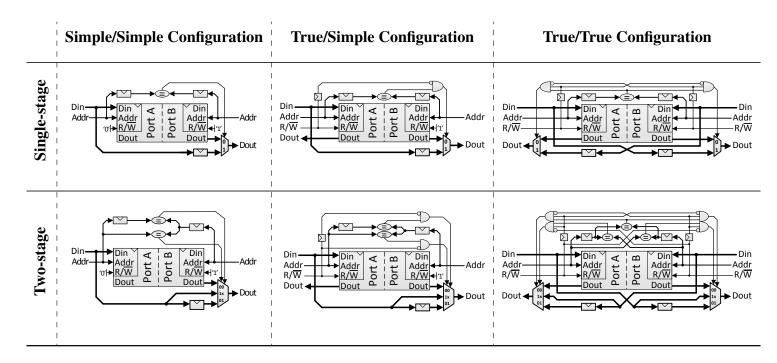

|   |     | 4.2.1    | Single S   | witched-Port Support                     | 83  |

|   |     |          | 4.2.1.1    | Data Dependencies and Bypassing          | 88  |

|   |     |          | 4.2.1.2    | SRAM Usage based on Port Functionality   | 90  |

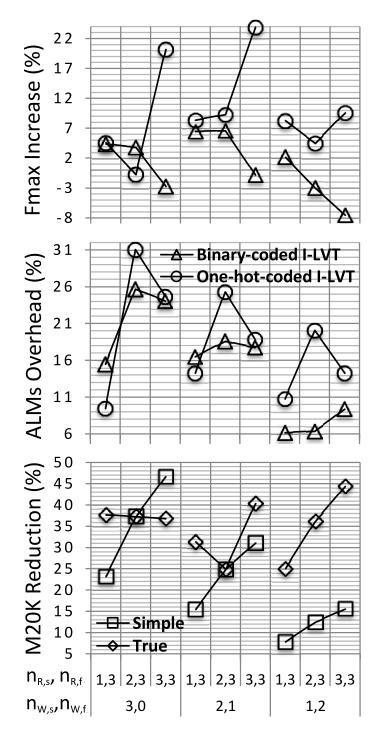

|   |     | 4.2.2    | Experim    | ental Results                            | 94  |

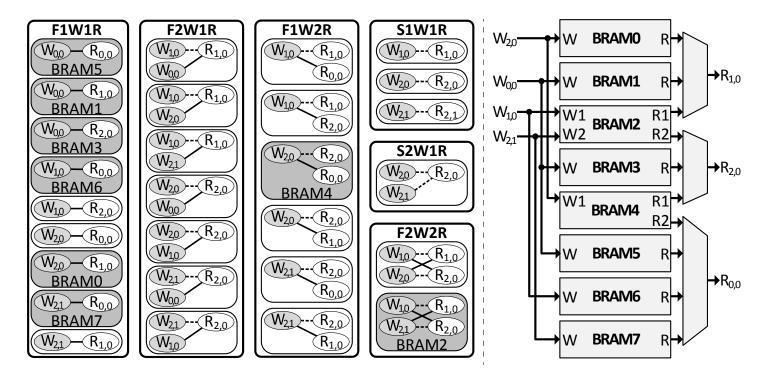

|   | 4.3 | Multi-   | Switched-  | Ports                                    | 96  |

|   |     | 4.3.1    | Multi-Po   | orted RAM with Multiple Switched Ports   | 97  |

|   |     |          | 4.3.1.1    | Motivation and Key Idea                  | 97  |

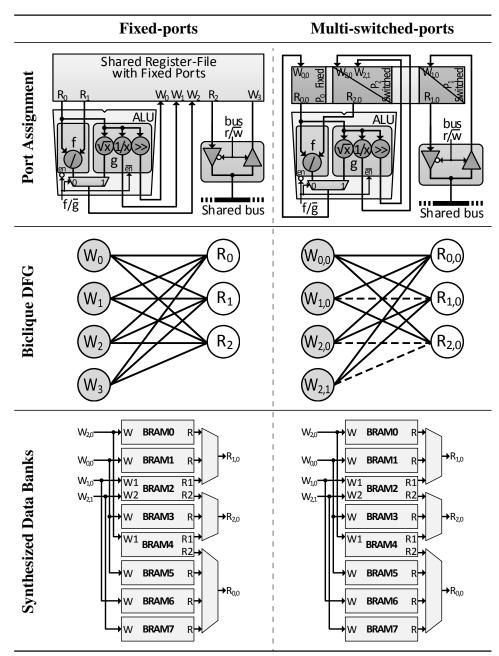

|   |     |          | 4.3.1.2    | Port Assignment and Problem Definition   | 100 |

|   |     |          | 4.3.1.3    | Modeling Data Banks with Data Flow Graph |     |

|   |     |          |            | (DFG)                                    | 102 |

|   |     |          | 4.3.1.4    | Multi-Switched-Ports DFG Optimization    | 104 |

|   |     |          | 4.3.1.5    | Solving the Cover Problem                | 106 |

|   |     |          | 4.3.1.6    | Data Dependencies and Bypassing          | 109 |

|   |     |          |            |                                          |     |

|   |              | 4.3.2    | Experime           | ental Results                              |

|---|--------------|----------|--------------------|--------------------------------------------|

|   |              |          | 4.3.2.1            | Experimental Framework                     |

|   |              |          | 4.3.2.2            | Methodology                                |

|   |              |          | 4.3.2.3            | Test Cases                                 |

|   |              |          | 4.3.2.4            | Results                                    |

|   | 4.4          | Conclu   | usions             |                                            |

| 5 | <b>2-D</b> i | mensio   | nal Hiera          | rchical Search BCAMs (2D-HS-BCAMs) 124     |

|   | 5.1          | Introd   | uction             |                                            |

|   | 5.2          | The 2-   | Dimensio           | nal Hierarchical Search BCAM (2D-HS-BCAM)  |

|   |              | Appro    | ach                |                                            |

|   | 5.3          | BCAM     | 1 Bypassir         | ng                                         |

|   | 5.4          | Compa    | arison and         | Discussion                                 |

|   | 5.5          | Experi   | mental Re          | sults                                      |

|   | 5.6          | Conclu   | usions             |                                            |

| 6 | Indi         | rectly I | ndexed H           | ierarchical Search BCAMs (II-HS-BCAMs) 145 |

|   | 6.1          | Introd   | uction             |                                            |

|   | 6.2          | Motiva   | ation and <b>F</b> | Key Idea                                   |

|   | 6.3          | Design   | 1 and Func         | tionality                                  |

|   | 6.4          | Feasib   | ility on Al        | tera's Stratix Devices                     |

|   | 6.5          | Compa    | arison and         | Discussion                                 |

|   | 6.6          | Experi   | mental Re          | sults                                      |

|   | 6.7          | Conclu   | usions             |                                            |

| 7  | Con          | clusion              | s                                                   |  |  |  |

|----|--------------|----------------------|-----------------------------------------------------|--|--|--|

|    | 7.1          | Dissertation Summary |                                                     |  |  |  |

|    | 7.2          | Future               | Directions                                          |  |  |  |

|    |              | 7.2.1                | Invalidation-Table Multi-Ported Memories            |  |  |  |

|    |              | 7.2.2                | BRAM-Based Content-Addressable Memories 169         |  |  |  |

|    |              | 7.2.3                | Parallel Reconfigurable Computing with Customizable |  |  |  |

|    |              |                      | Concurrent Memories                                 |  |  |  |

| Bi | Bibliography |                      |                                                     |  |  |  |

| A  | Bru          | te-Forc              | e Transposed Indicators (BF-TI) BCAM Writing Mech-  |  |  |  |

|    | anis         | m                    |                                                     |  |  |  |

| B  | Wid          | e Prior              | ity Encoders in FPGAs                               |  |  |  |

| С  | Veri         | log IPs              | User Guide                                          |  |  |  |

# **List of Tables**

| Table 3.1 | Bypassing for XOR-based and binary/thermometer-coded I-             |

|-----------|---------------------------------------------------------------------|

|           | LVT multi-ported memories                                           |

| Table 3.2 | Summary of SRAM bits usage                                          |

| Table 3.3 | Summary of M20K blocks usage                                        |

| Table 3.4 | Summary of register usage                                           |

| Table 4.1 | Single-stage and two-stage bypassing for simple and true dual-      |

|           | port RAM                                                            |

| Table 4.2 | Resources consumption for a 4W/8R multi-ported RAM test-            |

|           | case with 8k-entries of 32-bit words and new data RDW bypassing. 92 |

| Table 4.3 | Register consumption for a 4W/8R multi-ported RAM test-case         |

|           | with 8k-entries of 32-bit words                                     |

| Table 4.4 | Biclique patterns and their attributes                              |

| Table 4.5 | Comparison of purely fixed-ports versus multi-switched-ports        |

|           | implementations of the example in Figure 4.8                        |

| Table 4.6 | Bypassing of multi-switched-ports                                   |

| Table 4.7  | Single-stage and two-stage BRAM bypassing                     |

|------------|---------------------------------------------------------------|

| Table 4.8  | Multi-switched-ports conversion (example from Figure 4.8) 117 |

| Table 4.9  | Heterogeneous multi-ported RAM testcases                      |

| Table 4.10 | Experimental results                                          |

| Table 4.11 | Results comparison                                            |

| Table 6.1  | BRAM usage of a single stage II2D-BCAM 154                    |

| Table 6.2  | Storage efficiency $\mu_s$ (inversed)                         |

|            |                                                               |

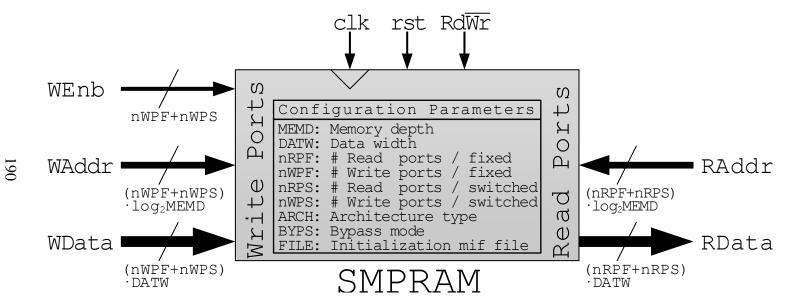

| Table C.1  | List of SMPRAM module interface ports                         |

| Table C.2  | List of SMPRAM module parameters                              |

# **List of Abbreviations**

| The following lists an aboreviations that have been used in the disserta |                                           |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| MSPRAM                                                                   | Multi-Switched-Ports Random Access Memory |  |  |  |

| MPRAM                                                                    | Multi-Ported Random Access Memory         |  |  |  |

| LVT                                                                      | Live-Value Table                          |  |  |  |

| I-LVT                                                                    | Invalidation-Based Live-Value Table       |  |  |  |

| ALM                                                                      | Adaptive Logic Module                     |  |  |  |

| ESB                                                                      | Embedded System Block                     |  |  |  |

| MFB                                                                      | Multi-Function Block                      |  |  |  |

| ALU                                                                      | Arithmetic Logic Unit                     |  |  |  |

| API                                                                      | Application Programming Interface         |  |  |  |

| ASIC                                                                     | Application-Specific Integrated Circuit   |  |  |  |

| BRAM                                                                     | Block-RAM                                 |  |  |  |

The following lists all abbreviations that have been used in the dissertation.

- CAD Computer-Aided Design

- CAM Content-Addressable Memory

- **BCAM** Binary Content-Addressable Memory

- **TCAM** Ternary Content-Addressable Memory

- **RCAM** Reconfiguration Memory Based Content-Addressable Memory

- PE Priority Encoder

- PE Processing Element

- LPME Longest-Prefix Match Encoder

- LPM Longest-Prefix Match

- CGRA Coarse-Grained Reconfigurable Array

- CMOS Complementary Metal-Oxide Semiconductor

- CPU Central Processing Unit

- **DFG** Data Flow Graph

- **DSP** Digital Signal Processing

- FF Flip-Flop

- **FPGA** Field-Programmable Gate Array

- GUI Graphical User Interface

IC **Integrated Circuit** LP Linear Programming ILP Integer Linear Programming IP Intellectual Property IP Internet Protocol IPv4 Internet Protocol Version 4 IPv6 Internet Protocol Version 6 LAB Logic Array Block MLAB Memory Logic Array Block Look-Up Table LUT MSB Most Significant Bit Least Significant Bit LSB RAM Random Access Memory ROM Read Only Memory RTL Register Transfer Level **SRAM** Static RAM VLIW Very Large Instruction Word

- LZD Leading Zero Detector

- LZC Leading Zero Counter

- WAW Write-After-Write

- **RAW** Read-After-Write

- **RDW** Read-During-Write

- TLB Translation Lookaside Buffer

- TIRAM Transposed Indicators RAM

- **STIRAM** Set Transposed Indicators RAM

- **BF-TI** Brute-Force Transposed Indicators

- 2D-HS-BCAM 2-Dimensional Hierarchical Search BCAM

- II-HS-BCAM Indirectly Indexed Hierarchical Search BCAM

- **BST** Binary Search Tree

- BGP Border Gateway Protocol

- MSPS Million Searches per Second

- CMOS Complementary Metal-Oxide-Semiconductor

- NMOS N-Type MetalOxideSemiconductor

- ACM Association for Computing Machinery

- **SIGDA** Special Interest Group on Design Automation

- **IEEE** The Institute of Electrical and Electronics Engineers

- **TRETS** Transactions on Reconfigurable Technology and Systems

- FCCM Field-Programmable Custom Computing Machines

- **ICFPT** International Conference on Field-Programmable Technology

- **NSERC** Natural Sciences and Engineering Research Council of Canada

# **List of Notations**

The following lists all notations that have been used in the dissertation.

| WAddr    | Write Address                     |

|----------|-----------------------------------|

| RAddr    | Read Address                      |

| WData    | Write Data Bus                    |

| RData    | Read Data Bus                     |

| RWData   | Bidirectional Read/Write Data Bus |

| RBankSel | Read Bank Selector                |

| WPatt    | Write Pattern                     |

| WAddr    | Write Address                     |

| MPatt    | Match Pattern                     |

| MAddr    | Match Address                     |

| MIndc    | Match Indicators                  |

- MultiPatt Multiple Patterns

- **RefRAM** Reference RAM

- SetRAM Sets RAM

- *n<sub>W</sub>* Number of Write Ports

- *n<sub>R</sub>* Number of Read Ports

- *n*<sub>t</sub> Number of True Ports

- $n_{W,f}$  Number of Write Simple (Fixed) Ports

- $n_{R,f}$  Number of Read Simple (Fixed) Ports

- $n_{W,s}$  Number of Write Switched Ports

- $n_{R,s}$  Number of Read Switched Ports

- *d* Memory Depth

- w Data Width

- *n*<sub>*M20K*</sub> Number of M20K Blocks

- *n<sub>BReg</sub>* Number of Bypass Registers

- *f<sub>fb</sub>* I-LVT Feedback Function

- *fout* I-LVT Output Extraction Function

| Р              | Ports Group                    |

|----------------|--------------------------------|

| W              | Writes Group                   |

| R              | Reads Group                    |

| $E_s$          | Switched Edges Set             |

| $R_D$          | RAM Depth                      |

| $C_D$          | CAM Depth                      |

| $D_W$          | Data Width                     |

| $P_W$          | Pattern Width                  |

| $S_W$          | Set Width                      |

| $P_{W,opt}$    | Optimal Cascaded Pattern Width |

| $I_{p,a}$      | Match Indicator                |

| Α              | Address Set                    |

| S              | Set Set                        |

| $R_{W,max}$    | Widest RAM Width               |

| $R_{D,min}$    | Shallowest RAM Depth           |

| n <sub>C</sub> | Number of Cascades             |

### Acknowledgments

My gratitude begins with my research advisor Dr. Guy Lemieux, who have offered consistent support, guidance, dedication and patience throughout my research study and bringing this dissertation to fruition. Without his invaluable assistance, encouragement, advice, and technical insight, this work would not have been possible. I am very grateful for having him as my mentor and research advisor!

In addition, I would like to thank Dr. Mark Greenstreet, with whom I have worked on several exciting and productive project. His brilliance and expertise were a real inspiration. I am also thankful to Dr. Steve Wilton for the several discussions we had on academia, research and teaching. His deep knowledge, insights, support, and encouragement were invaluable.

I would also like to thank my external examiner, Dr. Paul Chow from the University of Toronto, for providing valuable comments that helped improve the quality of this dissertation and for being kind enough to travel and attend this dissertation defence in person. I thank my university examiners, Dr. Alexandra Fedorova and Dr. Jeremy Heyl and my supervisory committee Dr. Mieszko Lis and Dr. Mieszko Lis for their constructive feedback and suggestions during this dissertation defence.

I thank the System-on-Chip technical support staff, Roozbeh Mehrabadi and Dr. Roberto Rosales, for their help and dedication. I thank all my colleagues in the System-on-Chip research group, and other friends whom I have had the pleasure of working with. In particular, Rehan Ahmed, Usman Ahmed, Abdalrahman Arafeh, Samer Al-Kiswany, Mohammed Al-Taha, Alex Brant, Anas Bsoul, Assem Bsoul, Joydip Das, Stuart Dueck, Joseph Edwards, Abdullah Gharaibeh, Jeffrey Goeders, David Grant, Eddie Hung, Keith Lee, Zhiduo Liu, Hossein Omidian, Aaron Severance, Ahmad Sharkia, Douglas Sim, Tom Tang, Michael Yue, Chris Wang, and others.

Financial support from the Natural Sciences and Engineering Research Council of Canada (NSERC) is gratefully acknowledged. Thanks to Altera Corp. and CMC Microsystems for donating hardware and software licenses.

Last but most important, thanks and love goes to my family –my parents, Mohammad and Rasmia, my wife, Soaad, and our son, Mohammad– I am grateful for your unwavering love, gracious support and continuous encouragement. Thank you Soaad for being there for me again and again when I needed you the most. I would never have gotten to this point without you. Thank you for reminding me of my ability to accomplish this goal. I love you! To my parents, Mohammad and Rasmia,

my wife, Soaad,

and our son, Mohammad.

## **Chapter 1**

# Introduction

The following introductory chapter is organized as follows. The need for Block-RAM-based massively parallel memory structures and the motivation behind our work is described in detail in Section 1.1. The thesis statement and research goals are provided in Section 1.2. Section 1.3 explains the feasibility problem of parallel memory structures in Field-Programmable Gate Arrays (FPGAs). Our research contributions are listed in Section 1.4. Section 1.5 describes the research methodology and evaluation metrics used to evaluate and compare our design to other techniques. The organization of the rest of this dissertation is summarized in Section 1.6

### **1.1 Motivation**

Since they were first introduced three decades ago, Field-Programmable Gate Arrays (FPGAs) have evolved from being merely used as glue-logic to competing with custom-designed Application-Specific Integrated Circuits (ASICs). Modern FPGAs comprise hundreds of thousands of programmable logic gates augmented with thousands of configurable Digital Signal Processing (DSP) blocks and memory blocks, all on the same chip with flexible routing fabric. Routing and configuration flexibility of these numerous hardware blocks grants FPGAs their inherent parallelism; hence, FPGAs are exploited for massively parallel computing and can be tailored as an accelerator for specific applications.

These massively parallel systems demand highly parallel memory structures to keep pace with their concurrent nature since memories are usually the bottleneck of computation performance. In this dissertation, we propose new ways to build two key types of parallel memory structures in FPGAs, specifically Multi-Ported Random Access Memories (MPRAMs) and Content-Addressable Memories (CAMs), using the regular logic, registers and dual-ported memory blocks found in modern FPGAs.

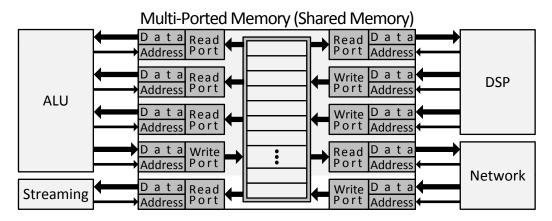

FPGA devices provide SRAM blocks with only one or two access ports. This allows RAM content in one block to be accessed concurrently by one or two "users" at the same time. To allow more concurrent access, a method is required to allow potentially dozens of users to simultaneously read or write an SRAM in the same clock cycle as depicted in Figure 1.1.

In addition, modern FPGAs do not provide hard CAM blocks. Instead, they must be built from existing SRAM blocks; existing construction techniques do not scale well, making large CAMs very inefficient.

Below, we elaborate further on MPRAMs and CAMs.

Figure 1.1: Multi-Ported Random Access Memory (MPRAM) abstraction as shared memory allowing concurrent access for several users.

#### **1.1.1 Multi-Ported Random Access Memories (MPRAMs)**

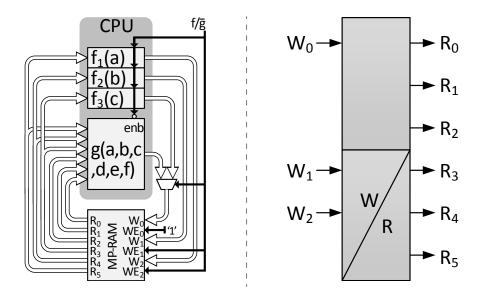

Multi-ported memories are the cornerstone of all high-performance Central Processing Unit (CPU) designs. They are often used in register files, but also in other shared-memory structures such as Translation Lookaside Buffers (TLBs), caches and coherence tags. Hence, high-bandwidth memories with multiple parallel reading and writing ports are required. In particular, multi-ported RAMs are often used by wide superscalar processors [6], Very Large Instruction Word (VLIW) processors [6, 7], multi-core processors [8, 9], vector processors, Coarse-Grained Reconfigurable Arrays (CGRAs) [10], and Digital Signal Processors (DSPs). For example, the second generation of the Itanium processor architecture employs a 20-port register file constructed from SRAM bit cells with 12 read ports and 8 write ports [8]. The key requirement for all of these designs is fast, concurrent, single-cycle access from multiple requesters. These multiple requesters require concurrent access for performance reasons. While there is demand for more RAM ports, the two leading multi-ported RAM techniques in FPGAs have relatively large overhead in (1) register usage or (2) total SRAM block count [11, 12]. This dissertation introduces two new design techniques that are near-optimal in resource overhead and have several practical advantages. Furthermore, it provides a mechanism to construct and optimize memory structures with time-switched ports. A RAM compiler has also been developed to automate the construction of these switched memories.

#### **1.1.2** Content-Addressable Memories (CAMs)

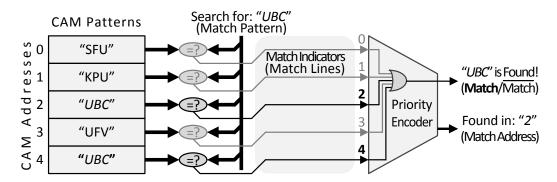

CAMs, being a hardware implementation of associative arrays, are massively parallel search engines accessing all memory content to compare with the searched pattern simultaneously. An abstraction of a CAM is shown in Figure 1.2 where CAM patterns are stored in a memory. To find a specific pattern in the CAM, all CAM patterns are read simultaneously, then compared to the matched pattern. Comparing all CAM patterns to the matched pattern generates match indicators (or match lines) which indicated for each pattern in the CAM if this pattern matches the searched pattern. A priority-encoder will detect if there is a match and generate the address of the first matching pattern.

CAMs are considered heavy power consumers due to the very wide memory bandwidth requirement and the concurrent compare. While a standard RAM returns data located in a given memory address, a CAM returns an address containing a specific given datum, thus performing a memory-wide search for a specific value. To do this, it must perform a memory-wide search for a specific value, and there

**Figure 1.2:** Content-Addressable Memory (CAM) abstraction as a massively parallel search engine accessing all memory content to compare with the searched pattern simultaneously.

may be multiple addresses that all match the data.

Since a CAM is actually a high-performance implementation of a very basic associative search, it can be used in many science fields [13]. CAMs are keystones of network processors [14–17], specifically used for Internet Protocol (IP) lookup engines for packet forwarding [18–24], intrusion detection [25–29], packet filtering and classification [30–32]. In high-performance processors, CAMs are used for memory management as coherence tag arrays for highly-associative caches [33] and Translation Lookaside Buffers (TLBs) [34, 35]. CAMs are also used to implement load and store queues in out-of-order instruction schedulers with a wide scheduling window [36]. In addition, CAMs are used for pattern matching [37–39], data compression [40], DSP [41, 42], databases [43, 44], bioinformatics [45, 46], and logic minimization [47]. A variety of other scientific fields also use CAMs as single-cycle associative search accelerators with millions of search entries.

Despite their importance, the high implementation cost of CAMs means they are used sparingly. As a result, FPGA vendors do not provide any dedicated CAM circuitry or any special infrastructure to enable a construction of efficient CAMs. Furthermore, FPGAs lack an area-efficient soft CAM implementation. Current CAM approaches in vendor IP libraries achieve a maximum of 64K entries and utilize all the resources of a modern FPGA device. Instead, designers tend to use algorithmic search heuristics causing a dramatic performance degradation.

### **1.2 Thesis Statement and Research Goals**

This dissertation addresses the memory bottleneck of massively parallel reconfigurable systems by providing efficient, parallel and customizable embedded memory structures. Although MPRAMs and CAMs are important, their high implementation cost means they are used sparingly. As a result, FPGA vendors only provide standard dual-ported memories to handle the majority of usage patterns, and rely upon a simplistic soft CAM implementation that does not scale. This dissertation describes a novel, efficient and modular approach to construct MPRAMs and CAMs out of basic dual-ported RAM blocks, logic and registers.

The main goal is to address scaling issues with both designs, to permit use of deeper MPRAMs with more ports, as well as deeper and wider CAMs that can scale better. These new designs must be practical as well, meaning they achieve high clock rates and provide complete functionality such as initialization, bypassing, and fast updates.

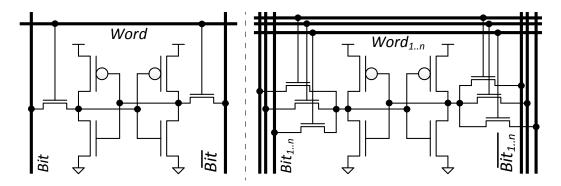

**Figure 1.3:** (left) A single-port SRAM cell using two cross-coupled CMOS inverters. (right) Multi-ported access using additional pass-gates, word and bit lines.

### **1.3 Research Problem: On the feasibility of Parallel memory structures in FPGAs**

In this section, we describe the limitations of creating area-efficient and performanceoriented parallel memory structures in FPGAs, specifically multi-ported memories and content-addressable memories.

#### **1.3.1** Multi-Ported Random Access Memories (MPRAMs)

A Static RAM (SRAM) cell is a Complementary Metal-Oxide-Semiconductor (CMOS) bi-stable circuit built out of CMOS cross-coupled inverters and access pass-gates as illustrated in Figure 1.3 (left). To provide more access ports, the basic basic SRAM bit cell can be altered to provide more bit lines, word lines, and access transistors as described in Figure 1.3 (right), however, the area growth is quadratic with the number of ports [48]. Furthermore, this requires a custom design for each unique set of parameters (e.g., number of ports, width and depth of RAM).

Since FPGAs must fix their RAM block design for generic, most common usage cases, it is too costly to provide highly specialized RAMs with a large number of ports. In FPGAs, one way of synthesizing a multi-ported RAM is to build it from registers and logic. However, this is only feasible for very small memories. Other techniques, covered in Chapter 2, are inefficient and do not scale well for deep or wide MPRAMs. Hence, a method of composing arbitrary, multi-ported RAMs from simpler RAM blocks is required.

#### **1.3.2** Content-Addressable Memories (CAMs)

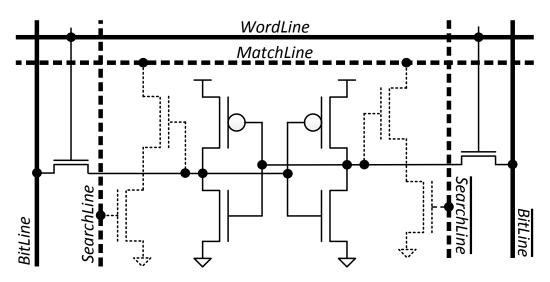

CAMs are usually custom-designed at the transistor level [49–53]. As depicted in Figure 1.4, four additional transistors over the standard 6-transistor SRAM cell are required. The additional transistors form a comparison circuit, an XOR with NMOS-stack only, since its output (the match line) is pulled-up. Other variations of the BCAM cells are also available, e.g., the 9-T NAND-type BCAM cell [49]. However, the custom approach requires more engineering effort and longer delays in time-to-market. This custom approach is unsuitable for FPGAs.

Older FPGA devices, including Altera's FLEX, Mercury and APEX devices [54] employed minor architectural features to directly construct small CAM blocks. However, FPGA vendors do not provide dedicated hard cores for CAMs in modern devices. These have been replaced with soft CAM cores that employ existing Block-RAMs in a brute-force approach described in this dissertation as the traditional or transposed-indicators RAM approach.

While modern databases can easily contain millions of entries, the area growth

Figure 1.4: CMOS 10-T NOR-type BCAM cell; solid lines form a 6-T SRAM cell.

of traditional CAM techniques in FPGAs is high and is currently limited to 64k entries. Wide and shallow RAMs are needed to efficiently implement brute-force CAMs. Shallow RAMs are required because each extra bit in the CAM pattern width doubles the required RAM depth, resulting in poor efficiency. In addition, deeper CAMs can be built by increasing RAM width. However, FPGA RAM block width is growing slowly. For example, M4K blocks in Stratix II devices have minimal depth of 128 with maximal width of 36, M9K blocks in Stratix III and Stratix IV devices have minimal depth of 256 and maximal width of 36, M20K blocks in Stratix V devices [55] have minimal depth of 512 and maximal width of 40. With the increasing depth of RAMs, and limited width growth, the brute-force approach is getting less efficient.

#### **1.4 Research Contributions**

This section lists the contributions of my dissertation. The multi-ported memory contributions can be categorized into the Invalidation-Based Live-Value Table (I-LVT) work in Chapter 3 and the switched ports work in Chapter 4. Whereas our preliminary work on BCAMs is the 2-Dimensional Hierarchical Search BCAM (2D-HS-BCAM) work in Chapter 5 and the follow-up work is the Indirectly Indexed Hierarchical Search BCAM (II-HS-BCAM) in Chapter 6.

#### **1.4.1** Invalidation-Based Live-Value Table (I-LVT)

Recently, a few FPGA-based multi-ported RAM designs have been proposed. They use a Live-Value Table (LVT) together with multi-banking for data storage [11]. While each writing port writes to a different bank, the LVT tracks the last-written bank for each memory address, allowing reading of the latest data. Since the LVT is composed of registers, it cannot build deep MPRAMs efficiently. Alternatively, the XOR-based method retrieves the latest written data by utilizing cancellation properties of the XOR operator[12]. The XOR-based method overcomes the register-based memory limitation by storing all data in BRAMs; however, this incurs excessive memory overhead since wide memories are required to accommodate all the XOR-ed data.

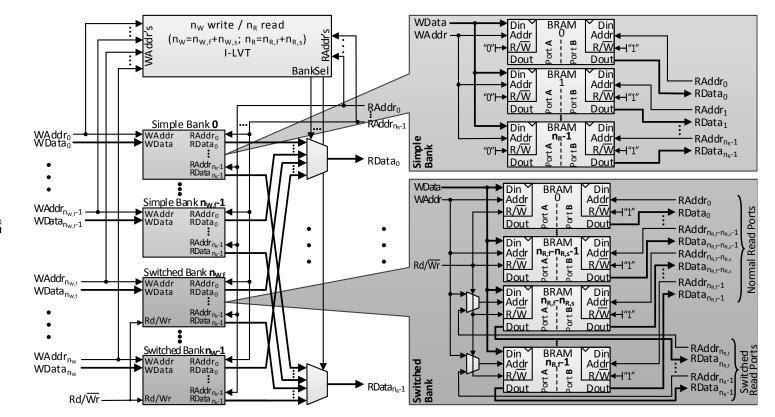

In Chapter 3, an SRAM-based LVT is proposed by utilizing an invalidationtable data structure [1]. Similar to a regular LVT, the Invalidation-Based Live-Value Table (I-LVT) determines the correct bank to read from, but it differs in how updates to the table are made. While previous approaches use registers to implement a live-value-table, the breakthrough of this approach is that it is near-optimal and purely SRAM-based, allowing it to efficiently scale to large depths. Compared to other multi-ported approaches, the I-LVT also provides improved overall performance. This dissertation demonstrates the viability, area reduction, and performance benefits of the proposed approach and provide an open source library with a fully tested, generic and modular implementation that can be adopted in parallel computing systems.

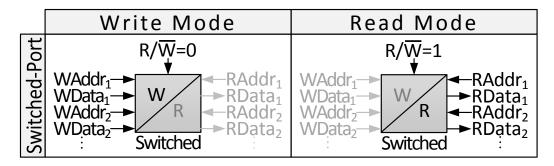

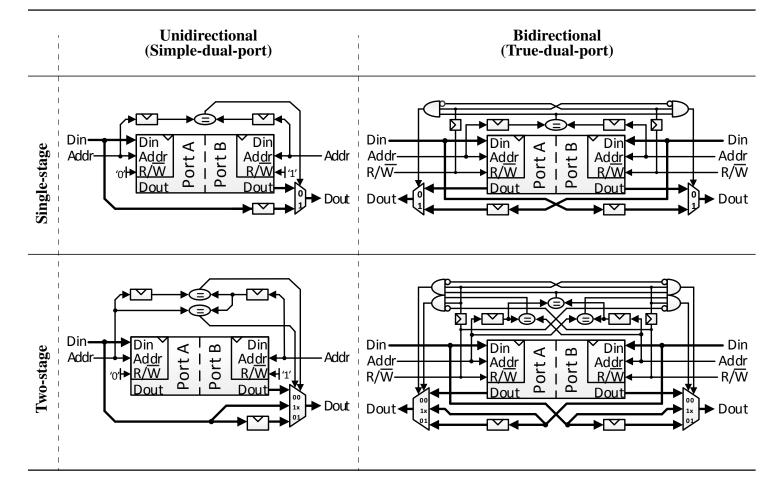

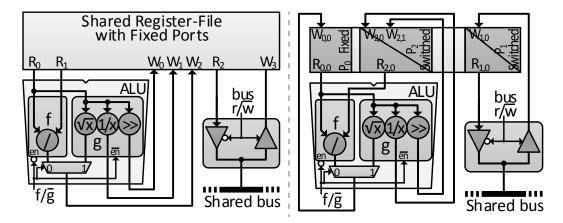

#### **1.4.2** Switched Ports

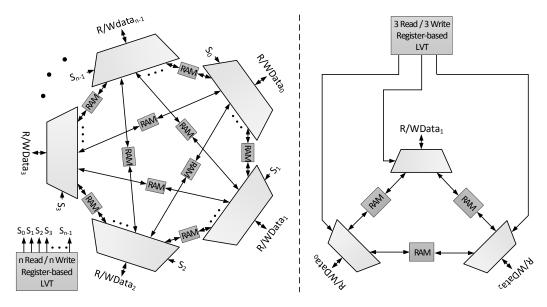

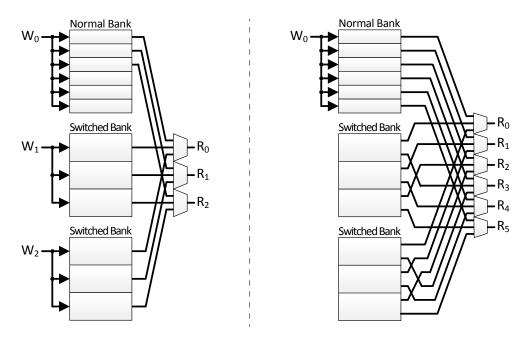

Switched ports, first introduced in [2], are a generalization of true (bidirectional) ports, where a certain number of write ports can be dynamically switched into a different number of read ports using a common read/write control signal. While a true port is a pair of read/write ports, switched ports are best described as a set of read ports and set of write ports. Furthermore, a given application may have multiple sets, each set with a different read/write control. While previous work generates multi-ported RAM solutions that contain only true ports [56], or only simple (unidirectional) ports, this research demonstrates that using only two models is too limiting and prevents optimizations from being applied. In particular, the use of switched ports can lead to a reduction in the amount of storage needed by the data banks. It does this by using the underlying true-dual-port capability of FPGA Block-RAMs.

The general problem of switched ports is optimized by solving the corresponding set cover problem via Integer Linear Programming (ILP). This is the first time such an optimization model is used to construct multi-ported memories. A memory compiler that automates the construction of a multi-ported RAM with switched ports was released as an open source library.

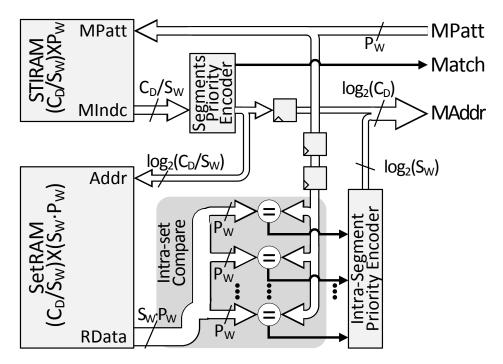

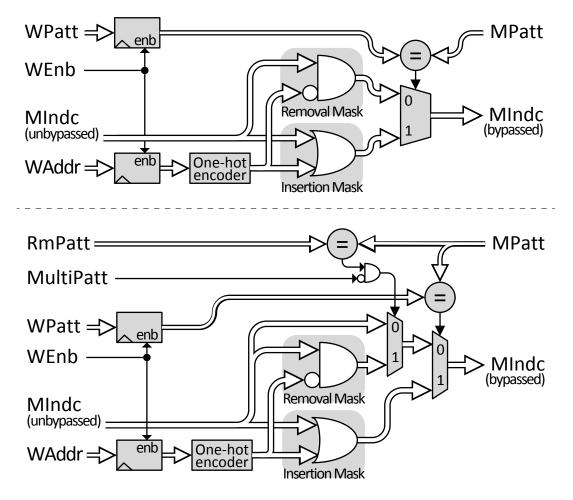

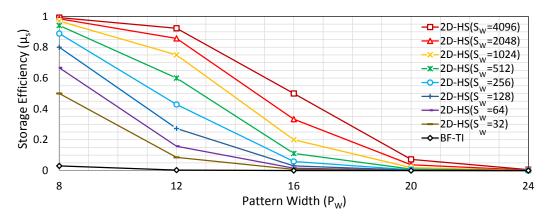

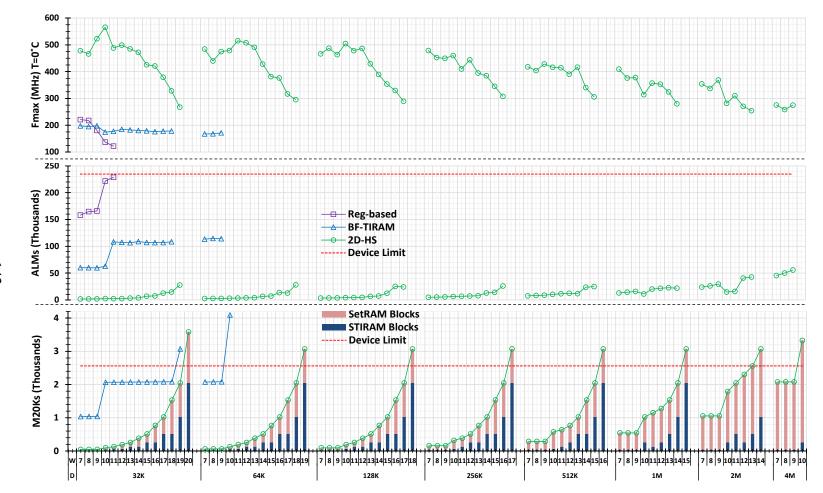

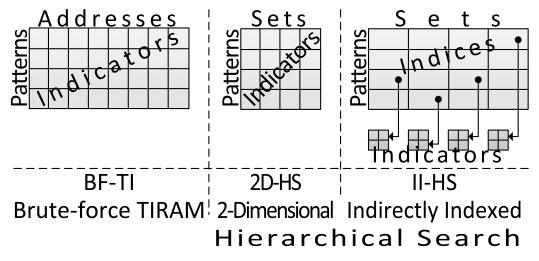

## 1.4.3 2-Dimensional Hierarchical Search BCAM (2D-HS-BCAM)

Due to the increasing amount of processed information, modern BCAM applications demand a deep searching space. However, traditional BCAM approaches in FPGAs suffer from storage inefficiency. The 2-Dimensional Hierarchical Search BCAM (2D-HS-BCAM) [4] is a novel and efficient technique for constructing BCAMs out of standard SRAM blocks in FPGAs. To achieve high storage efficiency, the suggested technique first searches for a row containing multiple patterns, then a search is done within the row for a precise match.

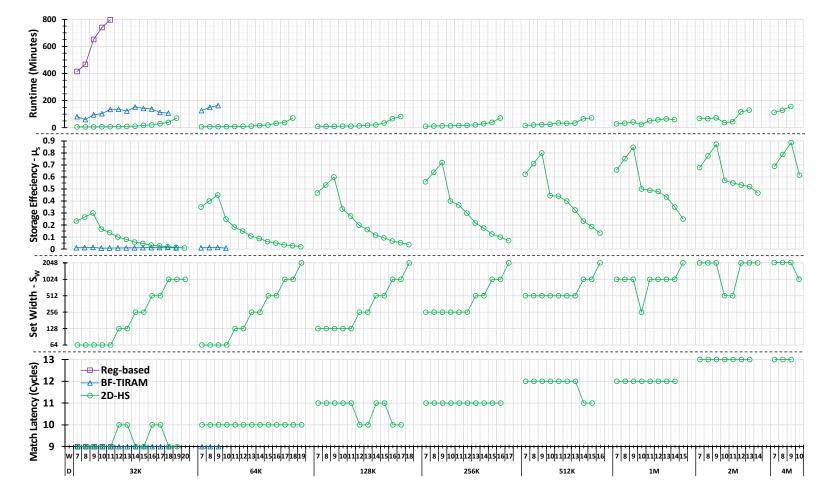

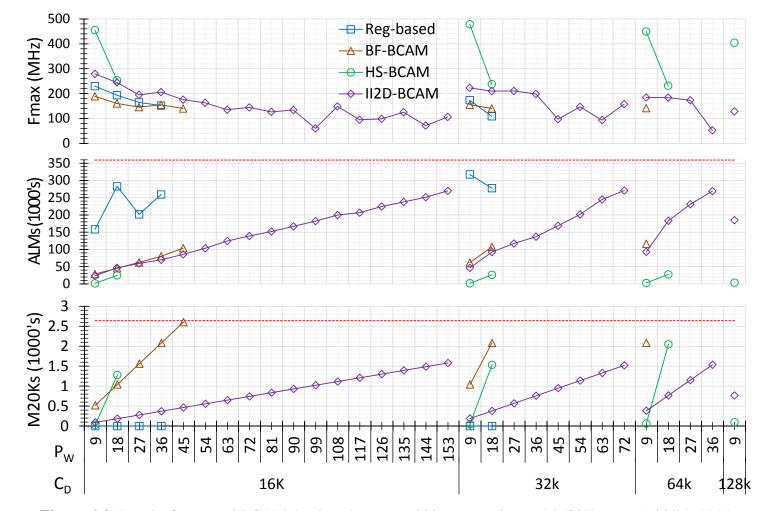

Using Altera's Stratix V device, the traditional design method achieves up to a 64K-entry BCAM while the proposed technique achieves up to 4M entries. For the 64K-entry test-case, the traditional method consumes 43 times more Adaptive Logic Modules (ALMs), 18 times longer mapping runtime, and achieves only one-third of the  $F_{max}$  of the proposed method. A fully parameterized Verilog implementation is being released as an open source hardware library. The library has been extensively tested using ModelSim and Altera's Quartus tools.

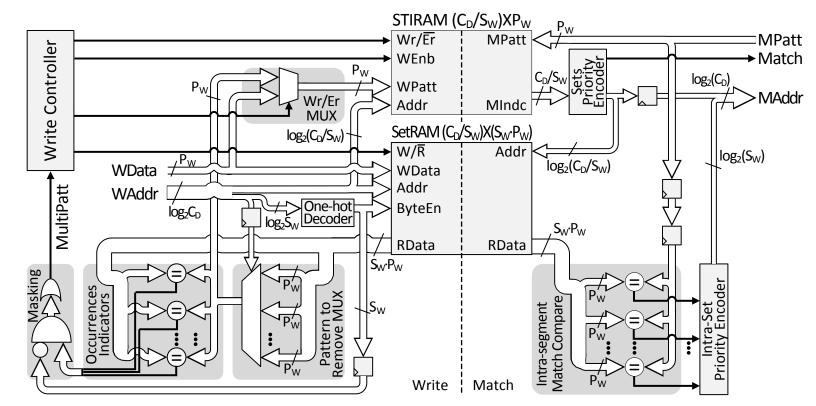

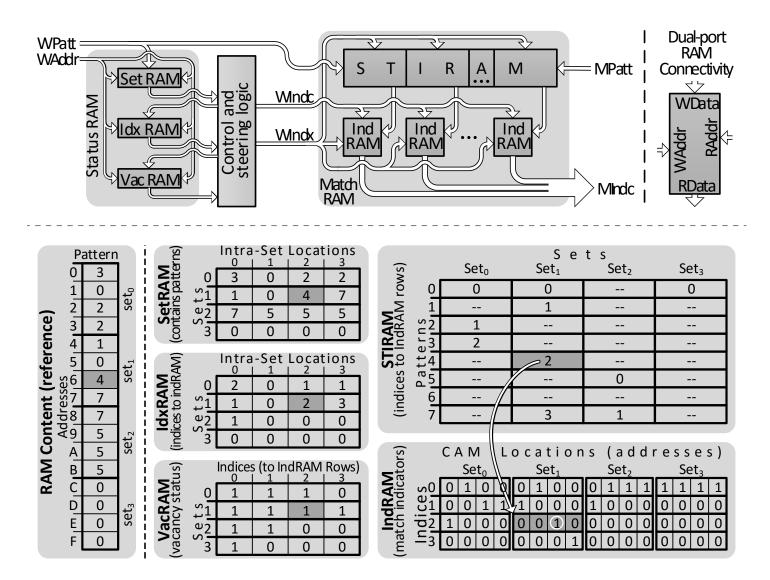

## 1.4.4 Indirectly Indexed Hierarchical Search BCAM (II-HS-BCAM)

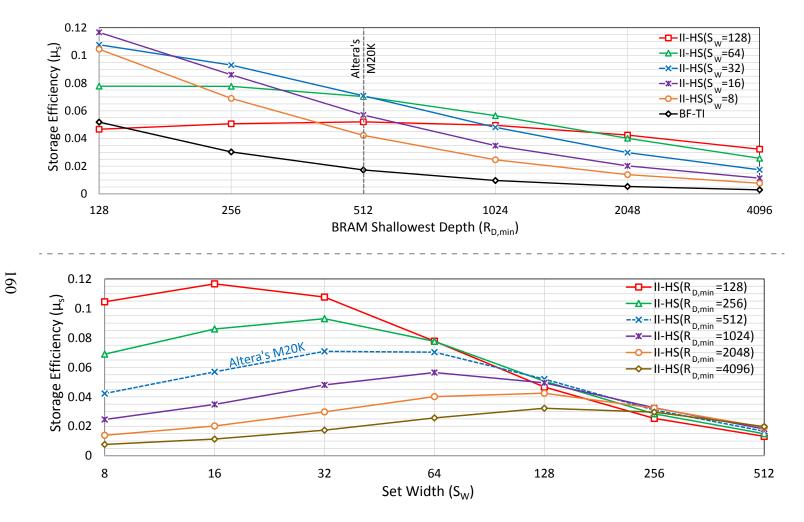

The hierarchical search just described does not allow wide CAMs to be constructed; it incurs an exponential growth as pattern width increases. The II-HS-BCAM [5] approach solves this by indirectly storing match indicators. This allows II-HS-BCAM blocks to be cascaded in pattern width, allowing for linear growth. Our method exhibits high storage efficiency and is capable of implementing up to nine times wider BCAMs compared to other approaches.

## **1.5** Research Methodology and Evaluation Metrics

In the section, we describe the research methodology, including design methodology, simulation and synthesis used throughout the dissertation. Furthermore, we review the evaluation metrics used to evaluate and compare our design to other techniques.

#### **1.5.1 Verilog Description**

All architectures which have been proposed in this dissertation, together with previous and standard approaches, have been fully developed as parameterized Verilog modules. The Verilog implementation is used to verify correctness and evaluate characteristics of the suggested architectures and compare to standard approaches and previous attempts.

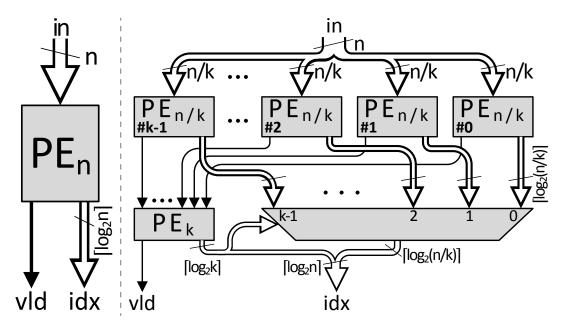

Some modules could not be described with Verilog directly. Alternatively, a Verilog generator was developed to generate these modules based on given design parameters. For instance, the Priority Encoder (PE) which was used in Chapter 5 and Chapter 6 to generate CAM match addresses has a recursive definition. Since Verilog is not capable of describing recursive modules, a generator was used to create the Verilog code recursively. In addition, the memory compiler in Chapter 4 requires solving a set-cover problem via Linear Programming (LP) to optimize the generated modules. Since performing this optimization process in Verilog is not possible, a Verilog generator was used to create Verilog code based on the optimized solution.

#### **1.5.2** Simulation and Synthesis

In each chapter, a large variety of different architectures and design parameters are swept and simulated in batch using Altera's ModelSim version 10.1e, each with over a million random cycles. All different design modules were compiled, mapped and fit using Altera's Quartus II version 14.0 [57] on Altera's Stratix V 5SGXMABN1F45C2 device [55]. This is a high-end performance-oriented speed grade 2 device with 360k ALMs, 2640 M20K blocks, and 1064 I/O pins. Half of the ALMs can be used to construct Memory Logic Array Blocks (MLABs), where a single MLAB consists of 10 ALMs.

A run-in-batch simulation and synthesis flow manager that simulates and synthesizes various designs with various parameters in batch using Altera's ModelSim and Quartus II is also provided. The Verilog modules, the Verilog generators, the algorithmic scripts, and the flow manager are available online as an open source contribution [58].

#### **1.5.3 Results Collection**

A general sweep is performed to test all combinations. Following this, the full set of results is analyzed. In this dissertation, we omit many of the in-between settings because they behaved as one might expect to see via interpolation of the endpoints.

The run-in-batch flow manager was also used to collect design results of the proposed and previous techniques. Performance evaluation (e.g.,  $F_{max}$ ) was generated by TimeQuest, the Quartus II Static Timing Analysis (STA) engine. Resource consumption, such as registers, Look-Up Tables (LUTs), ALMs, Logic Array Blocks (LABs), MLABs, and Block-RAMs (BRAMs), was collected after the design was fit to the Stratix V device by the Quartus II fitter.

### **1.5.4 BRAM Packing Approximation**

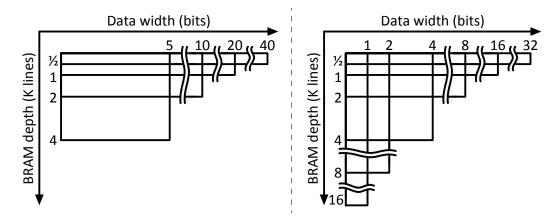

As shown in Figure 1.5, Altera's M20K blocks can be configured into several RAM depth and data width configurations [55]. The total amount of utilized SRAM bits can be either 16Kbits, or 20Kbits. Assuming that the RAM packing process minimizes the number of blocks cascaded in depth to avoid additional address decoding, each 16K lines will be packed into single bit-wide blocks, and the remainder will be packed into the minimal required configuration.

An estimation of the number of packed M20K blocks required to construct a RAM with a specific depth, d, and data width, w, is  $n_{M20K}(d,w)$ . This value is described as follows

Figure 1.5: Altera M20K configuration (left) 20Kb (right) 16Kb.

$$n_{M20K}(d,w) = \left\lfloor \frac{d}{16k} \right\rfloor \cdot \begin{cases} w & d\% 16k > 8k \\ \lfloor w/2 \ \rfloor & 8k \ge d\% 16k > 4k \\ \lfloor w/5 \ \rfloor & 4k \ge d\% 16k > 2k \\ \lfloor w/10 \rfloor & 2k \ge d\% 16k > 1k \\ \lfloor w/20 \rfloor & 1k \ge d\% 16k > \frac{1}{2}k \\ \lfloor w/40 \rfloor & \frac{1}{2}k \ge d\% 16k \end{cases}$$

(1.1)

## 1.6 Dissertation Organization

The rest of this dissertation is organized as follows. Chapter 2 provides a background on multi-ported memories and content-addressable memories in FPGAs. Standard and previous methods are surveyed and their limitations are discussed. Chapter 3 provides a detailed description of our near-optimal Invalidation-Based Live-Value Table (I-LVT) multi-ported memory. Multi-ported memories with switched port and the Multi-Switched-Ports Random Access Memory (MSPRAM) compiler are described in Chapter 4. The 2-Dimensional Hierarchical Search BCAM (2D-HS-BCAM), an efficient and deep BCAM for narrow patterns is provided in Chapter 5. Chapter 6 describes the Indirectly Indexed Hierarchical Search BCAM (II-HS-BCAM), an area-efficient and high-performance BCAM architecture, based on hierarchical search and compression techniques that supports wide patterns. Future directions and conclusions are drawn in Chapter 7.

# **Chapter 2**

# **Background and Related Work**

This chapter provides a background on multi-ported memories and content-addressable memories in FPGAs. Standard and previous methods are surveyed and their limitations are discussed.

## 2.1 RAM Multi-Porting Techniques in Embedded Systems

This section provides a review of current methods of creating multi-ported memories in embedded systems. Creating multi-ported access to register-based memories is described in Section 2.1.1. Multi-pumping is described in Section 2.1.2. Replicating a memory bank to increase the number of read and write ports is described in Section 2.1.3 and Section 2.1.4, respectively.

#### 2.1.1 Register-based RAM

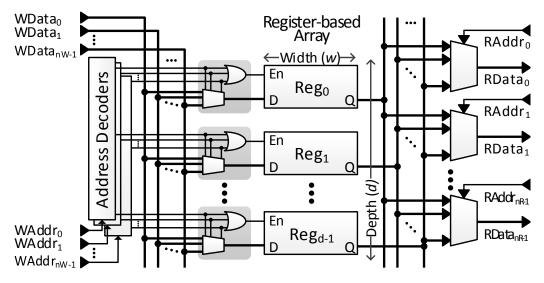

Multi-ported RAM arrays can be constructed using basic Flip-Flop (FF) cells and logic. As depicted in Figure 2.1, each writing port uses a decoder to steer the relevant written data into the addressed row. Each read port uses a mux to choose the relevant register output. This method is not practical for large memories due to area inflation, fan-out increase, performance degradation, and a decline in routability.

#### 2.1.2 RAM Multi-Pumping

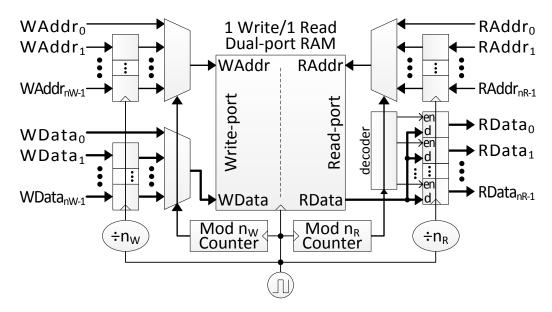

A time-multiplexing approach can be applied to an SRAM block to reuse access ports and share them among several clients, each during a different time slot. As depicted in Figure 2.2, addresses and data from several clients are latched then given round-robin access to a dual-ported RAM. The RAM must operate at a higher frequency than the rest of the circuit. If the maximum RAM frequency is similar to the pipe frequency, or a large number of access ports are required, then multi-pumping cannot be used.

In FPGAs the process of generating multi-pumped memories can be automated and tailored for heterogeneous applications [59–62]. Furthermore, the multipumping methods can be combined with other techniques to save area [63]. A number of designs utilize multi-pumping to gain additional access ports while keeping area overhead minimal [64, 65]. The 2.3GHz Wire-Speed POWER processor uses double-pumping to double the writing ports [66].

Figure 2.1: Register-based multi-ported memory.

**Figure 2.2:** Multi-pumping: RAM is overclocked, allowing multiple access during one pipeline cycle.

#### 2.1.3 Multi-Read RAM: Bank Replication

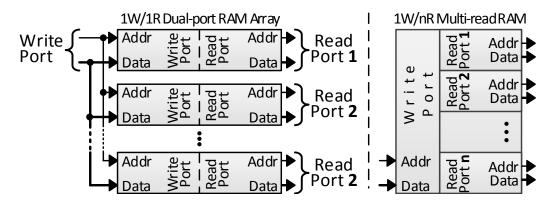

To provide more reading ports, the whole memory bank can be replicated while keeping common write address and data as shown in Figure 2.3. Data will be written to all bank replicas at the same address, hence reading from any bank is equivalent. This method incurs high SRAM area and consumes more power. However, the replication approach has two strong advantages over other multiporting approaches. The first is the simplicity and modularity of bank replication. The second is that read access time is unaffected as the number of port increases; only write delays increase due to fan-out, but this can be hidden by pipelining and bypassing. The bank replication technique is commonly used in state-of-the-art processors to increase parallelism. The 2.3GHz Wire-Speed POWER processor replicates a 2-read SRAM bank to achieve 4 read ports [66]. Each of the two integer clusters of the Alpha 21264 processor has a replicated 80-entry register file, thus doubling the number of read ports to support two concurrent integer units. Similarly, the 72-entry floating-point register file is duplicated, supporting two concurrent floating-point units [67].

#### 2.1.4 Multi-Write RAM: Emulation via Multi-banking

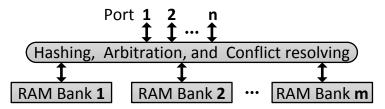

Multi-ported memories are very expensive in terms of area, delay, and power for a large number of ports. The overhead of multi-porting can be reduced by multi-banking if one relaxes the guaranteed access delay constraint. As depicted in Figure 2.4, the total RAM capacity can be divided into several banks, each with few ports (e.g., dual-port). A fixed hashing scheme is used to match each address

**Figure 2.3:** (left) Replicated dual-ported banks with a common write port. (right) Multi-read RAM symbol used in this dissertation.

Figure 2.4: Multi-banking: RAM capacity is divided into several banks. Ports access with a fixed hashing scheme.

to a single bank; often, the address MSBs are used. Arbitration logic steers access from multiple ports to each bank. Since two ports can request access to the same bank at the same time, a conflict resolving circuit determines which port grants access to a specific bank. The other port will miss the arbitration and is required to request access again. Not only does this approach provide unpredictable access latency due to the arbitration miss, but it also increases delay due to the additional circuitry. Several approaches have been proposed to improve multi-banking [6, 68– 71]. State-of-the-art memory controllers and caches are based on multi-banking due to area and power efficiency. For example, Intel's i486 CPU has a data cache with 8 interleaved banks and two access ports [72].

## 2.2 Multi-ported SRAM-based Memories: Prior Work

In this section a review of three previous multi-ported SRAM-based memories are provided. The first approach is based on multi-banking with a LVT [11, 73] and is described in Section 2.2.1. The second approach retrieves the latest written data by utilizing logical XOR properties [12, 73] and is described in Section 2.2.3. Constructing data banks with true ports support are provided in Section 2.2.2. These methods are surveyed and their limitations are discussed.

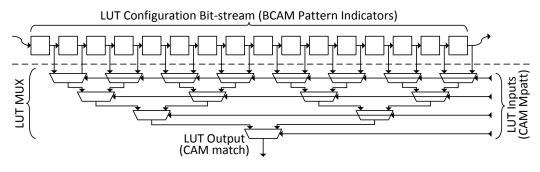

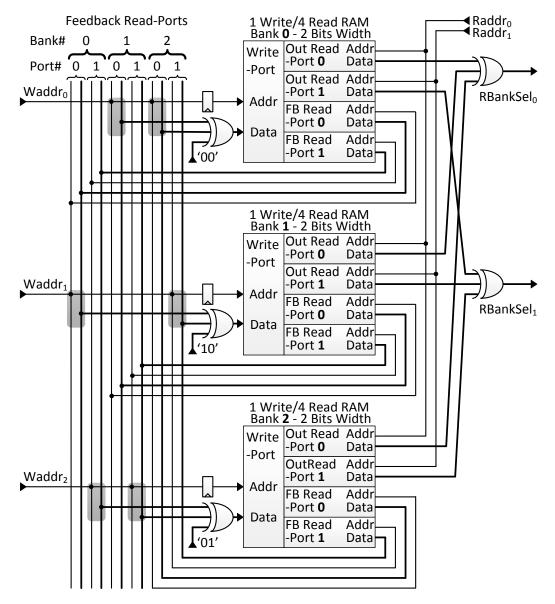

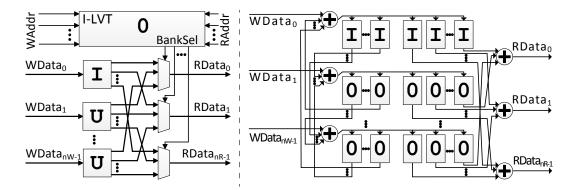

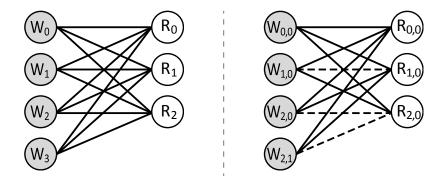

#### 2.2.1 LVT-Based Multi-ported RAM

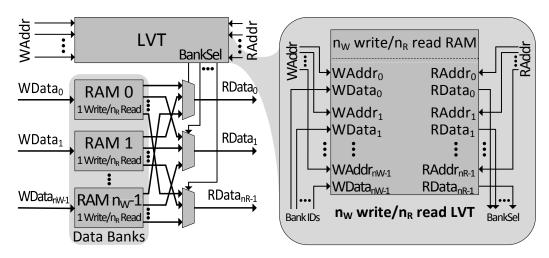

As depicted in Figure 2.5 (left), LVT-based multi-ported memories are compromised of two portions, LVT and data storage. In the data storage, each storage bank has a single write port and  $n_R$  read ports. This bank is replicated  $n_W$  times, where  $n_W$  and  $n_R$  are the number of write ports and read ports respectively. When a write port writes data to a specific address, the LVT is updated to indicate the port of this latest write operation. When this address is later read, the LVT provides this write port ID to retrieve the correct data.

For each RAM address, the LVT stores the ID of the bank replica that holds the latest data. The data storage uses a different bank replica for each writing port, while each bank replica has several reading ports. All banks are accessed by all read addresses in parallel; the LVT helps to steer the read data out of the correct bank since it holds the ID of last accessed (written) bank for each address.

Actually, the LVT itself is a multi-ported memory with the same depth and

Figure 2.5: (left) LVT-based multi-ported memory. (right) An LVT implemented using multi-ported memory.

number of writing ports as the implemented multi-ported RAM. However, since the LVT stores only bank IDs, the data (line) width of the LVT table is only  $\lceil \log_2 \rceil$ of writing ports. As described in Figure 2.5 (right), the LVT doesn't have write data, instead it writes a fixed bank ID for each port.

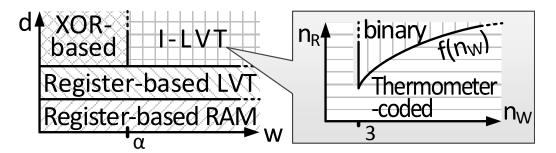

Since an LVT is a narrow multi-port memory, it is implemented as a registerbased multi-ported memory. As explained in Section 2.1.1, register-based RAM is not suitable for building deep memories. While the LVT width is only log<sub>2</sub> of the number of writing ports, the depth of the LVT is still identical to the depth of the original RAM. *This is the main cause of the area overhead*. In Chapter 3 we present two methods for building the LVT out of Block-RAMs instead of registers, allowing deep and wide multi-ported memories to be constructed much more efficiently.

Assuming that bank IDs are binary encoded, the total number of registers

required to implement the LVT is

$$d \cdot \lceil \log_2 n_W \rceil, \tag{2.1}$$

where d is the depth of the memory.

For deep memories, the large number of registers and huge read multiplexers make register-based LVTs impractical. For example, a Stratix V GX A5 device (185k ALMs) can fit up to 16k-deep memory with four write ports.

For the data storage part, a total of  $n_W$  multi-read banks are required for each write port. Each multi-read bank supports  $n_R$  read ports, allowing the LVT to select the required data block. The total number of SRAM cells in the data storage is

$$d \cdot w \cdot n_W \cdot n_R, \tag{2.2}$$

where *w* is width of data.

Using Altera's Stratix M20K BRAMs , the total number of required M20K blocks for the data storage is

$$n_{M20K}(d,w) \cdot n_W \cdot n_R. \tag{2.3}$$

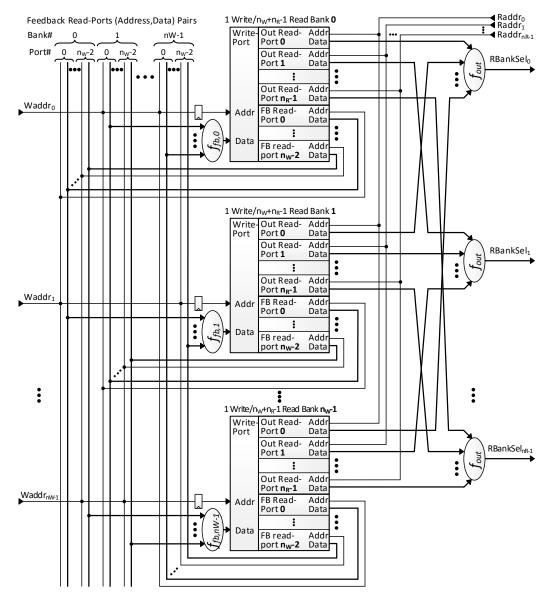

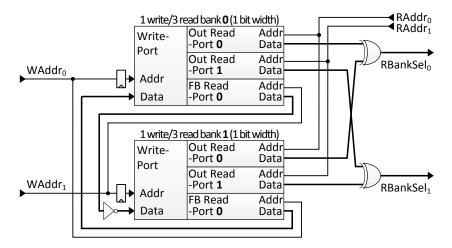

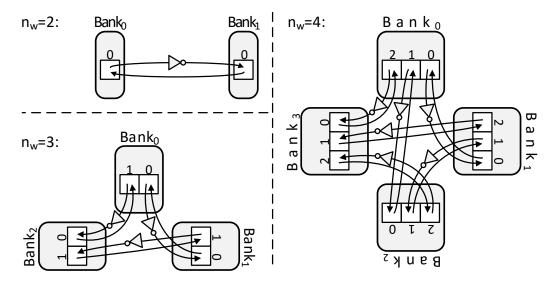

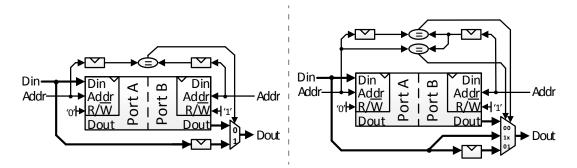

## 2.2.2 Multi-Ported Random Access Memories with True Dual-Ports

In the previous subsection, the data storage portion is built with simple read and simple write parts. Two papers [56, 73] introduced a modification to the data banks

to build a multi-ported memory where all ports are true (bidirectional) ports. This is achieved by utilizing the bidirectional functionality of underlying true-dual-port BRAMs in the FPGA. Figure 2.6 (left) illustrates a generalization of this method. Each port either writes to a set of data banks, or reads from them. *Every pair of ports has one data bank in common*, hence, when a port reads, it can access data written from any other port. A register-based LVT determines which bank holds the latest data. Figure 2.6 (right) describes an example of a RAM with 3 true-ports. This problem is identical to the mathematical handshakes problem, where each port must connect (handshake) to all other ports via a RAM. Hence, a total of

$$\frac{1}{2} \cdot n_t \cdot (n_t - 1) \tag{2.4}$$

data copies are required, where  $n_t$  is the number of bidirectional (true) ports. In contrast, the original LVT approach [11] requires  $n_t^2$  data copies. Nevertheless, this true-port RAM architecture is still based on a register-based LVT, hence it suffers from the same shortcomings.

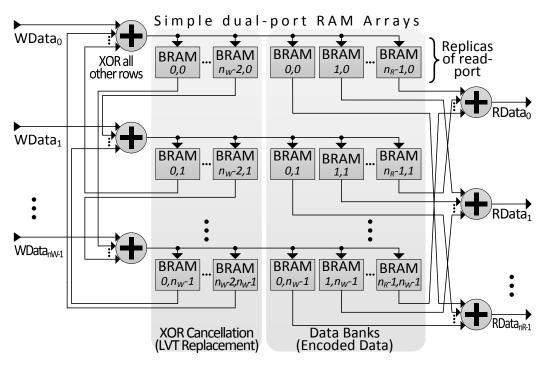

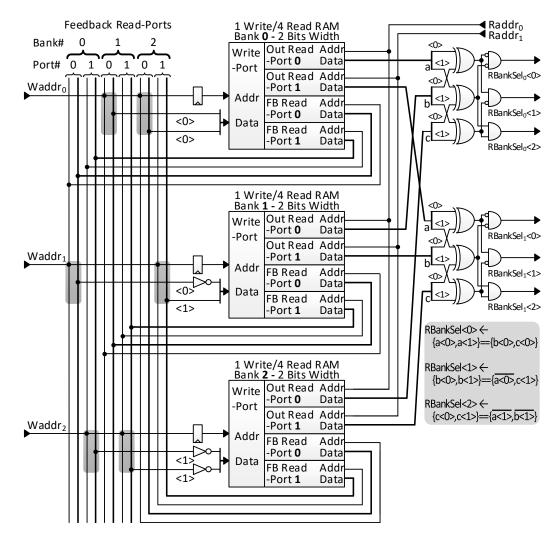

#### 2.2.3 XOR-Based Multi-Ported RAM

While the two LVT-based multi-ported memories just shown implement their LVTs as a register-based multi-ported memory, the XOR-based multi-ported memory is implemented using SRAM blocks [12, 73]. This makes it more efficient for deep memories. However, as will be shown, it is inefficient for wide memories.

The XOR-based method utilizes the special properties of the XOR function

**Figure 2.6:** Data banks with bidirectional true-ports support. Each port share a single BRAM with any other port.(left) Generalized approach. (right) A 3 true-ports example.

to retain the latest written data for each write port [74]. XOR is commutative  $a \oplus b = b \oplus a$ , associative  $(a \oplus b) \oplus c = a \oplus (b \oplus c)$ , zero is the identity  $a \oplus 0 = a$ , and the inverse of each element is itself  $a \oplus a = 0$ .

Like the previous methods, the XOR-based method contains two structures: one replaces the LVT and is used to encode written data, while the other is similar to the data storage but it stores encoded data.

As illustrated in Figure 2.7, each write port has a bank with multi-read and a single write. Some of the read ports are used as a feedback to encode the data to be rewritten, while the remaining read ports generate the data output. To perform a write, the new data is XOR'ed together with all the old data from the other banks; this encoded value is written to the corresponding bank. Hence if an address *A* is

written through write port *i* with data WData<sub>i</sub>, Bank<sub>i</sub> will be written with

$$Bank_i[A] \leftarrow Bank_0[A] \oplus Bank_1[A] \oplus \cdots \oplus WData_i \oplus \cdots \oplus Bank_{n_W-1}[A].$$

(2.5)

A read is performed by XOR'ing all the data for the corresponding read address from all the banks, hence,

$$RData_{i}[A] \leftarrow Bank_{0}[A] \oplus Bank_{1}[A] \cdots \oplus Bank_{n_{W}-1}[A].$$

(2.6)

Substituting  $Bank_i[A]$  from (Equation 2.5) into (Equation 2.6) and applying commutative and associative properties of the XOR shows that each bank appears twice in the XOR equation, hence will be cancelled since XORing similar elements is 0. The only remaining item will be  $WData_i$ , the required data.

The XOR-based multi-ported memory requires  $n_W$  multi-read banks for each write port. Each multi-read bank supports  $n_W - 1$  read ports for feedback, and  $n_R$  read ports. Each feedback read port is of width d, to match the write data, so these feedback memories can be quite large. The number of required SRAM cells for the entire multi-ported memory is

$$d \cdot w \cdot n_W \cdot (n_R + n_W - 1). \tag{2.7}$$

Using Altera's Stratix M20K BRAMs, the total number of required M20Ks is

$$n_M 20K(d, w) \cdot n_W \cdot (n_R + n_W - 1).$$

(2.8)

Figure 2.7: XOR-based multi-ported memory.

Since FPGA Block-RAM is synchronous, data feedbacks are read with a one-cycle read delay. Hence, the written data, their addresses and write-enables must be retimed to match the feedback data. This requires the following number of registers

$$n_W \cdot (w + \lceil \log_2 d \rceil + n_W). \tag{2.9}$$

## 2.3 FPGA-Based Binary Content-Addressable Memories (BCAMs)

CAMs are usually designed at the transistor level [49–53]. Older FPGA devices, including Altera's FLEX, Mercury and APEX devices [54], employed minor

architectural features to support small CAM blocks. However, FPGA vendors do not provide dedicated hard cores for CAMs in modern devices. These have been replaced with soft CAM cores that employ a brute-force approach. While the address space in modern databases can easily exceed millions of entries, traditional CAM techniques in FPGAs cannot satisfy these requirements. Wide and shallow RAMs are needed to efficiently implement brute-force BCAMs, yet BRAM width is growing slowly.

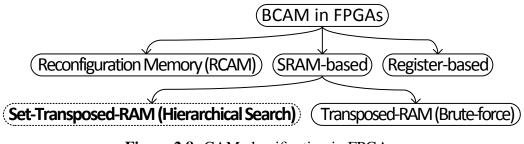

CAMs can be classified into two major classes: Binary Content-Addressable Memories (BCAMs) and Ternary Content-Addressable Memories (TCAMs). While BCAMs hold binary values only, TCAMs can hold don't care values (X's) that can match any value of the corresponding pattern bit. In this dissertation, we focus on CAM architecture in FPGAs. As depicted in Figure 2.8, CAM architecture in FPGAs can be classified into three categories, based on the FPGA memory resources they utilize. The first is register-based where registers are used to store patterns and concurrently compare all register values, however, register resources are limited, a state-of the art Altera's Stratix V device [55] can provide up to 32Kentries of a single byte pattern BCAM. SRAM blocks are utilized in the second approach to store for each pattern if it exists in any of the address individually, hence the name transposed RAM, also known as the brute-force approach. The same Altera Stratix V device can realize a CAM with byte-wide patterns up to 64K in depth. The third method is reconfigurable Reconfiguration Memory Based Content-Addressable Memory (RCAM), where LUT configuration memory is utilized. It is possible to implement a 128K-line single byte pattern RCAM on the

Figure 2.8: CAM classification in FPGAs.

same Stratix V device. However, a LUT's SRAM configuration is written serially, which adversely affects writing throughput. The following subsections provide a detailed review for these categories.

This section provides a review of current BCAM architectures in FPGAs. Using registers to create BCAMs is described in Section 2.3.1. The traditional brute-force BRAM-based approach is described in Section 2.3.2. BCAM pattern width cascading is described in Section 2.3.3. Reconfiguration Memory Based Content-Addressable Memories (RCAMs) are explained in Section 2.3.4. Alternative algorithmic searches are briefly described in Section 2.3.5. A review of FPGA vendors' supports of BCAMs is placed in Section 2.3.6.

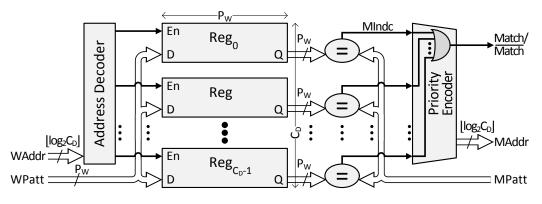

#### 2.3.1 Register-Based BCAMs

The flexibility of reading and writing flip-flops makes it possible to concurrently read and compare all the patterns as depicted in Figure 2.9. Similar to a registerbased RAM, an address decoder is used to generate one-hot decoded address lines, enabling a single line for writing. Each registered pattern is compared with the Match Pattern (MPatt) simultaneously; the comparison results drive the match

Figure 2.9: Register-based BCAM.

line, also called Match Indicators (MIndc) followed by a priority-encoder to detect the first Match Address (MAddr). The high demand for limited resources such as registers, comparators, address decoder and priority encoder (proportional to BCAM depth), make this approach infeasible for deep BCAMs; using Altera's high-end Stratix V device [55], only a one byte-wide, 32K-depth BCAM can be generated.

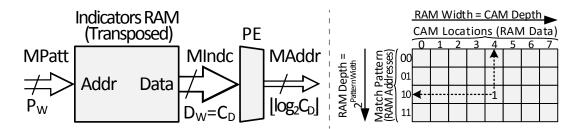

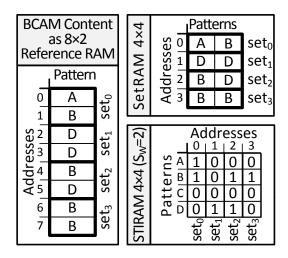

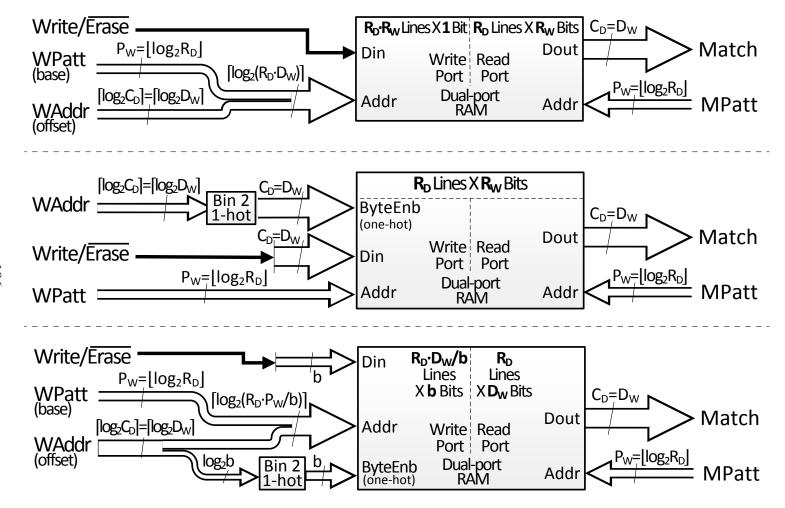

## 2.3.2 Brute-Force Approach via Transposed Indicators RAM (TIRAM)

The brute-force approach creates BCAMs out of standard BRAMs. These BRAMs are addressed with the match pattern, thus allowing a single cycle pattern match. This approach is utilized by FPGA vendor IP libraries or application notes. As depicted in Figure 2.10, a BRAM is addressed by the match pattern while each bit of the RAM data bits indicates the existence of the pattern. The data bit position corresponds to the BCAM address location. Thus, the depth of the CAM,  $C_D$ , must match the width of the data RAM,  $D_W$ . Also, the pattern width,  $P_W$ , of the CAM

**Figure 2.10:** (left) CAM as a Transposed-RAM followed by a Priority Encoder (PE). (right) Example of a pattern indicator for pattern '10' in address 4.

must match the address width of the data RAM, i.e.,  $P_W = \lceil log_2 R_D \rceil$ , where  $R_D$  is RAM depth.

In this dissertation, the Transposed Indicators RAM (TIRAM) structure in Figure 2.10 (left) is described as a matrix of indicators

$$TIRAM = \begin{bmatrix} I_{0,0} & I_{0,1} & \cdots & I_{0,C_D-1} \\ I_{1,0} & I_{1,1} & \cdots & I_{1,C_D-1} \\ \vdots & \vdots & \ddots & \vdots \\ I_{|P|-1,0} & I_{|P|-1,1} & \cdots & I_{|P|-1,C_D-1} \end{bmatrix}$$

(2.10)

$$\forall a \in A, p \in P : I_{p,a} = (RAM [a] EQ P),$$

Where *A* is the address space set and *P* is the pattern set in the corresponding RAM structure.

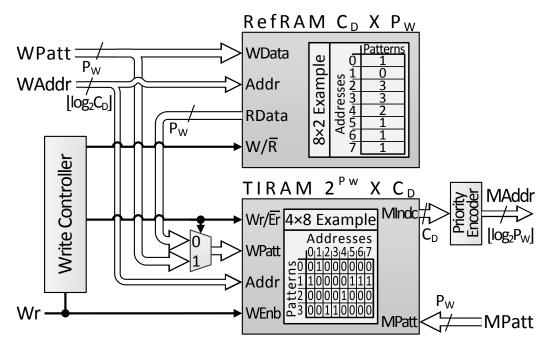

The complete system of the brute-force TIRAM approach is described in Figure 2.11. Reading from the TIRAM is performed by providing the Match Pattern (MPatt) as address to read the Match Indicators (MIndc) for the entire BCAM address space for this specific match pattern. A priority encoder detects the first Match Address (MAddr) from the match indicators. However, writing (also called or updating) to the TIRAM structure requires more computation since it requires setting the new match indicator and clearing the old match indicator. Appendix A provides the detailed writing mechanism of the brute-force TIRAM BCAM.

To implement a BCAM with  $C_D$  entries and  $P_W$  pattern width, namely a  $C_D \times P_W$  BCAM, The brute-force TIRAM approach requires  $C_D \cdot P_W$  SRAM cells for the Reference RAM (RefRAM), shown in Figure 2.11, which stores a copy of the Pattern written to at each CAM location. In contrast, the TIRAM requires  $2^{P_W} \cdot C_D$  SRAM cells, for a total of:

$$C_D \cdot P_W + 2^{P_W} \cdot C_D. \tag{2.11}$$

Assuming that RefRAM is fully utilized, and the TIRAM uses the widest BRAM configuration, the BRAM count is estimated as

$$\left\lceil \frac{C_D \cdot P_W}{R_{D,min} \cdot R_{W,max}} \right\rceil + \left\lceil \frac{2^{P_W}}{R_{D,min}} \right\rceil \cdot \left\lceil \frac{C_D}{R_{W,max}} \right\rceil,$$

(2.12)

where  $R_{W,max}$  and  $R_{D,min}$  are BRAM parameters indicating the maximum width, and minimum depth, respectively.

This BRAM-based brute-force approach is adopted by Xilinx [75–78] and Altera [79] to create soft CAMs as described in their application notes. Zerbini and Finochietto [80] apply the pattern width cascaded brute-force approach to emulate TCAMs for packet classification; however updating the TCAM content is not dis-

**Figure 2.11:** Brute-force TIRAM approach with  $8 \times 2$  example.

cussed. Jiang [81] also uses the brute-force approach to emulate TCAMs, however, a pattern update requires a sequential rewriting of all RAM addresses for each pattern. Ullah *et al.* [82–85] also use the brute-force approach, but their TCAMs can be partitioned, allowing the search of specific TCAM fragments. However, the required storage is still similar to the brute-force approach. Furthermore, rewriting the TCAM requires a serial rewriting of all RAM locations.

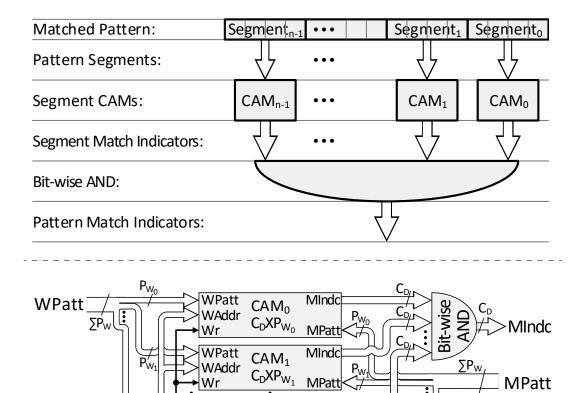

## 2.3.3 BCAM Pattern Width Cascading and Scaling

As shown in Equation 2.11, SRAM cell usage for the brute-force TIRAM approach is exponential to pattern width  $P_W$ . A wide pattern width will make the SRAM requirements infeasible. BCAM pattern width cascading relaxes this SRAM growth from exponential into linear. As depicted in Figure 2.12, the BCAM pattern (both matched and written pattern) is divided into smaller pattern segments; each segment is associated with a separate BCAM. The BCAM pattern width cascading technique is used by Xilinx[75–78] and Altera [79] to create soft scalable BCAMs as described in their application notes.

The write operation writes every pattern segment into its corresponding BCAM, while match operation matches each pattern segment with its corresponding BCAM. A match for the entire pattern is found if a match is found for all segments individually at the same BCAM location (hence the bitwise AND). The optimal pattern segment width is determined by the minimal depth  $R_{D,min}$  of the BRAM, namely the shallowest and widest configuration, since choosing a wider pattern requires exponential growth. The optimal pattern width is therefore  $P_{W,opt} = \lfloor log_2(R_{D,min}) \rfloor$  and the total number of BCAM pattern segments cascades is  $n_C = \left\lceil \frac{P_W}{P_{W,opt}} \right\rceil$ .

One stage of TIRAM will consume  $\left\lceil \frac{C_D}{R_{W,max}} \right\rceil$  BRAMs and the total BCAM consumption of the TIRAM is therefore

$$n_C \cdot \left( \left\lceil \frac{C_D}{R_{W,max}} \right\rceil + \left\lceil \frac{C_D \cdot P_{W,opt}}{R_{D,min} \cdot R_{W,max}} \right\rceil \right).$$

(2.13)

The linear relation to  $P_W$  and  $C_D$  in Equation 2.13 is clear, in contrast to the uncascaded version in Equation 2.12 where the relation to  $P_W$  is exponential.

CAM<sub>n-1</sub>

WPatt

log<sub>2</sub>C<sub>C</sub>

MIndc

**Figure 2.12:** BCAM pattern width cascading: (top) abstraction, (bottom) details.

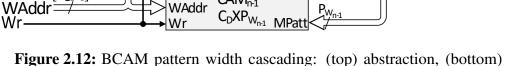

## 2.3.4 Reconfiguration Memory Based Content-Addressable Memories (RCAMs)

FPGA configuration memory is an SRAM chain loaded with the configuration bit-stream via a serial link and is used to configure the device functionality, mainly routing and logic (LUT) functionality. A segment of this configuration chain is shown in Figure 2.13, where it used to configure a 4-input LUT. A modern FPGA device accommodates several Mbits of configuration SRAM cells, for instance, Altera's Stratix V E device contains 22Mbits of configuration bits for LUTs only [55].

The SRAM reconfiguration memory in FPGAs can be utilized as a wide and shallow memory to generate Reconfiguration Memory Based Content-Addressable Memories (RCAMs). As depicted in Figure 2.13, a LUT MUX chooses one SRAM cell for each specific input that represents the LUT function for this input. Alternatively, the LUT input is used as a BCAM match pattern, and the LUT configuration SRAM cells indicates for a single CAM address if this specific pattern exists. Hence, a 4-inputs LUT fits a single address BCAM with 4-bits pattern, namely a  $1 \times 4$  BCAM. The address space can be increased by searching concurrently the same pattern for several BCAMs, i.e., sharing LUT inputs. The pattern width can be increased by cascading BCAM blocks as described in Section 2.3.3.

Due to its inherent nature, a variety of device-dependent RCAM approaches has been proposed [86–92]. All these device-dependent methods utilize Xilinx devices reconfiguration capabilities via JBits [93], a Java based Application Programming Interface (API) to reconfigure Xilinx devices by accessing and modifying the configuration bit-stream. However, RCAM writing requires rewriting the entire bit-stream or parts of it, in case partial reconfiguration is supported. In addition, using LUTs as RCAMs will block logic resources.

On the other hand, Altera's Stratix devices provides full accessibility to LUT configuration memory as SRAM blocks with decoded addresses called MLABs [55]. However, the LUT configuration memory can be used either for LUT configuration or as part of the MLABs. For example, each ALM of the Stratix V device can

accommodate a 6-input LUT, hence 64 configuration bits. Each 10 ALMs (a single LAB) creates a simple dual-ported  $64 \times 10$  or  $32 \times 20$  MLAB block. MLABs can be utilized to create BCAMs in a similar method as the reconfiguration memory, although the writing mechanism is different.

Other approaches cascade *logic LUTs* to generate area-efficient CAM [94–97]. However, writing to these CAMs is either not supported or requires rewriting the LUT content. Furthermore, logic resources are limited and incur increased delays.