#### Lecture #6

## Operational Amplifiers (Op Amps)

## Outline/Learning Objectives:

- Analyze and design simple signal-conditioning circuits based on OpAmps.

- Assess and understand some practical limitations of OpAmps.

- Use the electronics laboratory to investigate the electrical behavior of simple circuits and devices in co-requisite course.

## From Chapter 11 in Jaeger, Chapter 5 in Spencer

# Selected problems:

11.7, 11.13, 11.15, 11.41, 11.58, 11.78, 11.87

# Why study operational amplifiers?

The operational amplifier is a fundamental building block of analog circuit design.

The name "operational amplifier" originates from the use of this type of amplifier to perform specific electronic circuit functions or operations, such as scaling, summation, and integration, in analog computers.

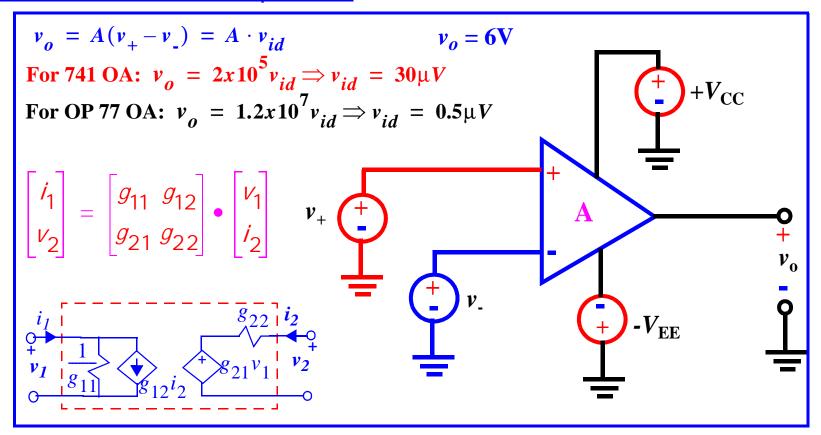

## The Differential Amplifier

## The Differential Amplifier\_

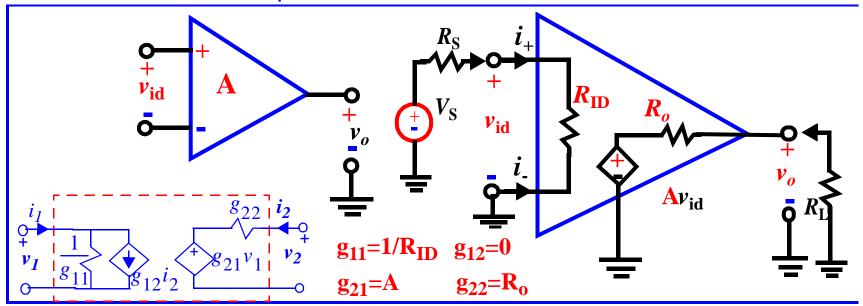

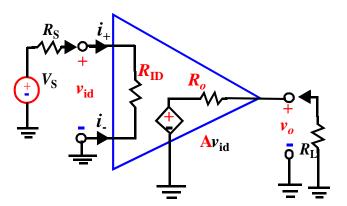

Define - A,  $v_{id}$ ,  $R_{ID}$  and  $R_o$ .

Explain the simplified g-parameter representation of the diff. amp.

Diff. amp.,

$$v_o = Av_{id} \cdot \frac{R_L}{R_O + R_L}$$

;  $v_{id} = v_s \cdot \frac{R_{ID}}{R_{ID} + R_s}$ . Note  $v_s = v_{id} \cdot \frac{R_{ID} + R_s}{R_{ID}}$ . Therefore,  $A_V = \frac{v_o}{v_s} = A\frac{R_L}{R_O + R_L} \cdot \frac{R_{ID}}{R_{ID} + R_s}$ .

In an ideal diff. amp,  $R_{ID} \gg R_s$  and  $R_O \ll R_L$  (fully mismatched R case), we have  $v_o = A v_{id}$ ,  $v_{id} = v_s$  and  $A_V = A$ .

## The Ideal Differential Amplifier

- Infinite gain (A);  $A \rightarrow \infty \Rightarrow v_{id} \rightarrow 0$ .

- Infinite input resistance;  $R_{ID} \rightarrow \infty$ .

- Zero output resistance;  $R_0 \rightarrow 0$ .

- Zero input-offset voltage;  $\pm v_{os} \rightarrow 0$ .

- Infinite common-mode rejection ratio (CMRR).

- Infinite power supply rejection ratio (PSRR).

- Infinite output voltage range.

- Infinite output current capability.

- Infinite open-loop bandwidth.

- Infinite slew-rate.

Real OA depart from ideal. However, the ideal characteristics implies that we need not be bothered by, for example, the OP loading characteristics.

#### Some conceptualizations to simplify OA analysis

- (1) For V purposes, IP port appears as a SC, i.e.,  $v_{id} \rightarrow 0$

- (2) For I purposes, IP port appears as an OC, i.e.,  $i_+ \rightarrow 0$ ;  $i_- \rightarrow 0$ .

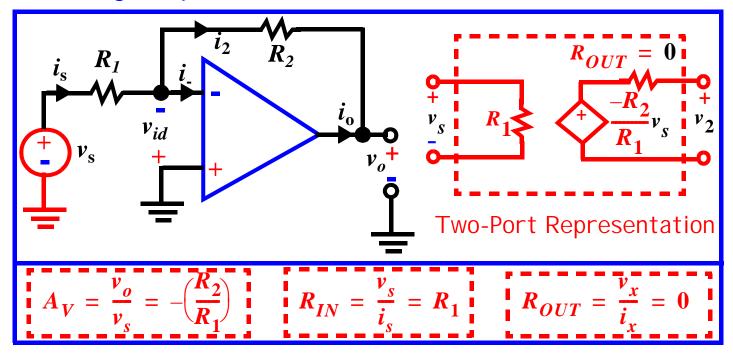

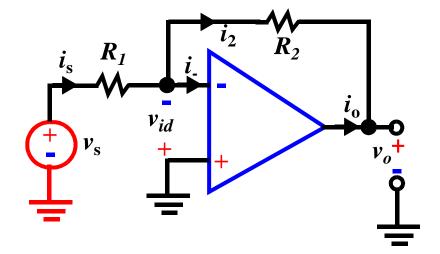

## The Inverting Amplifier \_

$$v_{+} = 0$$

and  $v_{-} = \frac{R_{2}}{R_{1} + R_{2}} v_{s} + \frac{R_{1}}{R_{1} + R_{2}} v_{o} = (1 - \beta) v_{s} + \beta v_{o}$

For inv. amp.,

$$A_V = \frac{v_o}{v_s} = \left(1 - \frac{1}{\beta}\right) \cdot \frac{1}{1 + \left(A\beta\right)^{-1}}$$

.  $\beta$  - feedback factor.

$$A_{V,ideal} = \lim_{A \beta \to \infty} (A_V) = \left(1 - \frac{1}{\beta}\right) = -\frac{R_2}{R_1}$$

#### The Inverting Amplifier

Suffers from low  $R_{IN}$  since cannot make  $R_{IN}$  too large because of  $A_{V}$ .

OP is phase shifted by  $\pi$  radians (180°) from IP.  $A_V$  depends only on the ratio of R's. This is important, e.g., R's can vary with temperature, but their ratio remains the same. That is, we can make a stable circuit using unstable components.

Example: Refer to the inverting amplifier circuit on the previous page, what is the voltage gain  $A_V$  if  $R_1=80~\Omega$ ,  $R_2=8~\mathrm{k}\Omega$ , and  $v_S(t)=0.15\sin(3000t)$  V. Write an expression for the current  $i_S(t)$  and output voltage  $v_O(t)$ .

$$A_V = -\frac{R_2}{R_1} = -\frac{8k}{80} = -100$$

$$I_S = \frac{V_S}{R_1} = \frac{0.15}{80} = 1.875 mA$$

$$\therefore i_S(t) = 1.875\sin(3000t)mA$$

$$v_O(t) = -15\sin(3000t)V$$

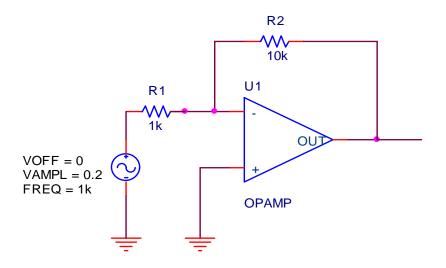

#### **PSPICE EXAMPLE**

#### Libraries:

- \* Local Libraries:

- \* From [PSPICE NETLIST] section of C:\Program Files\OrcadLite\PSpice\PSpice.ini file:

- .lib "nom.lib"

- \*Analysis directives:

- .TRAN 0 20ms 0

- .PROBE V(\*) I(\*) W(\*) D(\*) NOISE(\*)

- .INC ".\example2-SCHEMATIC1.net"

\*\*\*\* INCLUDING example2-SCHEMATIC1.net \*\*\*\*

\* source EXAMPLE2

Lecture 6 6 - 7

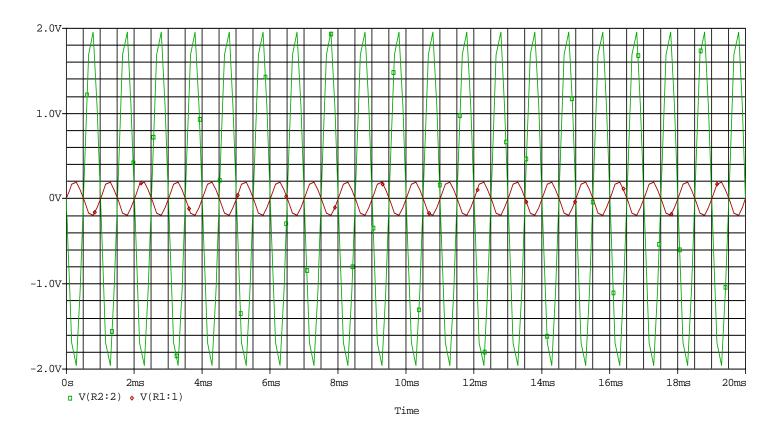

## PSPICE EXAMPLE (Cont'd)

E\_U1 N00043 0 VALUE {LIMIT(V(0, N00136)\*1E6, -15V, +15V)}

R\_R2 N00136 N00043 10k

R\_R1 N00248 N00136 1k

V\_V1 N00248 0

+SIN 0 0.2 1k 0 0 0

\*\*\*\* RESUMING example2-SCHEMATIC1-Example2Profile.sim.cir \*\*\*\*

.END

Lecture 6 6 - 8