## Lecture #10

# From Chapter 3 in Jaeger, Chapter 2 in Spencer

10 - 1

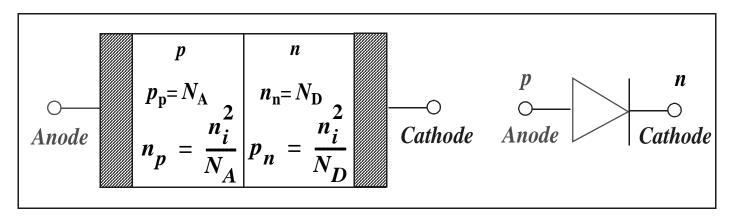

### **Diodes Basics**

#### **Outline/Learning Objectives:**

- pn junction electrostatics

- Mathematical model of the pn junction

- pn junction capacitance

#### **Selected Problems**

3.31, 3.70, 3.71, 3.78, 3.127, 3.129

#### **How the Diode Works**

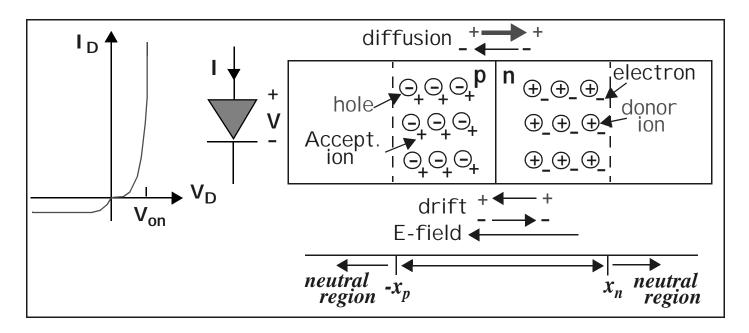

Explain space charge region (SCR) near to metallurgical junction which is depleted of mobile carriers (depletion layer or depletion region).

Lecture 10 10 - 2

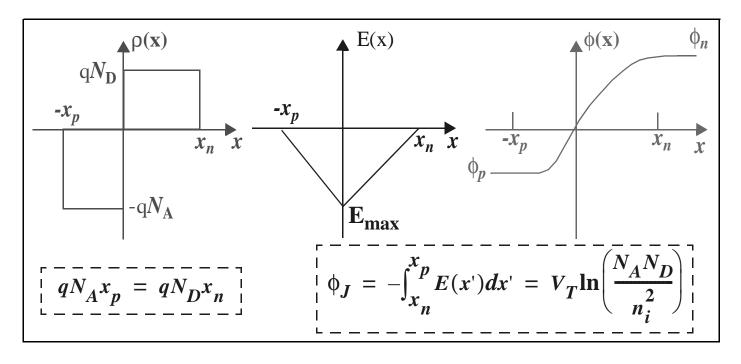

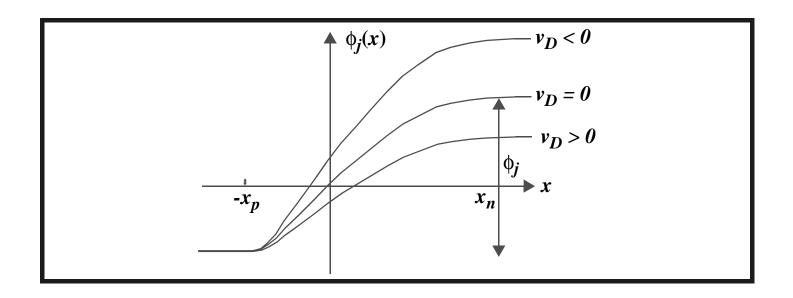

### pn junction electrostatics

Gauss' Law -

$$\nabla \cdot E = \frac{\rho_c}{\varepsilon_s}$$

, so in 1D, we get  $E(x) = \frac{1}{\varepsilon_s} \int \rho(x) dx$ .

Total depletion layer width is  $w_{do} = x_n + x_p = \sqrt{\frac{2\varepsilon_s}{q}} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) \phi_J$

Majority carriers - holes in p-region and electrons in n-region.

Holes diffuse from p to n and recombine with many of the free electrons there in **n-type** material. Leaves uncovered bound negative charges in L of junction (acceptor ions).

Electrons diffuse from n to p and recombine with many of the free holes there in p-type material. Leaves uncovered bound positive charges in R of junction (donor ions).

Diffusion of majority carriers leaves uncovered bound charges in space charge region (SCR) and creates an internal electric field from R to L.

Under E-field, minority carriers drift across the junction.

$$E = \frac{1}{\varepsilon_{Si}} \int \rho dx \text{ since } E = -\frac{dV}{dx}.$$

Potential barrier or height act to oppose diffusion of majority carriers - h (L --> R) and e (R --> L) and encourage drift of minority carriers.

Under OC conditions, net current is zero. Tendency of majority carriers to diffuse is just balanced by minority carriers to drift across junction.

Lecture 10 10 - 5

### **Example**

$$N_A = 10^{18} cm^{-3}$$

;  $N_D = 10^{14} cm^{-3}$ ;  $n_i = 10^{10} cm^{-3}$ ;

$$T = 300K$$

;  $\varepsilon_s = 11.7 \times 8.854 \times 10^{-14} \frac{F}{cm}$ ;  $\phi_J = 0.7V$ ;  $V_T = 0.0258V$ .

$$x_n = \sqrt{\frac{2\varepsilon_s}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) \phi_J} \cdot \frac{N_A}{N_A + N_D} = 3.03 \mu m$$

$$x_p = \sqrt{\frac{2\varepsilon_s}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) \phi_J} \cdot \frac{N_D}{N_A + N_D} = 3.03 \times 10^{-4} \mu m$$

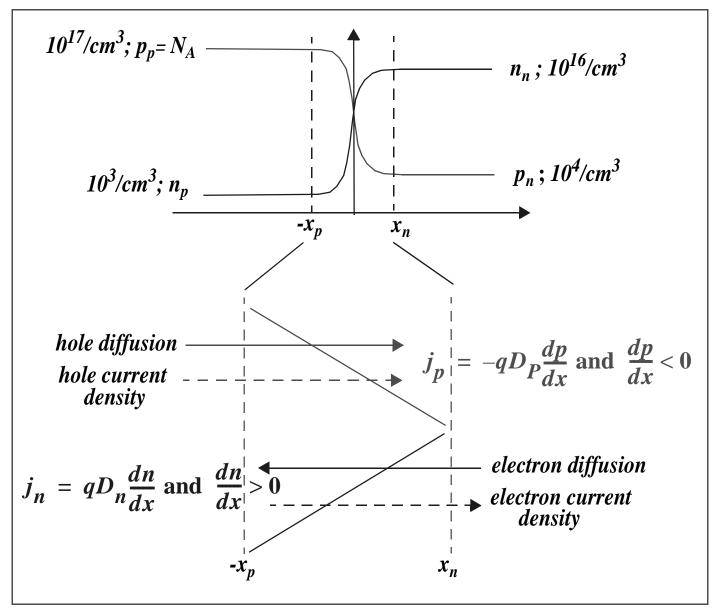

$$\boxed{j_n^T = \left(qn\mu_n E + qD_n \frac{\partial n}{\partial x}\right)} \text{ and } \boxed{j_p^T = qp\mu_p E - qD_p \frac{\partial p}{\partial x}} \text{ in A/cm}^2.$$

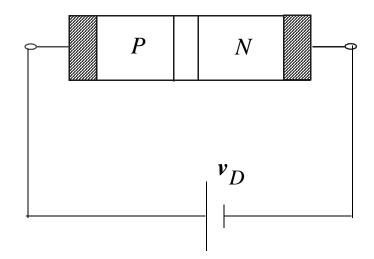

# The Diode behavior under applied voltage

#### Mathematical Model of the Diode

$$i_D = I_s \cdot \left(e^{qv_D/nkT} - 1\right)$$

Reverse saturation current  $(I_s)$

is independent of the junction potential.

$I_s$  doubles for every 10° increase

in temperature, near room temperature.

$$n$$

- ideality factor (1 to 2)  $q$  - electron charge  $(1.6x10^{-19}C)$

$$v_D$$

- diode voltage

$$v_D$$

- diode voltage  $k$  - Boltzmann constant  $\left(1.38x10^{-23}\frac{J}{K}\right)$

Reverse biases:

$$i_D \approx -I_s$$

for  $v_D \ll \frac{nkT}{q} = nV_T$ . Zero V:  $i_D = 0$ . Forward biases:  $i_D = I_s \cdot e$  for  $v_D \gg nV_T$ . (usually  $4V_T \approx 0.1V$ )

$$i_D = I_s \cdot e^{qv_D / nkT}$$

for  $v_D \gg nV_T$ . (usually  $4V_T \approx 0.1V$ )

### PN Junction Capacitance

Reverse Bias

$$Q_n = qN_Dx_nA = q\left(\frac{N_AN_D}{N_A + N_D}\right)w_dA$$

$$w_d = x_n + x_p = \sqrt{\frac{2\varepsilon_s}{q} \left(\frac{1}{N_A} + \frac{1}{N_D}\right) (\phi_J + v_R)}$$

$$C_{J} = \frac{dQ_{n}}{dv_{R}} = \left(\frac{\varepsilon_{Si}A}{w_{d0}}\right) \frac{1}{\sqrt{1 + v_{R}/\phi_{J}}}$$

Can be a V-controlled Capacitor (varactor)

Forward Bias  $Q_D = i_D \tau_T$  where  $\tau_T$  is the diode's transit time (1 fs to > 1  $\mu$ s - depends on type and size of diode).

Diffusion capacitance

$$C_D = \frac{dQ_D}{dv_D} = \frac{i_D \tau_T}{V_T}$$

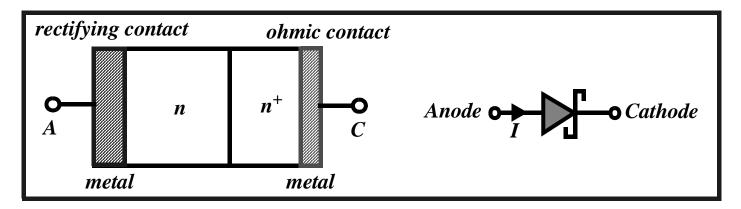

#### Schottky Barrier Diode

Characteristics - lower  $V_{on}$ .

- significantly reduced charge at  $v_{I\!\!P}$

- used in bipolar logic circuits.