## SOLUTIONS FOR EMERGING PROBLEMS IN MODULAR SYSTEM-ON-A-CHIP TESTING

## SOLUTIONS FOR EMERGING PROBLEMS IN MODULAR SYSTEM-ON-A-CHIP TESTING

BY QIANG XU AUGUST 2005

A THESIS SUBMITTED TO THE DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF MCMASTER UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

> © Copyright 2005 by Qiang Xu All Rights Reserved

### DOCTOR OF PHILOSOPHY (2005) (Electrical and Computer Engineering)

McMaster University Hamilton, Ontario

| TITLE:      | Solutions for Emerging Problems in Modular System-on-a-<br>Chip Testing |

|-------------|-------------------------------------------------------------------------|

| AUTHOR:     | Qiang Xu                                                                |

| SUPERVISOR: | Nicola Nicolici                                                         |

|             |                                                                         |

NUMBER OF PAGES: xvii, 211

### Acknowledgments

Finally the long journey has come to the end, and I am really glad that I have now the opportunity to express my gratitude for all the people who have made this thesis possible.

The first person I would like to thank is my supervisor, Nicola Nicolici, whose encouragement, enthusiasm to high-quality work and motivating discussions helped me in all the time of research for and writing of this thesis. In particular, I am deeply grateful to the support and freedom he gave me on my summer travel. It was a great pleasure to me to conduct this thesis under his supervision.

Needless to say, I am grateful to all of my colleagues in the computer-aided design and test research group at McMaster University, Bai Hong Fang, Henry Ko, David Lemstra, Adam Kinsman, David Leung and Ehab Anis, those with whom I have shared both happiness and sadness as a graduate student. I also would like to thank Theo Gonciari and Paul Rosinger from University of Southampton. In particular, I would like to express my appreciation to Theo Gonciari for his early work and insightful comments on this thesis. Krishnendu Chakrabarty from Duke University also provided constructive suggestions on this thesis and I am deeply indebted to him. Many thanks also go to the faculty, administrative and technical members in Department of Electrical and Computer Engineering at McMaster University, whose assistance was vital for the research. In particular, I would like to express my gratitude to Cheryl Gies, who is of great help whenever needed.

My father Zhiqing Xu, my mother Qinghua Zhang, my wife Yujie Cui and my sister Dongdong Xu have loved, trusted and supported me all the time in my life. I cannot live through this Ph.D period without their love and patience. Words cannot express my love and gratitude to my family.

## Abstract

Manufacturing test has established itself as an enabling technology for the system-on-achip (SOC) design paradigm. Although the IEEE Std. 1500 for embedded core test and prior work on test access mechanism design ease the SOC testing process, there are several emerging problems not treated explicitly or cost-effectively by the state-of-the-art methods. For example, the number of clock domains is stepping-up and the specific test access and isolation problems posed by multi-frequency cores have not been treated explicitly; detection of timing failures, which are predominant in deep sub-micron technologies, requires support from the test access architectures for at-speed application of two successive patterns; glue logic defined by system integrators for product differentiation is increasing in size and its test can adversely influence either the chip area or testing time; the continuous growth in the size of SOCs leads to multiple levels of design hierarchy, which imposes an additional constraint on the design and reuse of test architectures.

This dissertation shows how at-speed test application, without test hazards, can be achieved for cores with multiple clock domains, by embedding small custom logic in the wrapper. It also introduces novel test architectures for SOCs containing unwrapped logic blocks without any loss in fault coverage, by combining dedicated bus-based test access mechanism and functional interconnects for test data transfer. With some minor changes, this new test architecture can be utilized to effectively apply two-pattern test for core-based SOCs, which is essential for detecting delay faults and CMOS stuck-open faults. Test access mechanism design algorithms for the new SOC test architectures are also proposed and design trade-offs between test area and testing time are discussed. Finally, this dissertation presents a new framework for the design space exploration of multi-level test access mechanisms, which is important for future hierarchical SOCs that reuse past-generation SOCs with existing test infrastructure as internal mega-cores.

# **List of Abbreviations**

| ATE   | Automatic Test Equipment                 |

|-------|------------------------------------------|

| ATPG  | Automatic Test Pattern Generation        |

| BIST  | Built-In Self-Test                       |

| CMOS  | Complementary Metal Oxide Silicon        |

| CTL   | Core Test Language                       |

| CUT   | Core under Test                          |

| DFT   | Design for Testability                   |

| FF    | Flip-Flop                                |

| FIFO  | First-In First-Out                       |

| FSM   | Finite State Machine                     |

| HDL   | Hardware Description Language            |

| I/O   | Input/Output                             |

| IC    | Integrated Circuit                       |

| ILP   | Integer Linear Programming               |

| IP    | Intellectual Property                    |

| ITRS  | International Roadmap for Semiconductors |

| LFSR  | Linear Feedback Shift Register           |

| LSSD  | Level-Sensitive Scan Design              |

| MFCW  | Multi-Frequency Core Wrapper             |

| MISR  | Multiple Input Signature Analyzer        |

| NC-PI | Non-Controlled Primary Inputs            |

| PC-PI | Parallelly-Controlled Primary Inputs     |

|       |                                          |

| DCD     | Drinted Cinquit Decard                          |

|---------|-------------------------------------------------|

| PCB     | Printed Circuit Board                           |

| PI      | Primary Input                                   |

| PLL     | Phase-Locked Loop                               |

| PO      | Primary Output                                  |

| PSI     | Pseudo-Input                                    |

| PSO     | Pseudo-Output                                   |

| RAM     | Random Access Memory                            |

| SA      | Signature Analyzer                              |

| SC-PI   | Serially-Controlled Primary Inputs              |

| SECT    | Standard for Embedded Core Test                 |

| SFCW    | Single-Frequency Core Wrapper                   |

| SFF     | Scanned Flip-Flop                               |

| SOC     | System-on-a-Chip                                |

| TAM     | Test Access Mechanism                           |

| TAT     | Test Application Time                           |

| TDC     | Test Data Compression                           |

| TPG     | Test pattern generator                          |

| UDL     | User Defined Logic                              |

| VC      | Virtual Core                                    |

| VLSI    | Very Large Scale Integration                    |

| VTB     | Virtual Test Bus                                |

| VTB-DIU | Virtual Test Bus De-Multiplexing Interface Unit |

| VTB-MIU | Virtual Test Bus Multiplexing Interface Unit    |

| WBR     | Wrapper Boundary Register                       |

| WBY     | Wrapper Bypass Register                         |

| WIC     | Wrapper Input Cell                              |

| WIR     | Wrapper Instruction Register                    |

| WOC     | Wrapper Output Cell                             |

| WPI     | Wrapper Parallel Input                          |

| WPO     | Wrapper Parallel Output                         |

|         | ** *                                            |

| WSC        | Wrapper Serial Control |

|------------|------------------------|

| WSI        | Wrapper Serial Input   |

| WSO        | Wrapper Serial Output  |

| Wrapper SC | Wrapper Scan Chain     |

# Contents

| Acknowledgments iii |                                                                                                             |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ostrac              | et                                                                                                          |                                                                                                                                                                                                                                                                                                 | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| st of A             | Abbrevi                                                                                                     | ations                                                                                                                                                                                                                                                                                          | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Intr                | oductio                                                                                                     | n                                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.1                 | Core-I                                                                                                      | Based SOC Design                                                                                                                                                                                                                                                                                | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.2                 | Thesis                                                                                                      | Motivation                                                                                                                                                                                                                                                                                      | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.3                 | Thesis                                                                                                      | Organization and Contributions                                                                                                                                                                                                                                                                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Bac                 | kgroun                                                                                                      | d                                                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2.1                 | VLSI                                                                                                        | Testing Concepts                                                                                                                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                     | 2.1.1                                                                                                       | Defect vs. Fault Modeling                                                                                                                                                                                                                                                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 2.1.2                                                                                                       | Test Pattern Generation                                                                                                                                                                                                                                                                         | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 2.1.3                                                                                                       | Design for Testability (DFT)                                                                                                                                                                                                                                                                    | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 2.1.4                                                                                                       | Cost of Test                                                                                                                                                                                                                                                                                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.2                 | Scan I                                                                                                      | Design with Multiple Clock Domains                                                                                                                                                                                                                                                              | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 2.2.1                                                                                                       | Avoiding Clock Skew during Scan Shift                                                                                                                                                                                                                                                           | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 2.2.2                                                                                                       | Avoiding Clock Skew during Scan Capture                                                                                                                                                                                                                                                         | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.3                 | Delay                                                                                                       | Fault Testing Strategies                                                                                                                                                                                                                                                                        | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 2.4                 | Conclu                                                                                                      | uding Remarks                                                                                                                                                                                                                                                                                   | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                     | 2.2<br><b>Distraction</b><br><b>St of</b> <i>A</i><br><b>Intr</b><br>1.1<br>1.2<br>1.3<br><b>Bac</b><br>2.1 | St of Abbrevi         Introductio         1.1       Core-H         1.2       Thesis         1.3       Thesis         Background       2.1         2.1       VLSI         2.1.1       2.1.2         2.1.3       2.1.4         2.2       Scan H         2.2.1       2.2.2         2.3       Delay | st of Abbreviations         Introduction         1.1       Core-Based SOC Design         1.2       Thesis Motivation         1.3       Thesis Organization and Contributions         1.3       Thesis Organization and Contributions         Background         2.1       VLSI Testing Concepts         2.1.1       Defect vs. Fault Modeling         2.1.2       Test Pattern Generation         2.1.3       Design for Testability (DFT)         2.1.4       Cost of Test         2.2       Scan Design with Multiple Clock Domains         2.2.1       Avoiding Clock Skew during Scan Shift         2.2.2       Avoiding Clock Skew during Scan Capture |

| 3 | Prev | vious Work                                                       | 26 |

|---|------|------------------------------------------------------------------|----|

|   | 3.1  | IEEE Std. 1500                                                   | 27 |

|   |      | 3.1.1 Scalable Core Test Wrapper                                 | 27 |

|   |      | 3.1.2 Wrapper Instruction Set                                    | 30 |

|   |      | 3.1.3 Core Test Language (CTL)                                   | 31 |

|   | 3.2  | SOC Test Access                                                  | 32 |

|   |      | 3.2.1 Direct Access                                              | 32 |

|   |      | 3.2.2 Isolation Ring Access                                      | 33 |

|   |      | 3.2.3 Functional Access                                          | 34 |

|   |      | 3.2.4 Dedicated Bus-Based Access                                 | 36 |

|   |      | 3.2.5 Cost Analysis for Different SOC Test Access Strategies     | 38 |

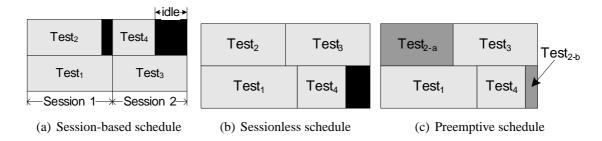

|   | 3.3  | Test Scheduling and Test Architecture Optimization               | 40 |

|   |      | 3.3.1 Test Scheduling                                            | 42 |

|   |      | 3.3.2 Wrapper Design and Optimization                            | 44 |

|   |      | 3.3.3 Integrated Wrapper/TAM Co-Optimization and Test Scheduling | 45 |

|   | 3.4  | SOC Test Resource Partitioning                                   | 52 |

|   |      | 3.4.1 Test Stimuli Compression                                   | 53 |

|   |      | 3.4.2 Test Response Compaction                                   | 55 |

|   | 3.5  | Concluding Remarks                                               | 56 |

| 4 | Wra  | apper Design for Multi-Frequency IP Cores                        | 57 |

|   | 4.1  | Preliminaries and Summary of Contributions                       | 57 |

|   | 4.2  | Multi-Frequency Core Wrapper Design                              | 61 |

|   | 4.3  | Multi-Frequency Core Wrapper Optimization                        |    |

|   |      | 4.3.1 Wrapper Optimization Using an ILP Model                    | 69 |

|   |      | 4.3.2 Wrapper Optimization Using Fast Heuristics                 | 71 |

|   | 4.4  | Experimental Results                                             | 75 |

|   | 4.5  | Concluding Remarks                                               | 78 |

| 5 | Two  | o-Pattern Test of Core-Based SOCs                                | 79 |

|   | 5.1  | Preliminaries and Summary of Contributions                       | 80 |

|   | 5.2  | Proposed Architecture for Two-Pattern Test                       | 85 |

|   |     | 5.2.1    | The Two-Pattern Testing Process                                 | . 85  |

|---|-----|----------|-----------------------------------------------------------------|-------|

|   |     | 5.2.2    | 1500-Compatible Core Wrapper Design for Two-Pattern Test        | . 87  |

|   | 5.3 | Propos   | sed Architecture Optimization                                   | . 88  |

|   |     | 5.3.1    | Test Conflicts                                                  | . 88  |

|   |     | 5.3.2    | TAM Division into Producer and CUT Groups                       | . 89  |

|   |     | 5.3.3    | Two-Pattern Test Scheduling                                     | . 90  |

|   | 5.4 | Experi   | mental Results                                                  | . 95  |

|   |     | 5.4.1    | SOC Specifications                                              | . 96  |

|   |     | 5.4.2    | Experiment 1: DFT Area Savings                                  | . 96  |

|   |     | 5.4.3    | Experiment 2: Optimal Producer-CUT TAM Configuration            | . 97  |

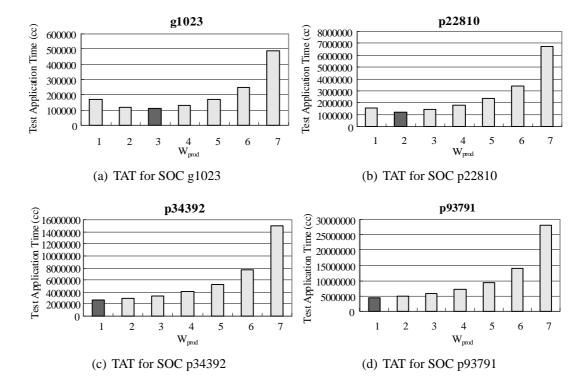

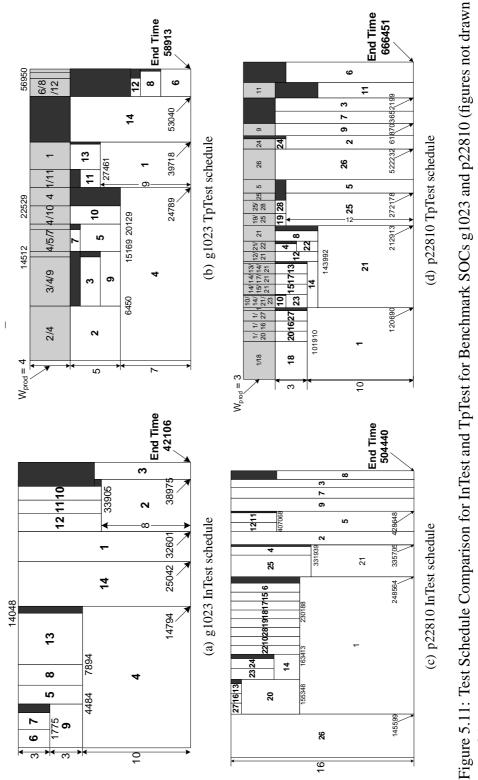

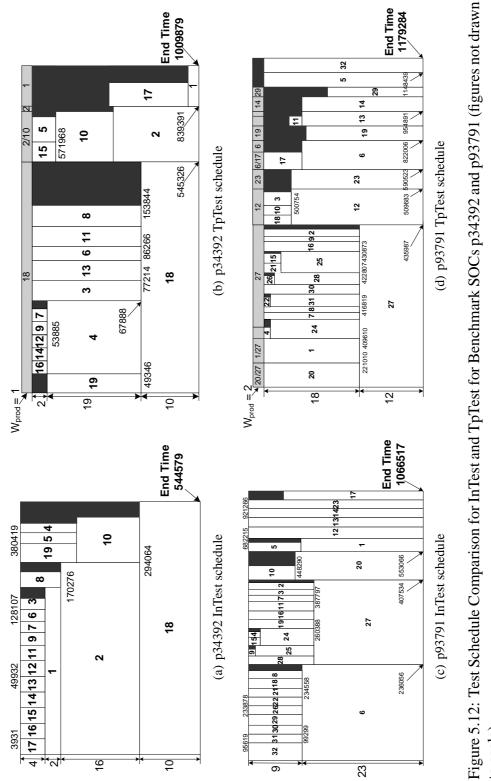

|   |     | 5.4.4    | Experiment 3: Test Schedule and Test Application Time           | . 98  |

|   | 5.5 | Conclu   | Iding Remarks                                                   | . 101 |

| 6 | Mod | lular S( | DC Testing with Reduced Wrapper Count                           | 104   |

|   | 6.1 |          | inaries and Summary of Contributions                            |       |

|   |     | 6.1.1    | Light Wrapper                                                   |       |

|   |     | 6.1.2    | Summary of Contributions                                        |       |

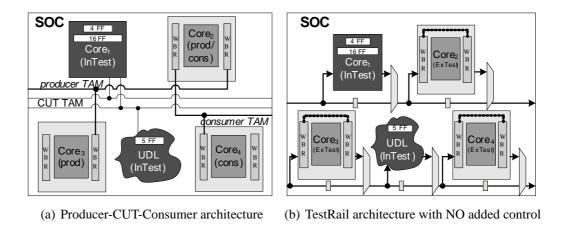

|   | 6.2 | Produc   | cer-CUT-Consumer Architecture for Testing Light-Wrapped Cores . |       |

|   |     | 6.2.1    | Test Conflicts Caused by Sharing Producers/Consumers            |       |

|   |     | 6.2.2    | TAM Division into Three Groups: Producer, CUT and Consumer      |       |

|   |     | 6.2.3    | Proposed Algorithms for Wrapper/TAM Co-Optimization             |       |

|   | 6.3 | Adapti   | ing the TestRail Architecture for Testing Light-Wrapped Cores   |       |

|   |     | 6.3.1    | Determine the TestRail Architecture                             |       |

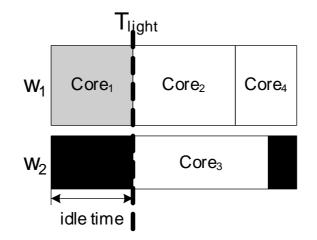

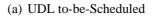

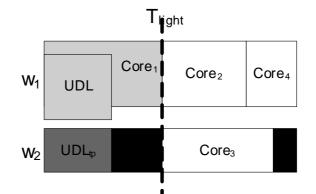

|   |     | 6.3.2    | Schedule Light-Wrapped Cores                                    |       |

|   |     | 6.3.3    |                                                                 |       |

|   |     | 6.3.4    | ReSchedule Wrapped Cores in between Different TestRails         |       |

|   | 6.4 |          | mental Results                                                  |       |

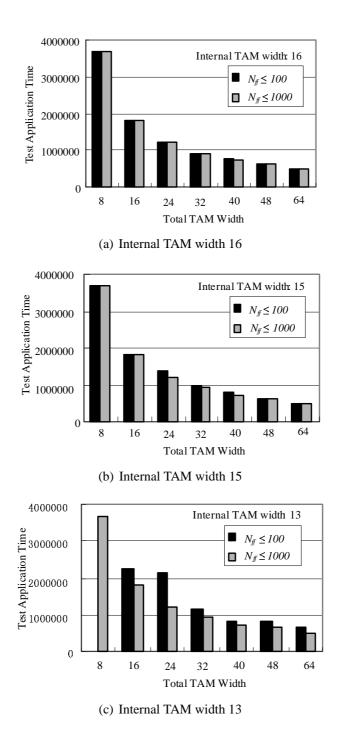

|   |     | 6.4.1    | Experiment 1: Test Schedule Comparison for m4953                |       |

|   |     | 6.4.2    | Experiment 2: Reduction in 1500-Wrappers and WBRs               |       |

|   |     | 6.4.3    | Experiment 3: Testing Time for Producer-CUT-Consumer Archi-     | 0     |

|   |     |          | tecture                                                         | . 141 |

|   |     |          |                                                                 |       |

|    |       | 6.4.4    | Experiment 4: Testing Time for Adapted TestRail Architecture | . 144 |

|----|-------|----------|--------------------------------------------------------------|-------|

|    | 6.5   | Conclu   | Iding Remarks                                                | . 149 |

| 7  | Mul   | ti-Frequ | uency TAM Design for Hierarchical SOCs                       | 150   |

|    | 7.1   | Prelim   | inaries and Summary of Contributions                         | . 151 |

|    |       | 7.1.1    | Related Work on Multi-Frequency TAM Design                   | . 152 |

|    |       | 7.1.2    | Related Work on Hierarchical SOC Testing                     | . 153 |

|    |       | 7.1.3    | Summary of Contributions                                     | . 154 |

|    | 7.2   | Multi-   | Frequency TAM Design for Flattened SOCs                      | . 155 |

|    |       | 7.2.1    | Multi-Frequency Test Architecture                            | . 155 |

|    |       | 7.2.2    | Multi-Frequency TAM Design Algorithm                         | . 158 |

|    |       | 7.2.3    | A Case Study for Benchmark SOC p22810                        | . 162 |

|    | 7.3   | Multi-   | Frequency TAM Design for Hierarchical SOCs                   | . 164 |

|    |       | 7.3.1    | Matching the Bandwidth for Hard Mega-Cores                   | . 164 |

|    |       | 7.3.2    | Design Flow for System Integrator                            | . 168 |

|    |       | 7.3.3    | A Case Study for Benchmark SOC p93791                        | . 171 |

|    | 7.4   | Experi   | mental Results                                               | . 173 |

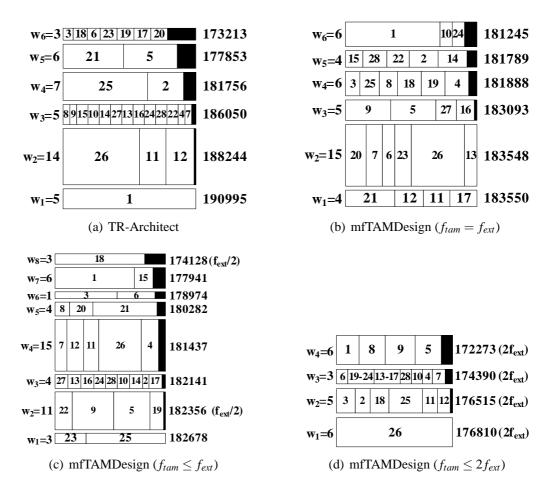

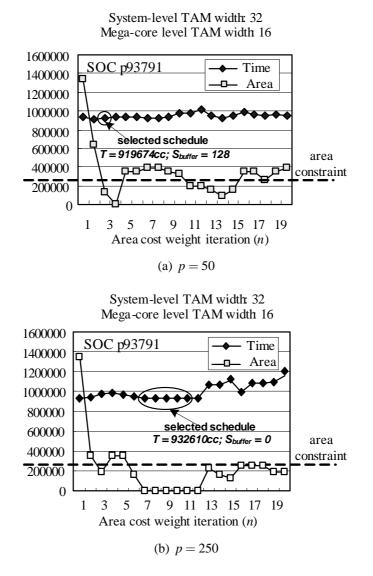

|    |       | 7.4.1    | Experiment 1: Testing Time for Flattened SOCs                | . 173 |

|    |       | 7.4.2    | Experiment 2: Testing Time for Hierarchical SOCs             | . 178 |

|    | 7.5   | Conclu   | Iding Remarks                                                | . 185 |

| 8  | Con   | clusion  |                                                              | 186   |

| Bi | bliog | raphy    |                                                              | 189   |

# **List of Tables**

| 3.1 | Test Cost Comparison for Different Access Strategies                           |

|-----|--------------------------------------------------------------------------------|

| 4.1 | hCADT01 Clock Domain Information                                               |

| 4.2 | Test Application Time and Number of VTB lines for hCADT01 with Dif-            |

|     | ferent TAM Width under Various Power Constraints                               |

| 5.1 | TAT Comparison of The Two Two-Pattern Test Methodologies for g1023. 99         |

| 5.2 | TAT Comparison of The Two Two-Pattern Test Methodologies for p22810. 99        |

| 5.3 | TAT Comparison of The Two Two-Pattern Test Methodologies for p34392. 100       |

| 5.4 | TAT Comparison of The Two Two-Pattern Test Methodologies for p93791. 101       |

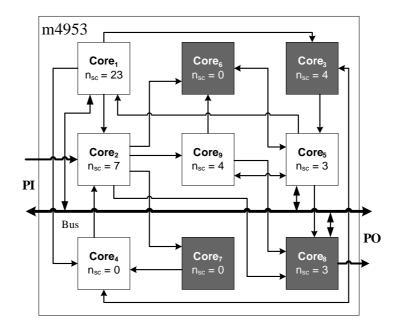

| 6.1 | Test Parameters of SOC m4953                                                   |

| 6.2 | The Number of Light-Wrapped Cores for Benchmark SOCs                           |

| 6.3 | Test Application Time Comparison for g1023                                     |

| 6.4 | Test Application Time Comparison for p34392                                    |

| 6.5 | Test Application Time Comparison for p93791                                    |

| 6.6 | Test Application Time Comparison for t512505                                   |

| 6.7 | TAT Comparison between The Two Proposed Test Architectures for p34392          |

|     | with Different Light-Wrapped Core Configurations                               |

| 6.8 | TAT Comparison between The Two Proposed Test Architectures for p93791          |

|     | with Different Light-Wrapped Core Configurations                               |

| 7.1 | TAT Comparison for TestRail Architecture with Fixed-Length Scan Chains. 174    |

| 7.2 | TAT Comparison for Test Bus architecture with Fixed-Length Scan Chains. 175    |

| 7.3 | TAT Comparison for TestRail Architecture with Flexible-Length Scan Chains. 176 |

- 7.4 TAT Comparison for Test Bus architecture with Flexible-Length Scan Chains. 176

- 7.5 Test Application Time for Hierarchical SOCs p22810 and a586710. . . . . 181

- 7.6 Test Application Time for Hierarchical SOCs p34392 and p93791. . . . . . 182

# **List of Figures**

| 1.1  | General Architecture of Core-Based System-on-a-Chip                        | 2  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Design Development Variations between Board and Chip [180]                 | 4  |

| 2.1  | Principle of VLSI Testing.                                                 | 10 |

| 2.2  | Commonly Used Fault Models: (a) Stuck-at Fault; (b)Delay Fault             | 11 |

| 2.3  | A Single Scan Chain Design Schematic.                                      | 15 |

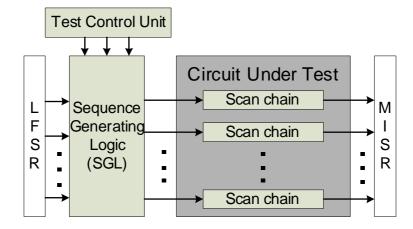

| 2.4  | Conceptual BIST Design Scheme.                                             | 16 |

| 2.5  | Scan-Based BIST Architecture                                               | 17 |

| 2.6  | Hazard of Clock Skew during Scan Shift.                                    | 20 |

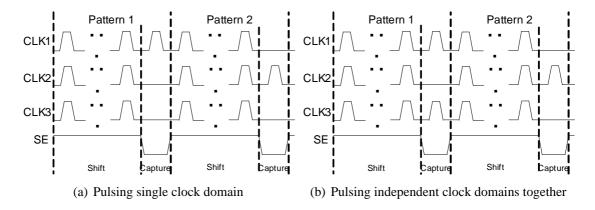

| 2.7  | Timing Diagram for Multi-Frequency Design with Combinational ATPG          |    |

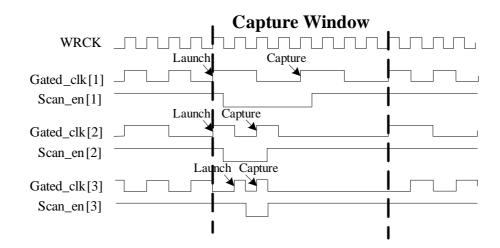

|      | Help                                                                       | 21 |

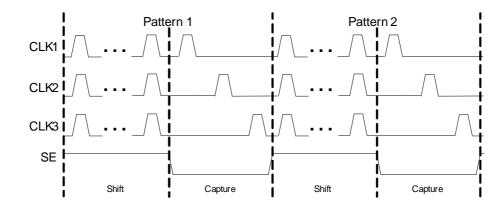

| 2.8  | Timing Diagram for Multi-Frequency Design with Sequential ATPG Help        | 22 |

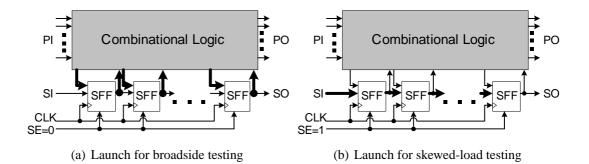

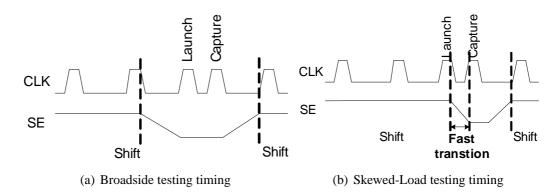

| 2.9  | Data Flow of Launch Pattern for Broadside Testing vs. Skewed-Load Testing. | 24 |

| 2.10 | Timing Diagrams of Broadside Testing vs. Skewed-Load Testing               | 24 |

| 3.1  | Conceptual Infrastructure for SOC Testing [180]                            | 27 |

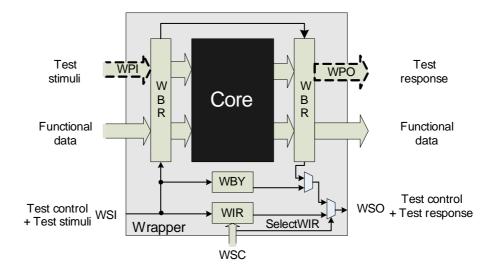

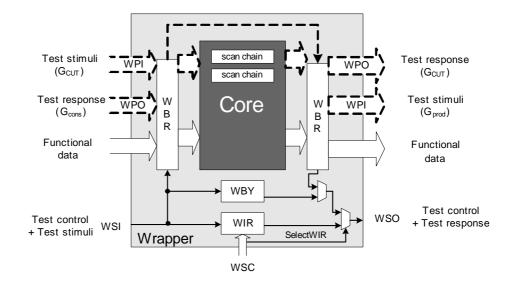

| 3.2  | IEEE 1500 Wrapper Architecture [117]                                       | 28 |

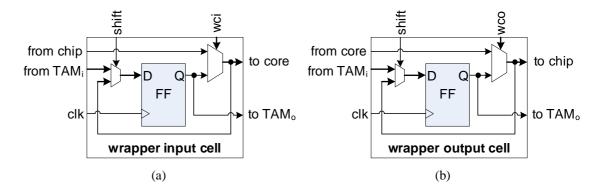

| 3.3  | Wrapper Cell Design for (a) Core Input and (b) Core Output Terminal [117]. | 29 |

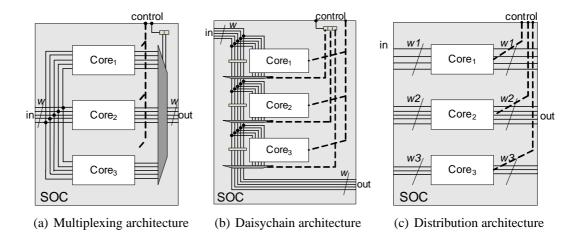

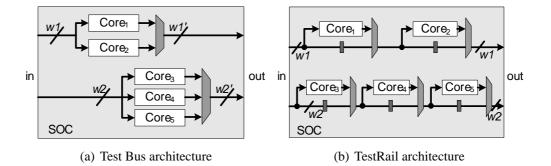

| 3.4  | Three Basic Scan-Based SOC Test Architectures ([2]).                       | 37 |

| 3.5  | Test Bus and TestRail Architectures.                                       | 38 |

| 3.6  | Test Scheduling Technique Categorization.                                  | 42 |

| 3.7  | TAM Bus Categorization.                                                    | 46 |

| 3.8  | Conceptual Infrastructure for SOC Testing with Test Data Compression       | 53 |

| 4.1  | An Example Multi-Frequency SOC.                                                      | 58 |

|------|--------------------------------------------------------------------------------------|----|

| 4.2  | Single/Multiple Frequency Cores.                                                     | 62 |

| 4.3  | An Example Multi-Frequency Core Wrapper.                                             | 63 |

| 4.4  | At-Speed Multi-Frequency Testing Timing Diagram with a Single Physical               |    |

|      | Clock                                                                                | 64 |

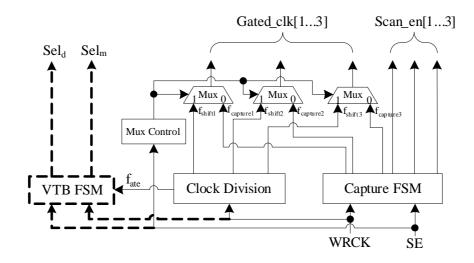

| 4.5  | Block Diagram of Scan Control Block                                                  | 66 |

| 4.6  | Timing Diagram for At-speed Multi-Frequency Testing with Multiple Phys-              |    |

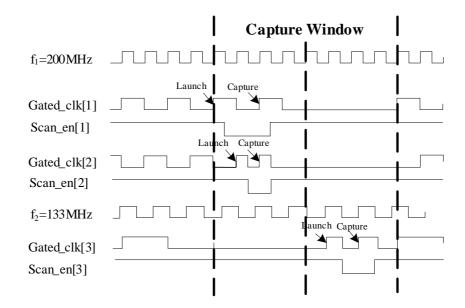

|      | ical Clocks.                                                                         | 67 |

| 4.7  | Pseudocode for Multi-Frequency Wrapper Design.                                       | 72 |

| 4.8  | Procedure for Assigning VTB Lines to the Bottleneck Virtual Core                     | 73 |

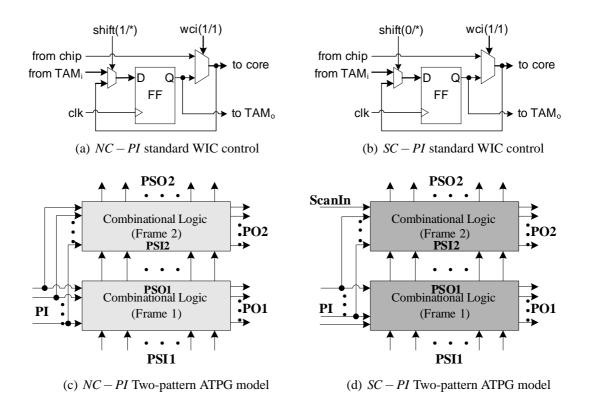

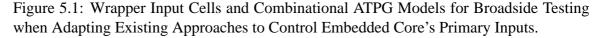

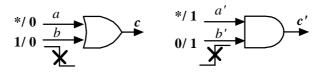

| 5.1  | Wrapper Input Cells and Combinational ATPG Models for Broadside Test-                |    |

|      | ing when Adapting Existing Approaches to Control Embedded Core's Pri-                |    |

|      | mary Inputs                                                                          | 81 |

| 5.2  | Fault Coverage Loss with $NC - PI$ and $SC - PI$ ATPG Model                          | 83 |

| 5.3  | PC-PI ATPG Model and The Two Corresponding Wrapper Input Cell De-                    |    |

|      | signs                                                                                | 84 |

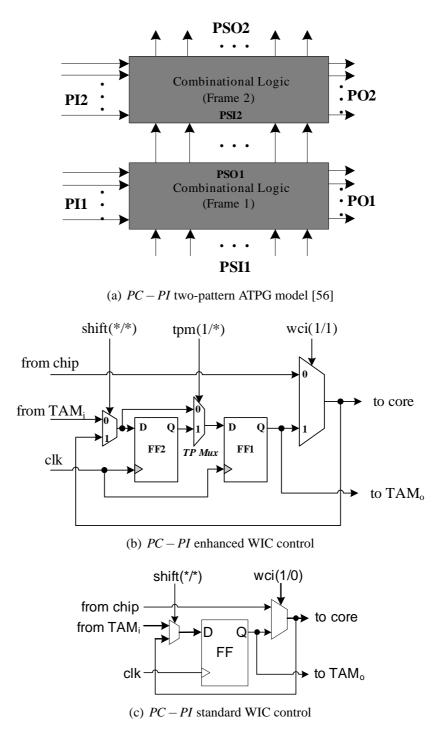

| 5.4  | Proposed Producer-CUT Architecture for SOC Two-Pattern Test                          | 86 |

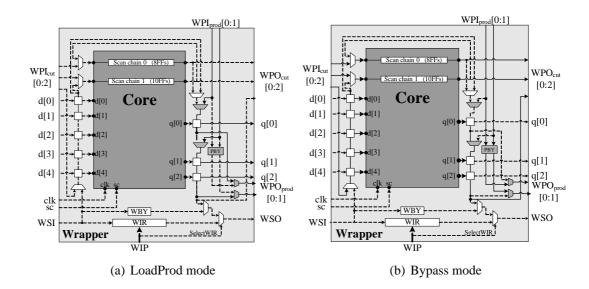

| 5.5  | An Example Producer Core in LoadProd and Bypass Modes                                | 87 |

| 5.6  | Test Conflicts for Multiple Cores on The Same Functional Bus                         | 89 |

| 5.7  | Pseudocode for Optimizing SOC with Two-Pattern Tested Cores                          | 91 |

| 5.8  | Loading Time for Different Patterns $(L_{prod}/wsc_{in}/wsc_{out})$                  | 92 |

| 5.9  | Procedure for Test Scheduling with Given Widths for Each TAM Group                   | 94 |

| 5.10 | SOC TATs with Variable Producer-CUT TAM Width Configurations                         | 97 |

| 5.11 | Test Schedule Comparison for InTest and TpTest for Benchmark SOCs                    |    |

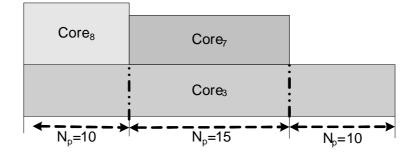

|      | g1023 and p22810 (figures not drawn to scale)                                        | 02 |

| 5.12 | Test Schedule Comparison for InTest and TpTest for Benchmark SOCs                    |    |

|      | p34392 and p93791 (figures not drawn to scale)                                       | 03 |

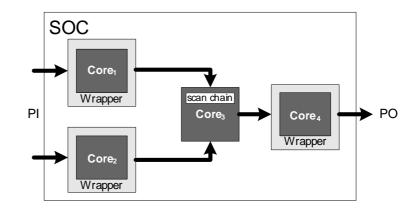

| 6.1  | Full Controllability and Observability for Core <sub>3</sub> without Wrapper Cells 1 | 06 |

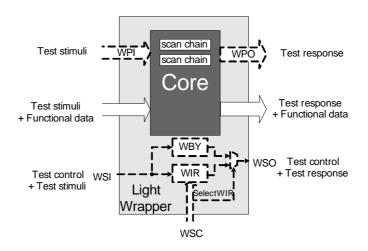

| 6.2  | Light Wrapper without Wrapper Cells                                                  | 07 |

| 6.3  | Revised IEEE 1500-Compliant Wrapper for Producer/Consumer Cores 1                    | 08 |

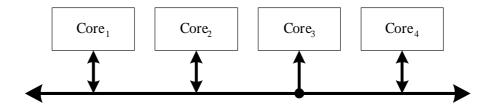

| 6.4  | Example SOC: m4953                                                            |

|------|-------------------------------------------------------------------------------|

| 6.5  | Proposed Test Architecture for an Example SOC Containing Light-Wrapped        |

|      | Cores                                                                         |

| 6.6  | Pseudocode for Optimizing Producer-CUT-Consumer Test Architecture 117         |

| 6.7  | Procedure for Deciding the Wrapper Type of Each Core                          |

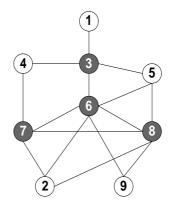

| 6.8  | Test Incompatibility Graph for SOC m4953                                      |

| 6.9  | Test Application Time for Light-Wrapped Cores                                 |

| 6.10 | Procedure for Test Scheduling with Given Widths of Each TAM Group 123         |

| 6.11 | Comparison of Test Architectures for SOCs with Light-Wrapped Cores -          |

|      | A Simple Example                                                              |

| 6.12 | Pseudocode for Optimizing TestRail Architecture with Light-Wrapped Cores. 126 |

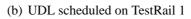

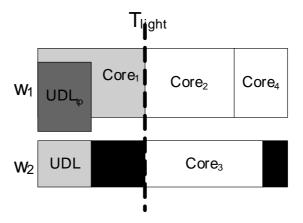

| 6.13 | Comparison of Scheduling UDLs on different TestRails                          |

| 6.14 | Procedure for Scheduling Light-Wrapped Cores onto TestRail Architecture 132   |

| 6.15 | Procedure for Rescheduling 1500-Wrapped Cores within TestRail 134             |

| 6.16 | Procedure for Rescheduling 1500-Wrapped Cores in between Different            |

|      | TestRails                                                                     |

| 6.17 | LightTRDesign Algorithm for an Example SOC with Five 1500-Wrapped             |

|      | Cores and Three Light-Wrapped Cores                                           |

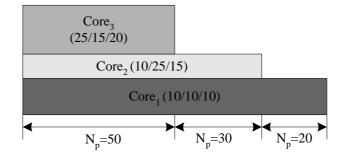

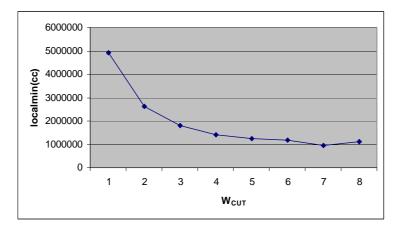

| 6.18 | Test Application Time Variation with $W_{CUT}$                                |

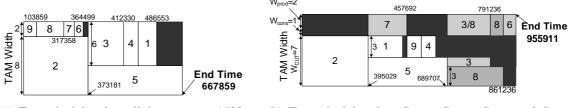

| 6.19 | Test Schedule Comparison for SOC m4953                                        |

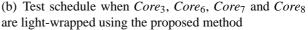

| 6.20 | Test Application Time Variation for p34392 with Different costweight 145      |

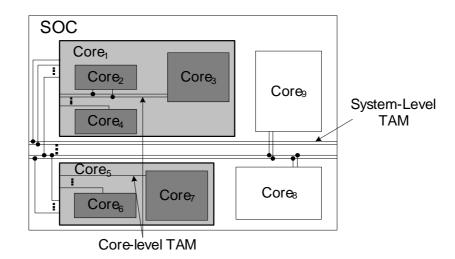

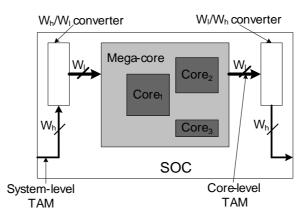

| 7.1  | Hierarchical SOC Example                                                      |

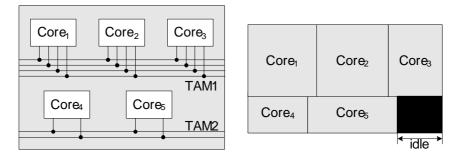

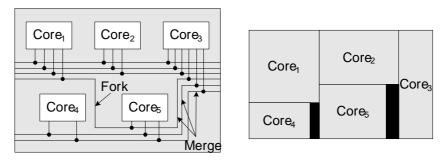

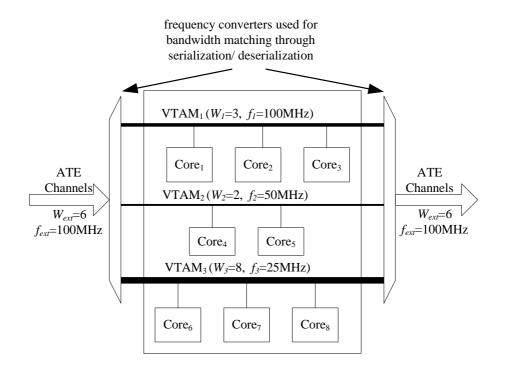

| 7.2  | Proposed Multi-Frequency Test Architecture for Flattened SOCs 156             |

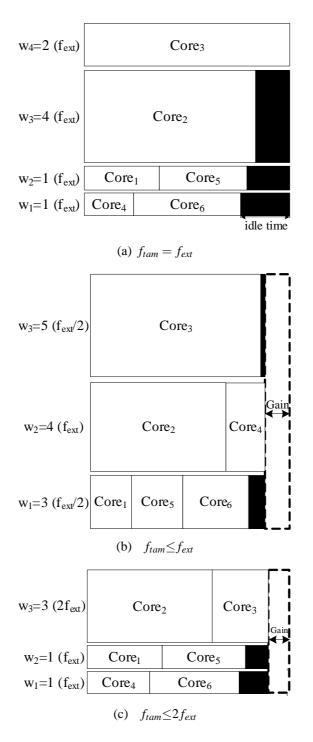

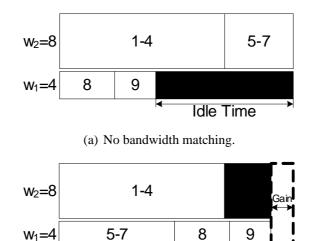

| 7.3  | The Benefits of Multi-Frequency TAM Design                                    |

| 7.4  | Pseudocode for SOC Test Architecture Optimization Using Multi-Frequency       |

|      | TAMs                                                                          |

| 7.5  | Procedure for Merging Multi-Frequency Virtual TAMs                            |

| 7.6  | Procedure for Distributing Freed Virtual TAM Lines                            |

| 7.7  | Comparison of TAM Design for Flattened SOC p22810 with $W_{ttl} = 40.$ 163    |

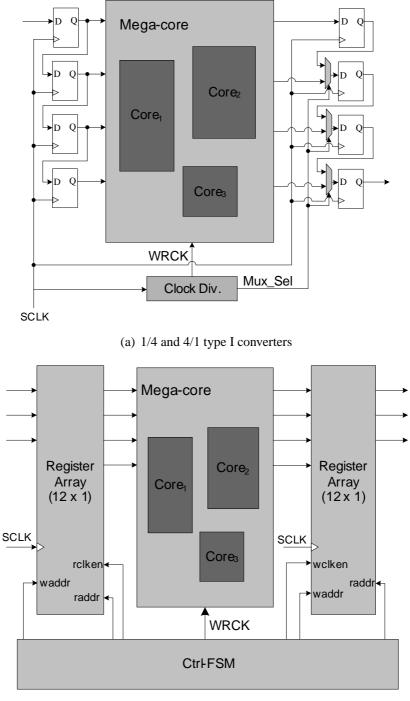

| 7.8  | Proposed Hardware Architecture for Testing Hard Mega-Cores                    |

|      |                                                                               |

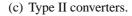

| 7.9  | Type I and II Frequency Converters Used for Bandwidth Matching 166            |

|------|-------------------------------------------------------------------------------|

| 7.10 | The Benefits of Multi-Frequency TAM Design for Hierarchical SOCs 167          |

| 7.11 | Design Flow for Testing SOCs with Multiple levels of Hierarchy 170            |

| 7.12 | Comparison of Multi-Level TAM Design for SOC p93791 with $W_{ttl} = 48$ . 172 |

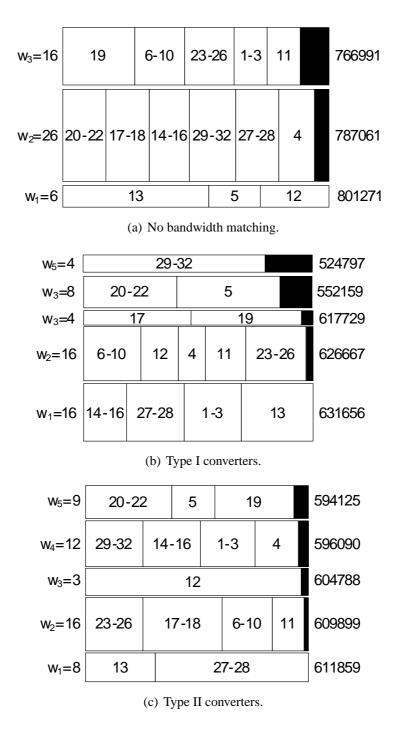

| 7.13 | Test Application Time and DFT area for p93791 with Different Area Cost        |

|      | Weights                                                                       |

| 7.14 | Test Application Time for p93791 with Different Internal TAM Widths. $184$    |

|      |                                                                               |

## Chapter 1

## Introduction

Semiconductor manufacturing technology has advanced significantly over the past several decades and continues to do so. The International Technology Roadmap for Semiconductors (ITRS) [69] projects that integrated circuits (ICs) with multi-billion transistors will be manufactured by the end of this decade, with feature sizes in the range of 50*nm* and clock frequencies in the range of 10*GHz*. In order to fully exploit the capabilities of the advanced process technologies and at the same time meet the shrinking product development schedules, the electronic industry is moving toward a design flow that integrates pre-designed and pre-verified cores into system-on-a-chip (SOC) platforms, based on the "reuse" philosophy [86]. Manufacturing test, a key step at the back end of the implementation flow of very large scale integrated (VLSI) circuits, used to isolate good chips from the defective ones, has become an essential technology that enables the fabrication yield, certifies the product quality and influences the final cost of the device [17].

Recently a vast body of research [171] has been endeavored to address the SOC testing challenges. Nevertheless, several emerging problems in SOC testing are not addressed and the known methods cannot be easily adapted to solve them in a cost-effective way due to their simplified assumptions. For example, embedded cores are considered to have only a single clock domain or design hierarchy is assumed to be flattened during test development. While these assumptions were valid in the past, they are becoming obsolete for state-of-the-art SOC designs. As a consequence, the topic of this dissertation is to tackle the emerging problems in modular SOC testing.

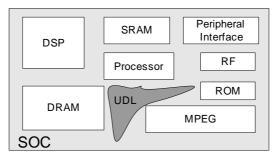

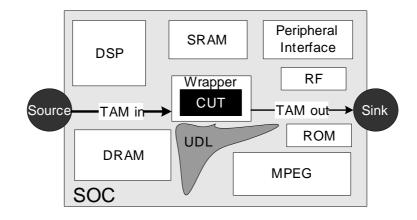

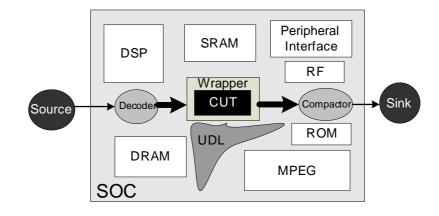

Figure 1.1: General Architecture of Core-Based System-on-a-Chip.

This chapter is organized as follows. We begin with an introduction to the core-based SOC design paradigm in Section 1.1. Section 1.2 illustrates the SOC test challenges and elaborates on several open questions that motivate this research work. Finally, Section 1.3 outlines the main contributions of this research and presents the organization of the thesis.

### 1.1 Core-Based SOC Design

The benefits of integrating an entire system on a single chip are manyfold. The reduction in chip count decreases the system cost because the cost of integrating multiple components is usually higher than the cost of the single SOC. The interconnect distance between components on a single silicon die is much shorter than on a board, which not only reduces timing delays and power dissipation, thus boosting the system performance, but also increases the system reliability. Further, a high integration is particularly desirable for applications where the product size is crucial, such as embedded mobile devices (e.g., cell phones or portable music players).

The main limitation of SOCs is the implementation time. To address this, SOC development is based on the design reuse philosophy, where two parties are involved: core providers and system integrators. Core providers create libraries of pre-designed and preverified building blocks, known as embedded cores, virtual components or macros. Embedded cores can be digital logic blocks, memories or analog (including radio frequency) circuits. Examples of cores include microprocessors, digital signal processors, analog-to-digital converters, network controllers, flash memories and peripherals. System integrators

put the SOC together by combining the available cores and their custom user-defined logic (UDL) [54], as shown in Figure 1.1.

Embedded cores come in different forms: soft, hard or firm. A soft core comes in the form of synthesizable hardware description language (HDL) code and has the advantage of being able to be easily re-targeted to different technologies. The trade-off for this flexibility and portability is unpredictability in area, performance and power. Hard cores, on the contrary, come with physical layout information and hence are technology-dependent. Despite the lack of flexibility, they are optimized for timing or power and have well-known performance parameters. Firm cores provide a trade-off between soft and hard cores. They are gate-level netlists and hence they are more predictable than soft cores, however, their size, aspect ratio and pin location can be tuned according to the system integrator's needs. Cores are often products of technology, software, and know-how that are subject to patents and copyrights. Hence, a core block represents intellectual property (IP) that the core provider licenses to the system integrator [54]. Therefore, the system integrator, who is in charge of core integration, verification, and also manufacturing test of the entire SOC (including the IP-protected internal cores), is not always entitled to make any changes to the core and is forced to reuse it "as is" (i.e., as a black box), knowing only the core's functionality without any implementation details.

In addition to the reusable cores from third-parties, SOCs often include UDLs for product differentiation and core interfacing. Because the UDLs are custom logic designed from scratch, the system integrator has full knowledge about both its functionality and structure.

### **1.2** Thesis Motivation

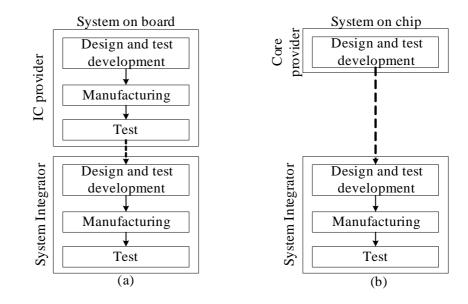

Although the design process for core-based SOCs is conceptually analogous to traditional board design, the manufacturing test process is fundamentally different [180]. In the traditional system-on-board approach, as shown in Figure 1.2(a), the IC provider performs chip design, manufacturing and test. The system integrator can assume the ICs are fault-free and he is only responsible for the design, assembly and test of the printed circuit board (PCB). Therefore, testing is usually limited to the interconnects between chips. In contrast, for the SOC approach, as shown in Figure 1.2(b), the cores are not yet manufactured when

Figure 1.2: Design Development Variations between Board and Chip [180].

the system integrator puts them together, thus the core providers cannot test their products for manufacturing defects. Manufacturing test can only be done by the system integrator once the chip is fabricated. This makes the testing of embedded cores a joint responsibility of both core providers and system integrators. Since the system integrator is usually forced to deal with cores as black boxes as discussed above, the core provider has to provide the model, the design for testability (DFT) [26] structures and the corresponding test vectors. The main difficulty for the system integrator is to provide a reliable and scalable test infrastructure for accessing the cores. This is required, since, contrary to PCBs where direct physical access to the chip pins is available, in SOCs the cores are embedded in the chip and thus, no direct access to the cores' terminals is available.

To enable the reuse of tests when a core gets embedded in multiple different SOCs, as well as to enable interoperable core-based testing of SOCs, the IEEE Std. 1500, i.e., IEEE standard for embedded core test (SECT) [67, 55], has been developed by the IEEE P1500 working group [117] (detailed in Section 3.1). A module-level test wrapper, similar to IEEE 1149.1 boundary-scan structures [132], is suggested to surround each embedded core, which allows inter-core and intra-core tests to be carried out via test access mechanisms (TAMs). IEEE Std. 1500 also standardizes a test information transfer model, i.e.,

IEEE 1450.6 core test language (CTL) [84]. IEEE Std. 1500, however, does not standardize the core's internal test methods or DFT structure, nor SOC test integration and optimization because of the differences in the test requirements for different technologies and the design styles of different cores and SOCs. Therefore, numerous strategies and algorithms in SOC test architecture design and optimization, test scheduling and test resource partitioning techniques have been proposed in the literature in order to reduce test cost of the SOC, based on the IEEE Std. 1500 test infrastructure.

Although the IEEE Std. 1500 and prior work in core-based SOC testing ease the task of system integrators for SOC test, with the ever increasing design complexity, many new problems are emerging:

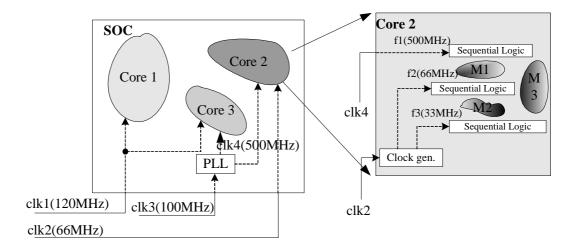

- *How to deal with the increasing number of clock domains inside embedded cores?* Many embedded cores operate internally with multiple frequencies. In functional mode care has been taken so that only safe transitions exist between the different clock domains. In test mode, however, if specific test clocking strategies are not employed, the test data might be corrupted due to clock skew. How to provide a reliable test strategy for such embedded multi-frequency cores is an open question.

- *How to apply delay tests for embedded cores?* With the continuous increase in speed of SOCs, verifying only logic correctness during manufacturing test is not sufficient to guarantee high quality products. To find out timing-related defects, dedicated atspeed delay test is required, which typically needs the application of consecutive test vector pairs. This consecutive testability, however, is not covered by prior research in modular SOC test architecture design.

- *How to effectively and efficiently test unwrapped logic blocks?* Embedded cores may have a large number of primary inputs (PIs) and primary outputs (POs), which can incur a large DFT area overhead when wrapping them. More importantly, IEEE Std. 1500 wrapper may also result in performance penalty because each wrapper cell adds a multiplexer on circuit's functional path. As a result, unlike the assumptions made by prior work that all embedded cores are 1500-wrapped, system integrators usually prefer to keep certain cores unwrapped in practice. In addition, the unwrapped UDLs

are typically distributed on chip and may contain many storage elements. The intercore test strategy provided by IEEE Std. 1500 treats these unwrapped logic blocks (including both unwrapped cores and UDLs) as non-scanned circuits and hence cannot provide sufficient controllability and observability for the circuits' internal memory elements, thus leading to fault coverage loss. Motivated by the above fact, a modular test strategy that provides the same testability for unwrapped logic blocks as when they are 1500-wrapped is required.

• *How to effectively and efficiently test SOCs with multiple levels of hierarchy?* Most of the prior work in this field assumes that the SOC hierarchy is flattened during test. This assumption, however, is becoming unrealistic. This is because, with the increase of reusability, sometimes the older-generation SOCs are themselves used as embedded cores in the new-generation SOC designs, thus leading to a hierarchical SOC design paradigm. Therefore, novel test strategies for hierarchical SOCs need to be developed.

Based on the above observations, the contributions and organization of this dissertation are presented in the next section.

### **1.3 Thesis Organization and Contributions**

The remainder of this dissertation is organized as follows. First the background for this research work is introduced in Chapter 2, including the basic VLSI manufacturing test concepts, various delay fault testing and multi-frequency testing strategies. Chapter 3 describes IEEE Std. 1500 in detail and presents a comprehensive overview of prior work in core-based SOC testing domain. Various test access strategies and the relevant solutions available for the design and optimization of SOC test architectures are reviewed.

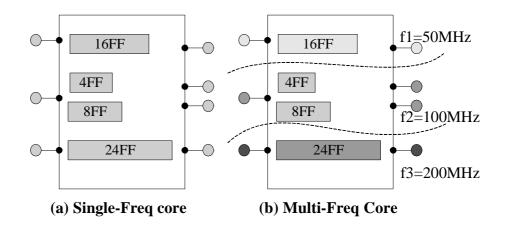

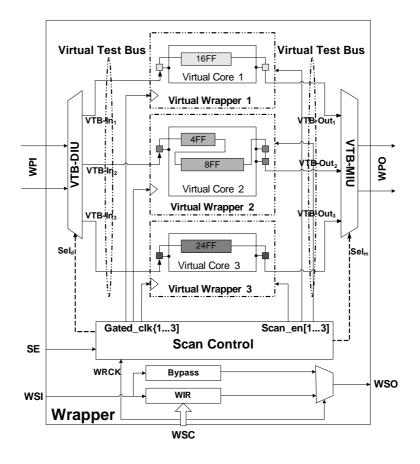

Motivated by the fact that most SOCs today include embedded cores that operate in multiple clock domains, Chapter 4 shows how at-speed test application can be achieved without test hazards by embedding custom logic in the multi-frequency core wrapper. The introduced limited DFT hardware can synchronize the external tester channels with the core's internal scan chains in the shift mode, and provide safe at-speed capture via a careful

capture window design. In addition, wrapper optimization algorithms are proposed, which efficiently utilize the available tester bandwidth and guarantee low test application time (TAT) within the given power ratings.

Although the at-speed testing strategy proposed in Chapter 4 is able to uncover some timing-related defects, to increase circuit reliability and manufacturing yield, system integrators are constrained to develop dedicated delay tests since more delay faults are emerging with the advancement of the VLSI fabrication technology. Therefore, in Chapter 5, we propose a novel architecture for two-pattern test of core-based SOCs, which can be used to achieve a reliable coverage of delay faults and complementary metal oxide semiconductor (CMOS) stuck-open faults. The proposed solution combines the dedicated bus-based test access mechanism and functional interconnects for test data transfer, in order to provide full controllability of the wrapper input cells in the two consecutive clock cycles required by two-pattern testing. This technique, however, introduces test schedule conflicts among different cores and hence increases the overall SOC test application time. Consequently, new algorithms for TAM design and test scheduling are proposed and design trade-offs between DFT area and testing time are discussed.

The main idea behind the proposed architecture for two-pattern test in Chapter 5 is a modular strategy that applies the test stimuli for the CUT through the functional interconnect. Following the same idea, Chapter 6 proposes solutions for reducing the number of wrapper boundary register cells without loss of the SOC test architecture's modularity and scalability for one-pattern tested cores. By utilizing the functional interconnect topology and the wrapper cells of the surrounding cores to transfer test stimuli and test responses, the wrapper of some cores can be removed without affecting the controllability/observability of the SOC. We present novel modular SOC test architectures for concurrently testing both the 1500-wrapped cores and unwrapped logic blocks. Since wrapper cells of cores that transfer test stimuli and test responses for unwrapped logic blocks become shared resources during test, conflicts arise during test scheduling that will negatively impact the SOC TAT. As a consequence, to alleviate this problem, we also present optimization algorithms for the proposed SOC test architectures.

Chapters 4, 5 and 6 present solutions for several emerging problems in testing SOCs

that have one level of hierarchy (SOC and cores). With the increase of reusability, pastgeneration SOCs might be used as embedded cores in next-generation designs, and hence an emerging problem is how to test such SOCs that have multiple levels of hierarchy. This problem is tackled in Chapter 7, which describes a new framework for the design and optimization of an hierarchical SOC test architecture. We first explore the concept that TAMs on the same level of design hierarchy employ multiple frequencies for test data transportation. Then, we extend this concept to hierarchical SOCs and, by introducing frequency converters at the inputs and outputs of the hierarchical cores, the proposed solution not only removes the constraint that the system level TAM width must be wider than the internal TAM width of hierarchical cores, but also facilitates rapid exploration of the trade-offs among TAT, test power and DFT hardware.

Finally, Chapter 8 summarizes the presented research work and concludes this thesis.

## Chapter 2

## Background

This chapter presents the background knowledge in VLSI testing, the process of identifying defects in an IC, for a better understanding of this dissertation. We first describe the manufacturing test concepts in Section 2.1, which lay the foundation for SOC testing. Sections 2.3 and 2.2 present the advancement of knowledge in delay fault testing and multifrequency testing over the past decades, respectively. Finally Section 2.4 concludes this chapter. Some of the descriptions and figures in this chapter are excerpted from [13, 158].

### 2.1 VLSI Testing Concepts

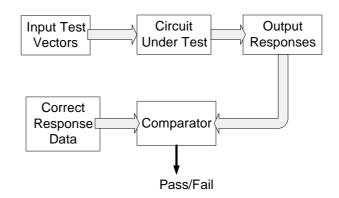

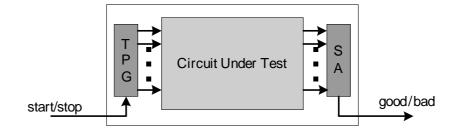

The basic principle of manufacturing test is illustrated in Figure 2.1. *Circuit under test* can be the entire chip or only a part of the chip (e.g., a logic block or a memory core). *Input test vectors* are binary patterns applied to the inputs of the circuit and the associated *output responses* are the values observed on the outputs of the circuit. Using a *comparator*, output responses are checked against the expected *correct response data*, which are obtained through simulation prior to design tape-out. If all the output responses match the correct response data, the circuit has passed the test and it is labeled as fault-free, otherwise, the circuit is said to be erroneous, and designers can either make a complete failure diagnosis or simply throw it away. *Automatic test equipment* (ATE), a powerful computer and measurement system operating under the control of a *test program*, is typically used to control the process of testing VLSI devices.

Figure 2.1: Principle of VLSI Testing.

Manufacturing test method used to identify defective chips can be divided into *functional test* and *structural test*. A complete functional test usually needs to check every entry of the truth table, which leads to extremely long testing time and makes it infeasible for complex digital systems [13] (one exception is the test of semiconductor memories due to their regularity and simple operations). Structural test, on the other hand, depends on the structure of the design. One of the greatest advantages of structural test is that it allows us to develop structural search algorithms to achieve efficient testing strategies, based on the fault modeling technique, discussed in the following.

#### 2.1.1 Defect vs. Fault Modeling

A defect in an electronic system is the unintended difference between the implemented hardware and its intended design [13]. Various kinds of defects exist in VLSI circuits [60]:

- 1. Process Defects for example, missing contact window, parasitic transistors, oxide breakdown.

- 2. Material Defects for example, bulk defects (cracks, crystal imperfection), surface impurities.

- 3. Age Defects for example, dielectric breakdown, electromigration.

- 4. Package Defects for example, contact degradation, seal leaks.

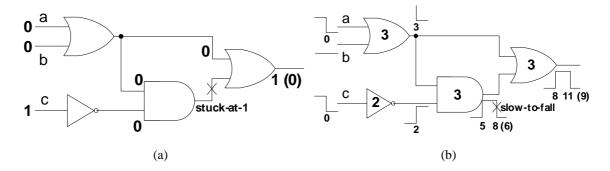

Figure 2.2: Commonly Used Fault Models: (a) Stuck-at Fault; (b)Delay Fault.

However, it is very hard to generate tests for every possible type of physical defects. Because the defects lead to faulty behaviors, they are usually modeled at a certain level of design abstraction for efficient testing, such as behavioral level, logic/gate level or transistor level. Fault models at behavioral level usually have no clear correlation to manufacturing defects and hence are used more often in design verification rather than manufacturing test. Transistor level fault models are also known as technology-dependent faults and are mainly used in analog circuit testing. Fault models based on logic gates (i.e., circuit is modeled as an interconnection of boolean gates, called netlist) are technology-independent and over time have been proven to be very efficient for testing digital circuits [13]. In the following we discuss some commonly-used fault models.

#### • Stuck-at Fault:

Stuck-at fault model, specifically, single stuck-at fault model is the fundamental fault model in digital testing, and it is also the most popular fault model used in the industry. In stuck-at fault model, each connecting line in the structural netlist can have only two types of faults: stuck to a logic value 0 (SA0) or 1 (SA1), as shown in Figure 2.2(a). In general, several stuck-at faults can be simultaneously present in the circuit, however, because the combinations of multiple stuck-at faults are prohibitively large, it is common practice to model only single stuck-at faults [13]. This single stuck-at fault model (based on the assumption that only one line is faulty at a time) has been extensively studied and is shown to be very effective to verify the logic correctness of the circuit [13].

#### • CMOS Stuck-Open and Stuck-Short Faults:

Case [14] found that the input-output behavior of a faulty CMOS logic circuit cannot be exactly represented by the stuck-at fault model. Since a CMOS logic gate consists of more than one transistor, instead of modeling faults at the gate level, these fault models assume just one transistor to be *stuck-open* or *stuck-short*. The effect of stuck-open faults is to produce a floating state at the output of the faulty logic gate. The effect of a stuck-short fault is to produce a power supply to ground conducting path.

#### • Delay Fault:

A digital system may also have timing failures without logic errors, i.e., it fails to operate at the specified speed but can produce correct outputs at slower or faster speed. Digital systems are usually synchronized by clock signals. Therefore, if the combinational logic elements cannot attain steady state within a clock period, the excessive propagation delay violates the *setup time* constraint of storage elements (i.e., flip-flops or latches). Alternatively, if the propagation delay through combinational logic is too short, it violates the *hold time* constraint of the storage elements. We mainly consider the former case because defects leading to excessive delay happen more often during manufacture. For example, as shown in Figure 2.2(b), because of the transition delay the output signal turns low at 11 instead of 9, if the period of system clock is 10, the storage element next to this logic will load the wrong value.

Commonly used delay fault models include the *transition fault model* (also called *gross-delay fault model*) and the *path delay fault model*. Transition fault model is based on the assumption that only a single gate delay is changed. It has the advantages of easy test set generation and comparably small test set size, but it is less accurate due to its simplistic assumption. Path delay fault model, however, considers the cumulative propagation delay of a combinational path and hence is much more accurate, but the test generation is extremely hard and normally requires a large number of test patterns. In addition, although path delay fault test generation has been researched for two decades, a large part of path delay faults remains untestable for state-of-the-art designs [98].

Different fault models may require different kinds of test pattern application strategies. For example, each stuck-at fault can be detected by a single test pattern. The delay fault, however, requires to examine signal transitions and hence consecutive test vector-pairs are needed, in which the first vector  $V_1$  initializes the circuit while the second vector  $V_2$  causes the desired transitions. Similarly, CMOS stuck-open fault is also detected by consecutive test vector-pairs, where  $V_1$  is used to initialize the circuit appropriately and  $V_2$  detects a stuck-at fault on the gate output. CMOS stuck-short fault is usually tested by quiescent current ( $I_{DDO}$ ) measurement because of its specific fault behavior.

#### 2.1.2 Test Pattern Generation

The task of the automatic test pattern generation (ATPG) process is to find a set of excitation vectors that cover a sufficient large portion of the fault set by the adopted fault model. To achieve this, ATPG algorithms first inject a fault into the circuit, and then use a variety of mechanisms to activate the fault and cause its effect to propagate through the hardware and manifest itself at circuit outputs [13]. ATPG is an extremely complex process, which may take weeks even months to achieve a high fault coverage for large designs, even with the help of specific test hardware.

In essence ATPG algorithms can be divided into combinational ATPG algorithms and sequential ATPG algorithms. The first and seminal combinational ATPG algorithm is D-algorithm proposed by Roth [147], which established the calculus and algorithms for ATPG using D-cubes. The next significant improvement is Goel's PODEM algorithm [43]. He efficiently used path propagation constraints to limit the ATPG algorithm search space. Fujiwara and Shimono's FAN algorithm [38, 39] further restricts the ATPG search space significantly by efficiently constraining the backtrace and considering signal information. Sequential ATPG algorithms are even more complex due to the unknown internal memory states at the beginning of test. As a result, the test must first initializes the internal states, and after test inputs are applied for several clock cycles the final states of memory elements must be propagated to primary outputs. The lack of controllability and observability to the internal nodes dramatically increases the test generation complexity. Commonly used algorithms for sequential ATPG are backward justification procedures through time-frame expansion [13]. To decrease the number of time-frames and hence ATPG complexity, it is

common practice to limit the sequential steps during test, using specific test hardware, as discussed in Section 2.1.3.

Since a test pattern can potentially detect several faults at the same time, ATPG algorithms are usually combined with fault simulation techniques during test generation. One possible approach is to start from a random set of test patterns. Fault simulation then determines how many faults are detected and these faults are then declared to be covered and removed from the fault set. After this trial random pattern phase, an ATPG algorithm is executed to target the remaining undetected faults. Whenever a deterministic test pattern is acquired, fault simulation is utilized again to find other faults that can be detected by this pattern. This process is repeated over and over until a desired fault coverage is achieved. It should be noted that the test patterns generated from ATPG process feature a large portion of "don't-care" bits (i.e., they can be assigned to any logic value without affecting the fault coverage of the test set), and test data volume can be dramatically reduced by manipulating these unspecified bits using efficient compaction and/or compression methods.

### 2.1.3 Design for Testability (DFT)

DFT is the design process which embeds special hardware for testing purpose only. With the ever increasing transistor to pin ratio in VLSI circuits, test generation is impractical without introducing DFT logic. The main purpose of DFT is to increase the controllability (i.e., the ability to set a particular logic signal to a 0 or a 1 within the circuit) and the observability (i.e., the ability to observe the state of a logic signal within the circuit) of the circuit's internal node. Two widely accepted DFT methodologies are illustrated in this section: scan based DFT and built-in self-test (BIST).

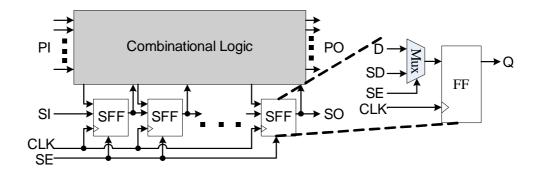

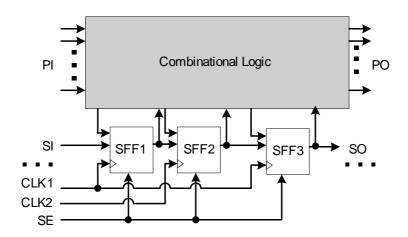

**Scan based DFT:** The main idea for scan based DFT is to obtain controllability and observability for internal flip-flops. This is done by replacing all or part of the flip-flops of the circuit with scanned flip-flops (SFFs). In the test mode, these scanned flip-flops functionally form one or more long shift registers (called *scan chains*). The input/output (I/O) of these scan chains are connected to primary I/Os of the chip, hence, all the SFFs can be set to any desired state by shifting those logic states into the scan chains. Similarly, the states of these SFFs can be observed by shifting out the contents of the shift registers.

Figure 2.3: A Single Scan Chain Design Schematic.

There are various types of implementation of SFFs, e.g., mux-based SFF, double latched SFF, level sensitive scan latches SFF [1, 13]. The one illustrated in Figure 2.3 and considered in this dissertation is the mux-based SFF, which is composed of a multiplexer and a D flip-flop. The SFF has two data inputs: the original data input D and the scan-data input SD, a scan enable signal SE controls which input is stored in the flip-flop. The scan chain is constructed by connecting the data output Q of one SFF to SD signal of the following SFF, as illustrated in the figure. Applying a test vector using scan based DFT implies three steps: (i) scanning-in the test stimuli, i.e., SE is set to 1 (test mode), the data is loaded from the scan input SI into the scan chain in  $N_{sc}$  clock cycles, where  $N_{sc}$  is the scan chain length; (ii) capturing the circuit responses, i.e., SE is set to 0, the data is loaded from the combinational logic outputs in 1 clock cycle; and (iii) scanning-out the test responses, i.e., similar to scan-in where the circuit responses are scanned out. It should be noted that the last step is usually performed simultaneously with the first step in a pipelined fashion, where new control values are loaded.