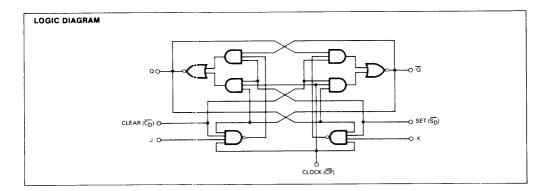

**DESCRIPTION** — The SN54LS/74LS76A offers individual J, K, Clock Pulse, Direct Set and Direct Clear inputs. These dual flip-flops are designed so that when the clock goes HIGH, the inputs are enabled and data will be accepted. The Logic Level of the J and K inputs will perform according to the Truth Table as long as minimum set-up times are observed. Input data is transferred to the outputs on the HIGH-to-LOW clock transitions.

## **SN54LS76A SN74LS76A**

## DUAL JK FLIP-FLOP WITH SET AND CLEAR

LOW POWER SCHOTTKY

## MODE SELECT -- TRUTH TABLE

| OPERATING MODE                                                                                | INPUTS         |                 |                            |                  | OUTPUTS   |             |

|-----------------------------------------------------------------------------------------------|----------------|-----------------|----------------------------|------------------|-----------|-------------|

|                                                                                               | S <sub>D</sub> | ¯c <sub>D</sub> | J                          | к                | Q         | ā           |

| Set<br>Reset (Clear)<br>"Undetermined<br>Toggle<br>Load "0" (Reset)<br>Load "1" (Set)<br>Hold |                | TLLTTT          | X<br>X<br>h<br>l<br>h<br>l | X<br>X<br>h<br>h | HLHIGLH Q | L H 4 H L 4 |

\*Both outputs will be HIGH while both  $\vec{S}_D$  and  $\vec{C}_D$  are LOW, but the output states are unpredictable if  $\vec{S}_D$  and  $\vec{C}_D$  go HIGH simultaneously.

H,h = HIGH Voltage Level

L.I = LOW Voltage Level

X = Immaterial

I,h (q) = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the HIGH-to-LOW clock transition.

LOGIC SYMBOL

J Suffix — Case 620-08 (Ceramic) N Suffix — Case 648-05 (Plastic)

V<sub>CC</sub> = Pin 5 GND = Pin 13