# Logic Design

## Synchronous Sequential Circuits

## Introduction

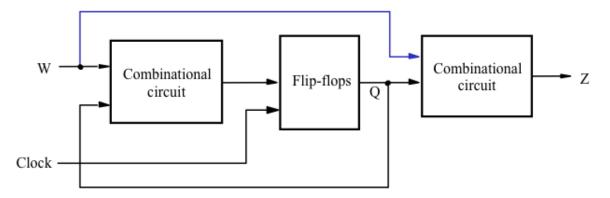

- Combinational circuits: value of each output depends only on the values of inputs

- Sequential Circuits: values of outputs depend on inputs and past behavior of the circuit

- In most cases a clock is used to control the operation of a sequential circuit

- These circuits are called synchronous sequential circuits

- Synchronous sequential circuits are realized using combinational logic and one or more flip-flops

- State: the value of outputs of flip-flops

- Under the control of clock signal, flip-flop outputs change their state as determined by the combinational logic

Figure 8.1. The general form of a sequential circuit.

- To ensure that only one transition from one state to another takes place during one clock cycle, flip-flops are edge-triggered

- Outputs are generated by another combinational circuit and are function of present state of the flip-flops and the inputs

- Outputs do not necessarily have to depend directly on the inputs

- Moore type: the output depends only on the state of the circuit

- Mealy type: outputs depend on both the state and the inputs

- Sequential circuits are also called finite state machines (FSM)

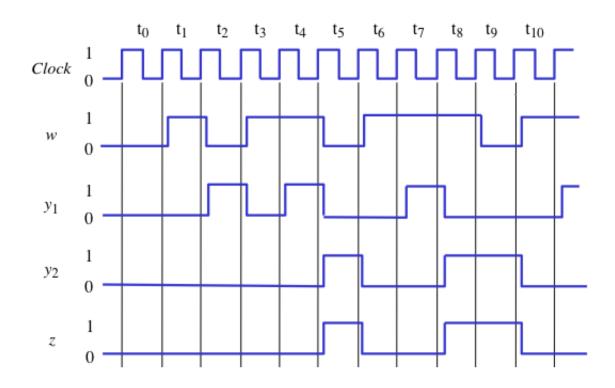

- Design a circuit that:

- Has one input (w) and one output (z)

- All changes occur on the positive edge of the clock

- Output z is equal to 1 if during the two immediately preceding clock cycles the input w was equal to 1. Otherwise z is equal to 0.

| Clockcycle:<br>w: | t <sub>0</sub> | $t_1$ | t <sub>2</sub> | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|-------------------|----------------|-------|----------------|----|----|----|----------------|----|----------------|----|-----------------|

| <i>w</i> :        | 0              | 1     | 0              | 1  | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| <i>z</i> :        | 0              | 0     | 0              | 0  | 0  | 1  | 0              | 0  | 1              | 1  | 0               |

#### Figure 8.2. Sequences of input and output signals.

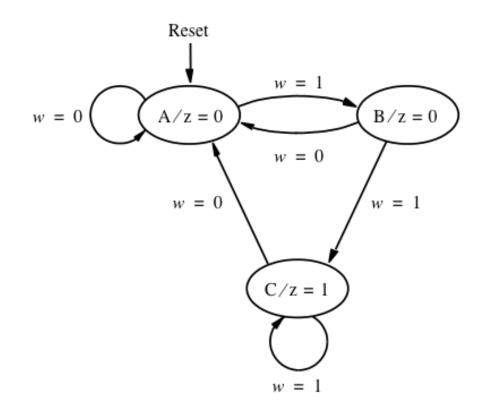

- First step in designing a FSM: determine how many states are needed and which transitions are possible from one state to another

- No set procedure for this task

- A good way is select a starting state (a state that the circuit enters when the power is turned on or a reset signal is applied)

- Starting state A

- As long as w is 0, the circuit should remain in A

- When w becomes 1, the machine should move to a different state (B)

#### State Diagram

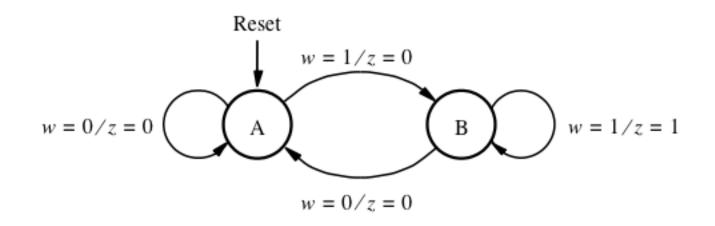

Figure 8.3. State diagram of a simple sequential circuit.

#### State Table

| Present | Next  | state | Output |

|---------|-------|-------|--------|

| state   | w = 0 | w = 1 | Z      |

| А       | А     | В     | 0      |

| В       | А     | С     | 0      |

| С       | А     | С     | 1      |

Figure 8.4. State table for the sequential circuit in Figure 8.3.

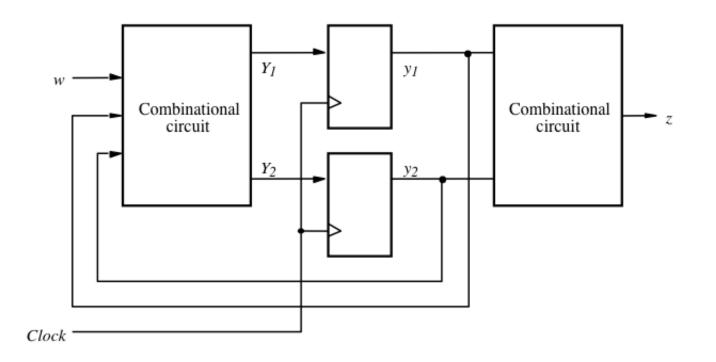

- When implemented in logic circuits, each state is represented by a particular valuation (combination) of state variables

- Each state variable may be implemented in the form of a flip-flop

- Since there are three states in this example, two state variables are sufficient: y<sub>1</sub> and y<sub>2</sub>

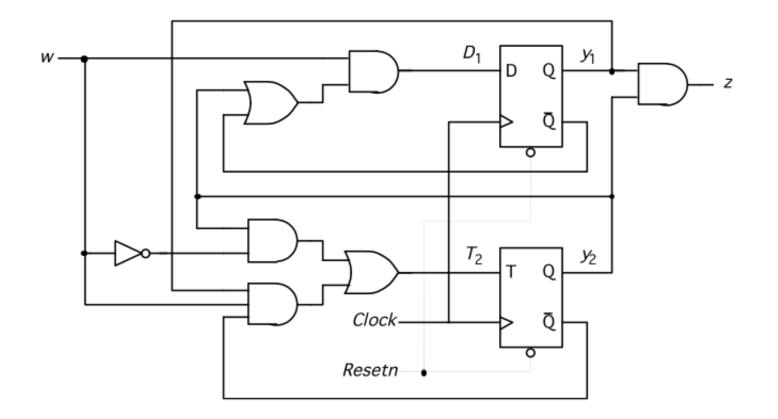

Figure 8.5. A general sequential circuit with input w, output z, and two state flip-flops.

- We need to design a combinational circuit with inputs w, y1 and y2 such that for all valuations of these signals Y1 and Y2 will cause the machine to move to the next state

- We create a truth table by assigning specific valuation of variables y1 and y2 to each state

|   | Present                       | Next s                        | tate                                                |        |

|---|-------------------------------|-------------------------------|-----------------------------------------------------|--------|

|   | state                         | w = 0                         | w = 1                                               | Output |

|   | <sup>y</sup> 2 <sup>y</sup> 1 | <sup>Y</sup> 2 <sup>Y</sup> 1 | <sup>Y</sup> <sub>2</sub> <sup>Y</sup> <sub>1</sub> | Z      |

| A | 00                            | 00                            | 01                                                  | 0      |

| в | 01                            | 00                            | 10                                                  | 0      |

| С | 10                            | 00                            | 10                                                  | 1      |

|   | 11                            | dd                            | dd                                                  | d      |

Figure 8.6. State-assigned table for the sequential circuit in Figure 8.4.

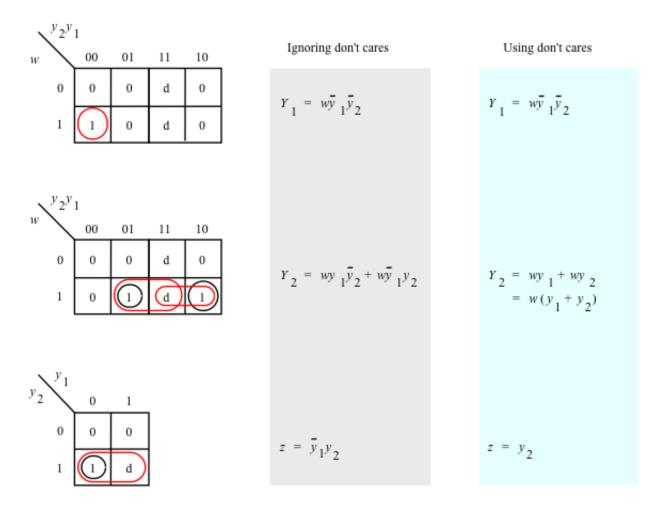

- Choice of flip-flop:

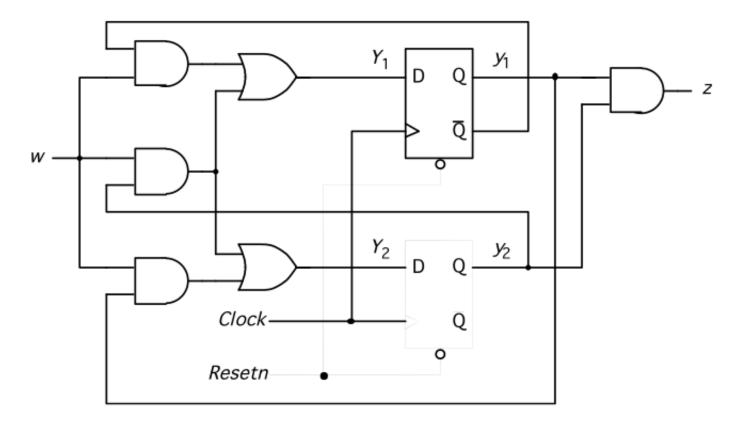

- Most straightforward choice is to use D flip-flops because the values of Y1 and Y2 are simply clocked into the flip-flops to become the new values of y1 and y2

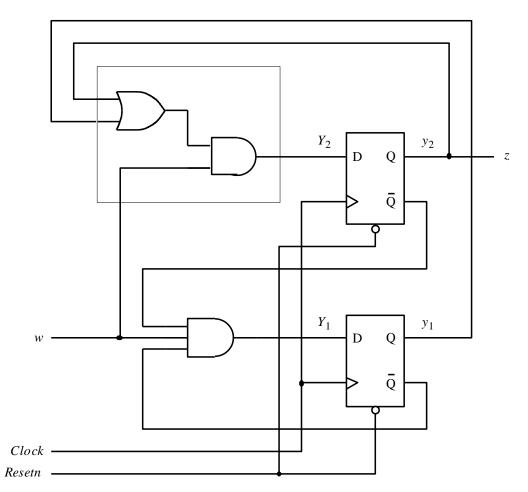

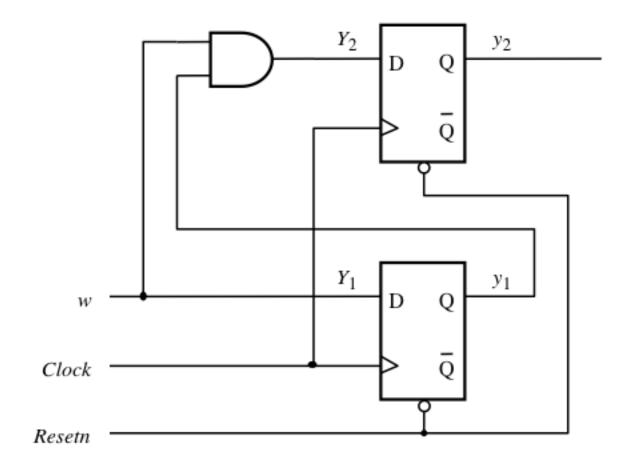

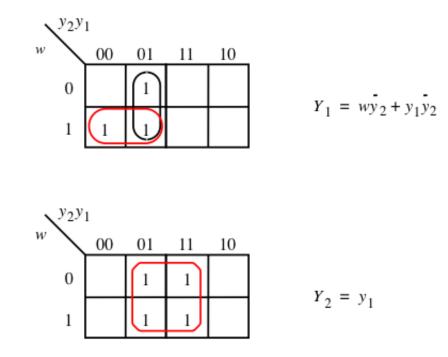

Figure 8.7. Derivation of logic expressions for the sequential circuit in Figure 8.6.

Figure 8.8. Final implementation of the sequential circuit derived in Figure 8.7.

Figure 8.9. Timing diagram for the circuit in Figure 8.8.

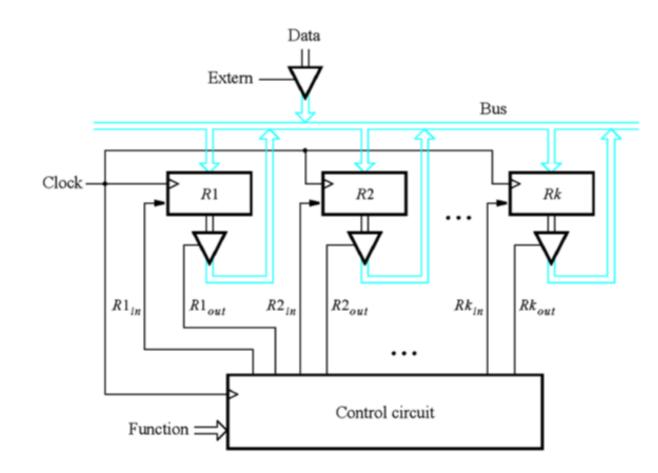

- Digital systems often contain a set of registers to store data

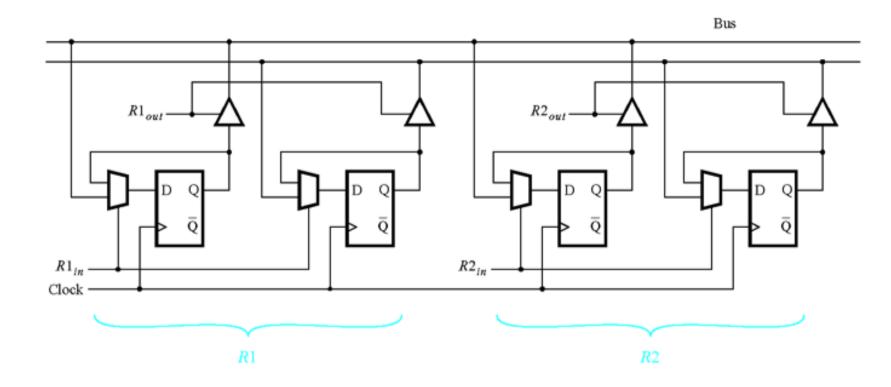

- Each register is connected to a common set of n wires, used to transfer data into and out of registers

- This common set of wires is called a bus

- In addition to registers other types of circuits would be connected to the bus

- It is essential to ensure that only one circuit block attempts to place data onto the bus wires at any given time

- A control circuit is used to ensure that only one of the tri-state buffers enables is asserted at a given time

Figure 7.55. A digital system with k registers.

Figure 7.56. Details for connecting registers to a bus.

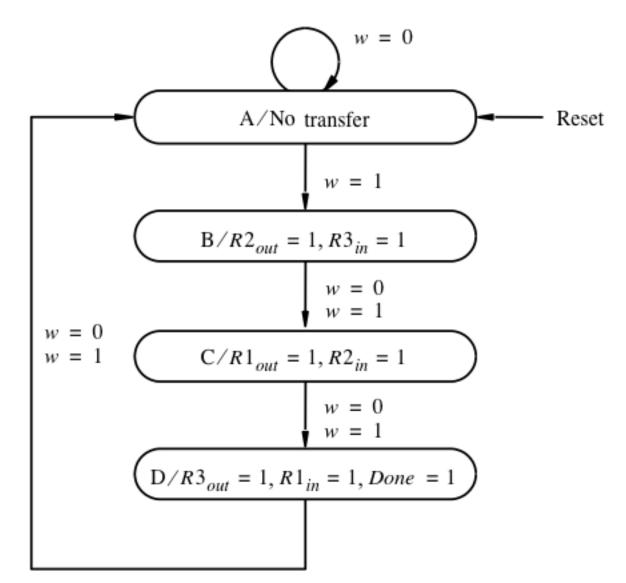

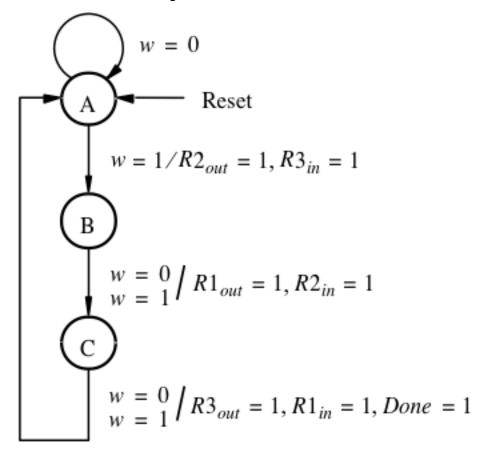

- An example: consider a system that has three registers, R1, R2 and R3. We want to swap the content of R1 and R2

- Steps:

- Copy R2 to R3

- Copy R1 to R2

- Transfer R3 to R1

- Content of R2 is loaded into R3 using  $R2_{out}=1$ ,  $R3_{in}=1$

- Content of R1 is transferred into R2 using R1<sub>out</sub>=1, R2<sub>in</sub>=1

- Content of R3 is transferred into R1 using  $R3_{out}=1$ ,  $R1_{in}=1$

- We will indicate the completion of the task by setting a signal Done=1

| Present | Next  | t state |            |           |            | Outputs   |            |           |      |

|---------|-------|---------|------------|-----------|------------|-----------|------------|-----------|------|

| state   | w = 0 | w = 1   | $R1_{out}$ | $R1_{in}$ | $R2_{out}$ | $R2_{in}$ | $R3_{out}$ | $R3_{in}$ | Done |

| Α       | А     | В       | 0          | 0         | 0          | 0         | 0          | 0         | 0    |

| В       | С     | С       | 0          | 0         | 1          | 0         | 0          | 1         | 0    |

| C       | D     | D       | 1          | 0         | 0          | 1         | 0          | 0         | 0    |

| D       | Α     | А       | 0          | 1         | 0          | 0         | 1          | 0         | 1    |

| Present  | Next     | state    | Outputs    |           |            |           |            |           |      |  |

|----------|----------|----------|------------|-----------|------------|-----------|------------|-----------|------|--|

| state    | w = 0    | w = 1    |            |           |            | Outputs   |            |           |      |  |

| $y_2y_1$ | $Y_2Y_1$ | $Y_2Y_1$ | $R1_{out}$ | $R1_{in}$ | $R2_{out}$ | $R2_{in}$ | $R3_{out}$ | $R3_{in}$ | Done |  |

| 00       | 00       | 01       | 0          | 0         | 0          | 0         | 0          | 0         | 0    |  |

| 01       | 10       | 10       | 0          | 0         | 1          | 0         | 0          | 1         | 0    |  |

| 10       | 11       | 11       | 1          | 0         | 0          | 1         | 0          | 0         | 0    |  |

| 11       | 00       | 0 0      | 0          | 1         | 0          | 0         | 1          | 0         | 1    |  |

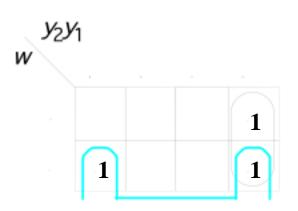

А

B C D

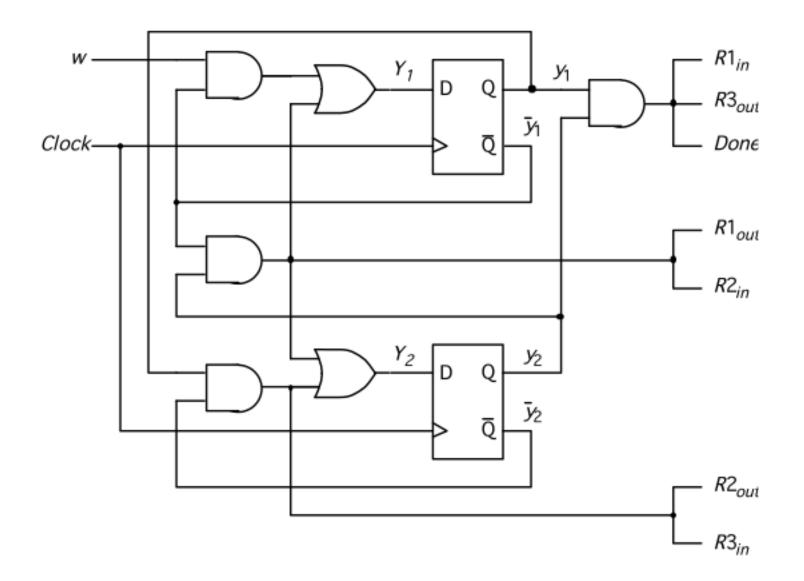

$$Y_1 = w\bar{y}_1 + \bar{y}_1 y_2$$

$$Y_2 = y_1 \bar{y}_2 + \bar{y}_1 y_2$$

$$R1_{out} = R2_{in} = \bar{y}_1 y_2$$

$$R1_{in} = R3_{out} = Done = y_1 y_2$$

$$R2_{out} = R3_{in} = y_1\bar{y}_2$$

- Some state assignment might be better than the others

- It is often impossible to find the best state assignment for a large circuit

- Exhaustive search is not practical because the number of available state assignments is huge

- Y1=D1=w

- Y2=D2=wy1

- z=y2

|   | Present               | Next      | state     |        |

|---|-----------------------|-----------|-----------|--------|

|   | state                 | w = 0     | w = 1     | Output |

|   | <i>Y</i> 2 <i>Y</i> 1 | $Y_2 Y_1$ | $Y_2 Y_1$ | z      |

| A | 00                    | 00        | 01        | 0      |

| B | 01                    | 00        | 11        | 0      |

| С | 11                    | 00        | 11        | 1      |

|   | 10                    | dd        | dd        | d      |

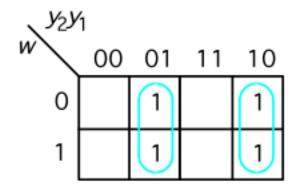

• We now consider a different state assignment for the bus controller example

|   | Presen    | t Nex    | tstate   |            |           |            | <b>o</b> . |            |           |      |

|---|-----------|----------|----------|------------|-----------|------------|------------|------------|-----------|------|

|   | state     | w = 0    | w = 1    |            |           |            | Outpu      | ts         |           |      |

|   | $y_2 y_1$ | $Y_2Y_1$ | $Y_2Y_1$ | $R1_{out}$ | $R1_{in}$ | $R2_{out}$ | $R2_{in}$  | $R3_{out}$ | $R3_{in}$ | Done |

| Α | 00        | 00       | 01       | 0          | 0         | 0          | 0          | 0          | 0         | 0    |

| В | 01        | 11       | 11       | 0          | 0         | 1          | 0          | 0          | 1         | 0    |

| С | 11        | 10       | 10       | 1          | 0         | 0          | 1          | 0          | 0         | 0    |

| D | 10        | 00       | 00       | 0          | 1         | 0          | 0          | 1          | 0         | 1    |

Figure 8.19. Derivation of next-state expressions for the sequential circuit in Figure 8.18.

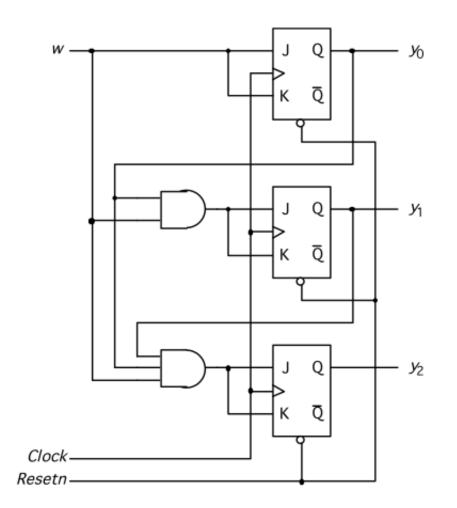

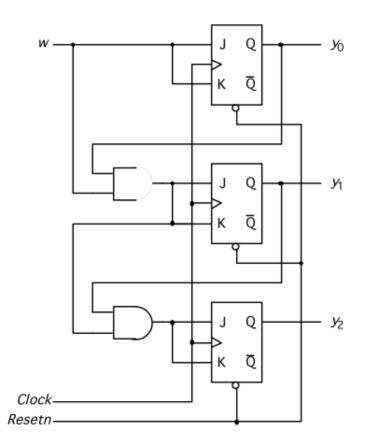

- One possibility is to use as many state variables as there are states

- For each state all but one of the state variables are equal to 0

- This approach is known as one-hot coding

- Y1=w'

- Y2=wy<sub>1</sub>

- Y3=wy<sub>1</sub>'

• z=y<sub>3</sub>

|   | Present                          | Next        | state       |        |

|---|----------------------------------|-------------|-------------|--------|

|   | state                            | w = 0       | w = 1       | Output |

|   | <i>y</i> 3 <i>y</i> 2 <i>y</i> 1 | $Y_3Y_2Y_1$ | $Y_3Y_2Y_1$ | Z      |

| A | 001                              | 001         | 010         | 0      |

| B | 010                              | 001         | 100         | 0      |

| C | 100                              | 001         | 100         | 1      |

|   | Present<br>state  | Nextstate<br>w = 0 $w = 1$ |                | Outputs    |           |            |           |            |           |      |  |  |  |

|---|-------------------|----------------------------|----------------|------------|-----------|------------|-----------|------------|-----------|------|--|--|--|

|   | $y_4 y_3 y_2 y_1$ | $Y_4Y_3Y_2Y_1$             | $Y_4Y_3Y_2Y_1$ | $R1_{out}$ | $R1_{in}$ | $R2_{out}$ | $R2_{in}$ | $R3_{out}$ | $R3_{in}$ | Done |  |  |  |

| А | 0 001             | 0001                       | 0010           | 0          | 0         | 0          | 0         | 0          | 0         | 0    |  |  |  |

| В | 0 010             | 0100                       | 0100           | 0          | 0         | 1          | 0         | 0          | 1         | 0    |  |  |  |

| С | 0 100             | 1000                       | 1000           | 1          | 0         | 0          | 1         | 0          | 0         | 0    |  |  |  |

| D | 1 000             | 0001                       | 0001           | 0          | 1         | 0          | 0         | 1          | 0         | 1    |  |  |  |

$$Y_{1} = w'y_{1} + y_{4}$$

$$Y_{2} = wy_{1}$$

$$Y_{3} = y_{2}$$

$$R1_{out} = R2_{in} = y_{3}$$

$$R1_{in} = R3_{out} = Done = y_{4}$$

$$R2_{out} = R3_{in} = y_{2}$$

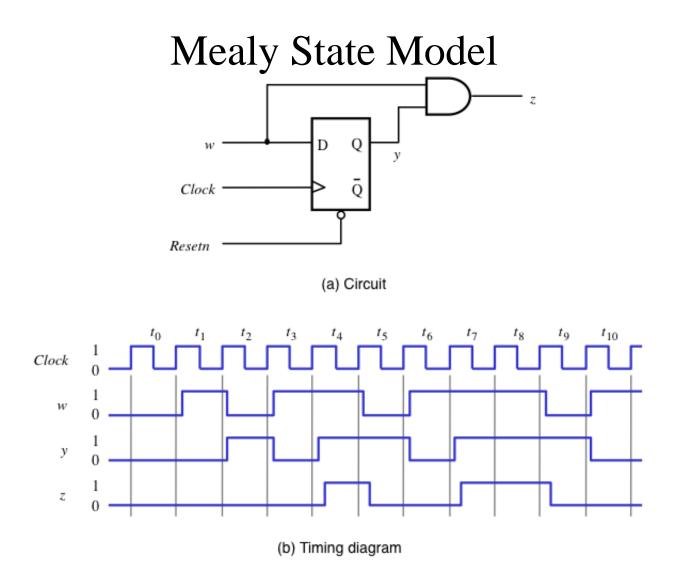

## Mealy State Model

- Mealy state machine: output values are generated based on both the state and the inputs

- Example: design a sequential circuit that the output z is equal to 1 in the same clock cycle when the second occurrence of w (input ) is detected

| Clock cycle:<br>w: | t <sub>0</sub> | t <sub>1</sub> | t <sub>2</sub> | t3 | t4 | t5 | t <sub>6</sub> | t7 | t <sub>8</sub> | t9 | t <sub>10</sub> |

|--------------------|----------------|----------------|----------------|----|----|----|----------------|----|----------------|----|-----------------|

| w:                 | 0              | 1              | 0              | 1  | 1  | 0  | 1              | 1  | 1              | 0  | 1               |

| <i>z</i> :         | 0              | 0              | 0              | 0  | 1  | 0  | 0              | 1  | 1              | 0  | 0               |

Figure 8.23. State diagram of an FSM that realizes the task in Figure 8.22.

| Present | Next  | state | Outj  | out z |

|---------|-------|-------|-------|-------|

| state   | w = 0 | w = 1 | w = 0 | w = 1 |

| А       | А     | В     | 0     | 0     |

| В       | А     | В     | 0     | 1     |

#### Figure 8.24. State table for the FSM in Figure 8.23.

|   | Present | Next  | state | Output |       |

|---|---------|-------|-------|--------|-------|

|   | state   | w = 0 | w = 1 | w = 0  | w = 1 |

|   | У       | Y     | Y     | Z      | Z     |

| A | 0       | 0     | 1     | 0      | 0     |

| В | 1       | 0     | 1     | 0      | 1     |

Figure 8.25. State-assigned table for the FSM in Figure 8.24.

Figure 8.26. Implementation of FSM in Figure 8.25.

Figure 8.28. State diagram for Example 8.4.

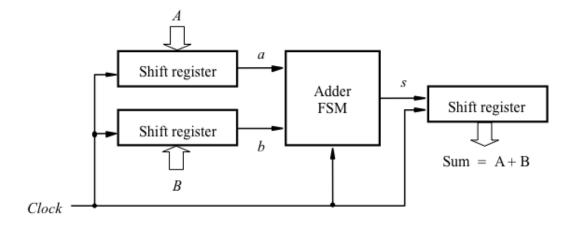

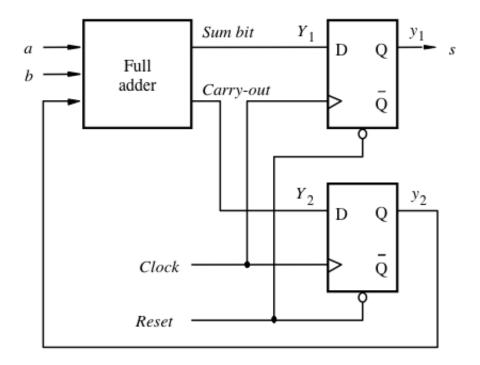

- If speed is not of great importance, a cost-effective option is to use a serial adder

- Serial adder: bits are added a pair at a time (in one clock cycle)

- A=an-1an-2...a0, B=bn-1bn-2...b0

Figure 8.39. Block diagram for the serial adder.

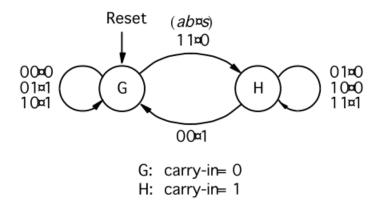

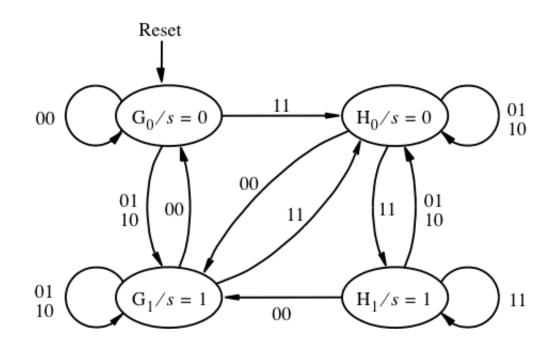

- G: state that the carry-in is 0

- H: state that the carry-in is1

Figure 8.40. State diagram for the serial adder FSM.

| Present | N             | ext st | ate |    |    | Out | put s |    |

|---------|---------------|--------|-----|----|----|-----|-------|----|

| state   | <i>ab</i> =00 | 01     | 10  | 11 | 00 | 01  | 10    | 11 |

| G       | G             | G      | G   | Н  | 0  | 1   | 1     | 0  |

| Н       | G             | Н      | Н   | Н  | 1  | 0   | 0     | 1  |

Figure 8.41. State table for the serial adder FSM.

| Present | N             | ext st | ate |    |    | Ou | tput |    |

|---------|---------------|--------|-----|----|----|----|------|----|

| state   | <i>ab</i> =00 | 01     | 10  | 11 | 00 | 01 | 10   | 11 |

| У       |               | Y      |     |    |    |    | 5    |    |

| 0       | 0             | 0      | 0   | 1  | 0  | 1  | 1    | 0  |

| 1       | 0             | 1      | 1   | 1  | 1  | 0  | 0    | 1  |

Figure 8.42. State-assigned table for Figure 8.41.

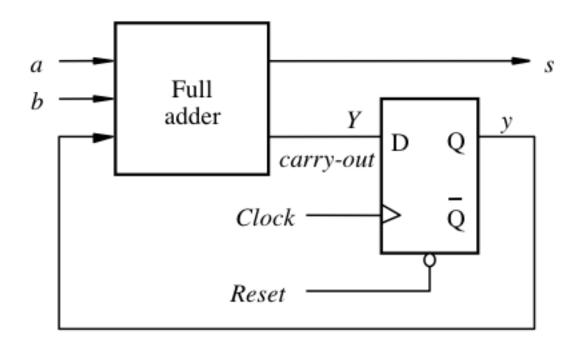

$$Y = ab + ay + by$$

$$s = a \oplus b \oplus c$$

#### Figure 8.43. Circuit for the adder FSM in Figure 8.39.

- Since in both states G and H, it is possible to generate two outputs depending on the input, a Moore-type FSM will need more than two states

- G0 and G1: carry is 0 sum is 0 or 1

- H0 andH1: carry is 1 sum is 0 or 1

Figure 8.44. State diagram for the Moore-type serial adder FSM.

| Present        | N             | lextsta                   | ite                       |       | Output |

|----------------|---------------|---------------------------|---------------------------|-------|--------|

| state          | <i>ab</i> =00 | 01                        | 10                        | 11    | s      |

| G <sub>0</sub> | $G_0$         | $G_1$                     | $G_1$                     | $H_0$ | 0      |

| G <sub>1</sub> | $G_0$         | $G_1$                     | $G_1$                     | $H_0$ | 1      |

| H <sub>0</sub> | G1            | $H_0$                     | $H_0$                     | $H_1$ | 0      |

| $H_1$          | $G_1$         | $\mathrm{H}_{\mathrm{0}}$ | $\mathrm{H}_{\mathrm{0}}$ | $H_1$ | 1      |

Figure 8.45. State table for the Moore-type serial adder FSM.

| Present               | ١             | Vextst  | ate |    |        |

|-----------------------|---------------|---------|-----|----|--------|

| state                 | <i>ab</i> =00 | 01      | 10  | 11 | Output |

| <i>Y</i> 2 <i>Y</i> 1 |               | $Y_2 Y$ | 1   |    | S      |

| 00                    | 0 0           | 01      | 01  | 10 | 0      |

| 01                    | 0 0           | 01      | 0 1 | 10 | 1      |

| 10                    | 0 1           | 10      | 10  | 11 | 0      |

| 11                    | 01            | 10      | 10  | 11 | 1      |

Figure 8.46. State-assigned table for Figure 8.45.

$$Y_2 = ab + ay_2 + by_2$$

$$Y_1 = a \oplus b \oplus c$$

$$s = y_1$$

Figure 8.47. Circuit for the Moore-type serial adder FSM.

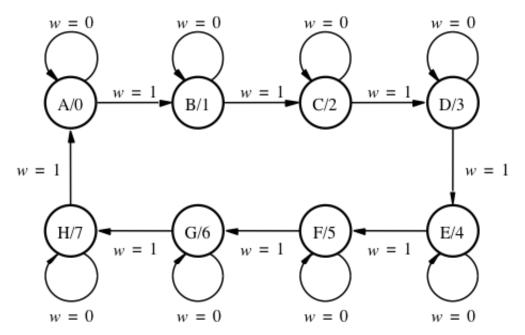

## Counter design using sequential circuits

- Counting sequence: 0,1,2,3,4,5,6,7,0,1,...

- Input signal w: if w=1 count is incremented, if w=0 count is frozen

Figure 8.60. State diagram for the counter.

#### State table

| Present | Next  | state | Output   |

|---------|-------|-------|----------|

| state   | w = 0 | w = 1 | <b>F</b> |

| А       | А     | В     | 0        |

| В       | В     | С     | 1        |

| С       | С     | D     | 2        |

| D       | D     | Е     | 3        |

| Е       | Е     | F     | 4        |

| F       | F     | G     | 5        |

| G       | G     | Н     | 6        |

| Н       | Н     | А     | 7        |

Figure 8.61. State table for the counter.

|   | Present                          | Next          | Next state    |        |  |  |

|---|----------------------------------|---------------|---------------|--------|--|--|

|   | state                            | w = 0         | w = 1         | Count  |  |  |

|   | <i>Y</i> 2 <i>Y</i> 1 <i>Y</i> 0 | $Y_2 Y_1 Y_0$ | $Y_2 Y_1 Y_0$ | Z2Z1Z0 |  |  |

| A | 000                              | 000           | 001           | 000    |  |  |

| В | 001                              | 001           | 010           | 001    |  |  |

| С | 010                              | 010           | 011           | 010    |  |  |

| D | 011                              | 011           | 100           | 011    |  |  |

| E | 100                              | 100           | 101           | 100    |  |  |

| F | 101                              | 101           | 110           | 101    |  |  |

| G | 110                              | 110           | 111           | 110    |  |  |

| Н | 111                              | 111           | 000           | 111    |  |  |

Figure 8.62. State-assigned table for the counter.

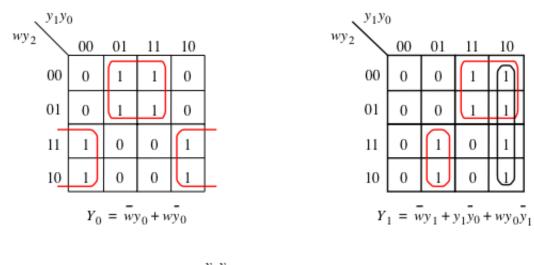

#### Implementation using D flip-flop

Figure 8.63. Karnaugh maps for D flip-flops for the counter.

$$D_0 = Y_0 = w'y_0 + wy'_0$$

$$D_1 = Y_1 = w'y_1 + y_1y'_0 + wy_0y'_1$$

$$D_2 = Y_2 = w'y_2 + y_2y'_0 + y_2y'_1 + wy_0y_1y'_2$$

Figure 8.64. Circuit diagram for the counter implemented with D flip-flops.

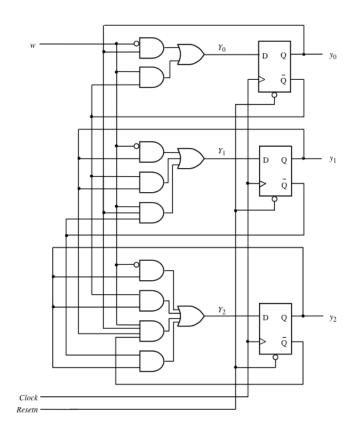

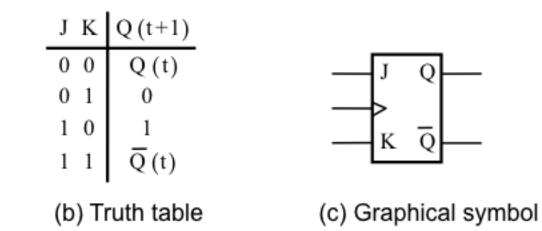

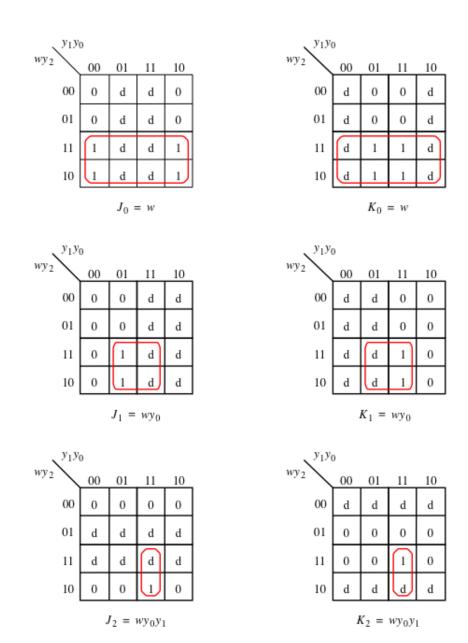

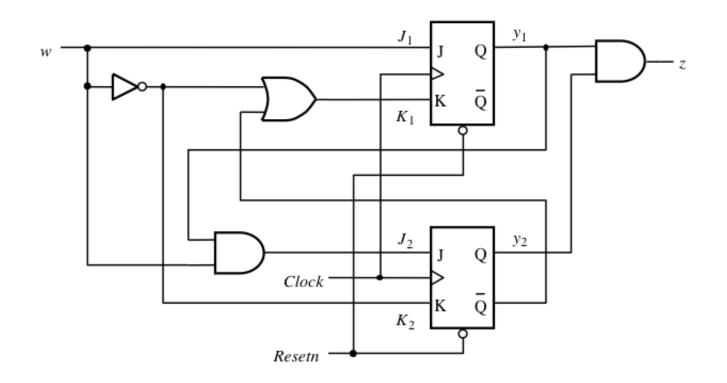

## Implementation using JK flip-flop

- For a JK flip-flop:

- If state=0, to remains in 0 J=0, K=d

- If state=0, to change to 1 J=1, K=d

- If state=1, to remains in 1 J=d, K=0

- If state=1, to remains in 0 J=d, K=1

|   | Present                          |               | Flip-flop inputs |          |          |               |          |          |          |        |

|---|----------------------------------|---------------|------------------|----------|----------|---------------|----------|----------|----------|--------|

|   | state                            |               | w = 0            |          |          | w = 1         |          |          |          | Count  |

|   | <i>Y</i> 2 <i>Y</i> 1 <i>Y</i> 0 | $Y_2 Y_1 Y_0$ | $J_2K_2$         | $J_1K_1$ | $J_0K_0$ | $Y_2 Y_1 Y_0$ | $J_2K_2$ | $J_1K_1$ | $J_0K_0$ | Z2Z1Z0 |

| A | 000                              | 000           | 0d               | 0d       | 0d       | 001           | 0d       | 0d       | 1d       | 000    |

| B | 001                              | 001           | 0d               | 0d       | d0       | 010           | 0d       | 1d       | d1       | 001    |

| C | 010                              | 010           | 0d               | d0       | 0d       | 011           | 0d       | d0       | 1d       | 010    |

| D | 011                              | 011           | 0d               | d0       | d0       | 100           | 1d       | d1       | d1       | 011    |

| E | 100                              | 100           | d0               | 0d       | 0d       | 101           | d0       | 0d       | 1d       | 100    |

| F | 101                              | 101           | d0               | 0d       | d0       | 110           | d0       | 1d       | d1       | 101    |

| G | 110                              | 110           | d0               | d0       | 0d       | 111           | d0       | d0       | 1d       | 110    |

| н | 111                              | 111           | d0               | d0       | d0       | 000           | d1       | d1       | d1       | 111    |

Figure 8.65. Excitation table for the counter with JK flip-flops.

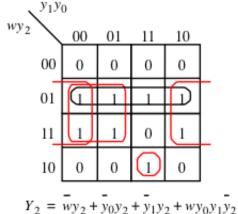

Figure 8.66. Karnaugh maps for JK flip-flops in the counter.

Figure 8.67. Circuit diagram using JK flip-flops.

Figure 8.68. Factored-form implementation of the counter.

# Analysis of Synchronous Sequential Circuits

- Outputs of flip-flops represent the current state

- Inputs of flip-flops determine the next state

- We can build the state transition table

- Then we build state diagram

Figure 8.80. Circuit for Example 8.8.

$$Y_1 = wy_2 + wy'_1$$

$$Y_2 = wy_1 + wy_2$$

$$z = y_2y_1$$

| Present | Next     | State    |        |

|---------|----------|----------|--------|

| state   | W = 0    | w = 1    | Output |

| y2y1    | $Y_2Y_1$ | $Y_2Y_1$ | Z      |

| 0.0     | 0.0      | 01       | 0      |

| 01      | 0.0      | 10       | 0      |

| 10      | 0.0      | 11       | 0      |

| 11      | 0.0      | 11       | 1      |

| Present | Next  | Output |   |

|---------|-------|--------|---|

| state   | w = 0 | w = 1  | z |

| А       | А     | в      | 0 |

| В       | Α     | С      | 0 |

| С       | Α     | D      | 0 |

| D       | Α     | D      | 1 |

(a) State-assigned table

(b) State table

#### Figure 8.81. Tables for the circuit in Example 8.80.

Figure 8.82. Circuit for Example 8.9.

$$J_1 = w$$

$$K_1 = w' + y_2$$

$$J_2 = wy_1$$

$$K_2 = w'$$

$$z = y_2y_1$$

| Present               |          |          |          |          |        |

|-----------------------|----------|----------|----------|----------|--------|

| state                 | w =      | = 0      | w =      | = 1      | Output |

| <i>Y</i> 2 <i>Y</i> 1 | $J_2K_2$ | $J_1K_1$ | $J_2K_2$ | $J_1K_1$ | z      |

| 00                    | 01       | 01       | 0 0      | 11       | 0      |

| 01                    | 01       | 01       | 10       | 11       | 0      |

| 10                    | 01       | 01       | 0 0      | 10       | 0      |

| 11                    | 01       | 01       | 10       | 10       | 1      |

Figure 8.83. The excitation table for the circuit in Figure 8.82.

| Present | Next State |          |        |

|---------|------------|----------|--------|

| state   | W = 0      | w = 1    | Output |

| y2y1    | $Y_2Y_1$   | $Y_2Y_1$ | Z      |

| 0.0     | 0 0        | 01       | 0      |

| 0 1     | 0 0        | 10       | 0      |

| 10      | 0 0        | 11       | 0      |

| 11      | 0 0        | 11       | 1      |

| Present | Next state |       | Output |

|---------|------------|-------|--------|

| state   | W = 0      | w = 1 | z      |

| А       | А          | в     | 0      |

| В       | Α          | С     | 0      |

| С       | Α          | D     | 0      |

| D       | А          | D     | 1      |

(a) State-assigned table

(b) State table

$$D_{1} = w(y_{2} + y'_{1})$$

$$T_{2} = wy_{1}y'_{2} + w'y_{2}$$

$$z = y_{2}y_{1}$$

| Present               | Flip-flop inputs |          |        |

|-----------------------|------------------|----------|--------|

| state                 | w = 0            | w = 1    | Output |

| <i>Y</i> 2 <i>Y</i> 1 | $T_2D_1$         | $T_2D_1$ | Ζ      |

| 0 0                   | 0 0              | 01       | 0      |

| 0 1                   | 0.0              | 10       | 0      |

| 10                    | 10               | 01       | 0      |

| 11                    | 10               | 01       | 1      |

| Present | Next State |          |        |

|---------|------------|----------|--------|

| state   | W = 0      | w = 1    | Output |

| y2y1    | $Y_2Y_1$   | $Y_2Y_1$ | Z      |

| 0.0     | 0.0        | 01       | 0      |

| 0 1     | 0.0        | 10       | 0      |

| 10      | 0.0        | 11       | 0      |

| 11      | 0.0        | 11       | 1      |

| Present | Next state |       | Output |

|---------|------------|-------|--------|

| state   | W = 0      | w = 1 | z      |

| Α       | А          | в     | 0      |

| В       | Α          | С     | 0      |

| С       | Α          | D     | 0      |

| D       | Α          | D     | 1      |

(a) State-assigned table

(b) State table