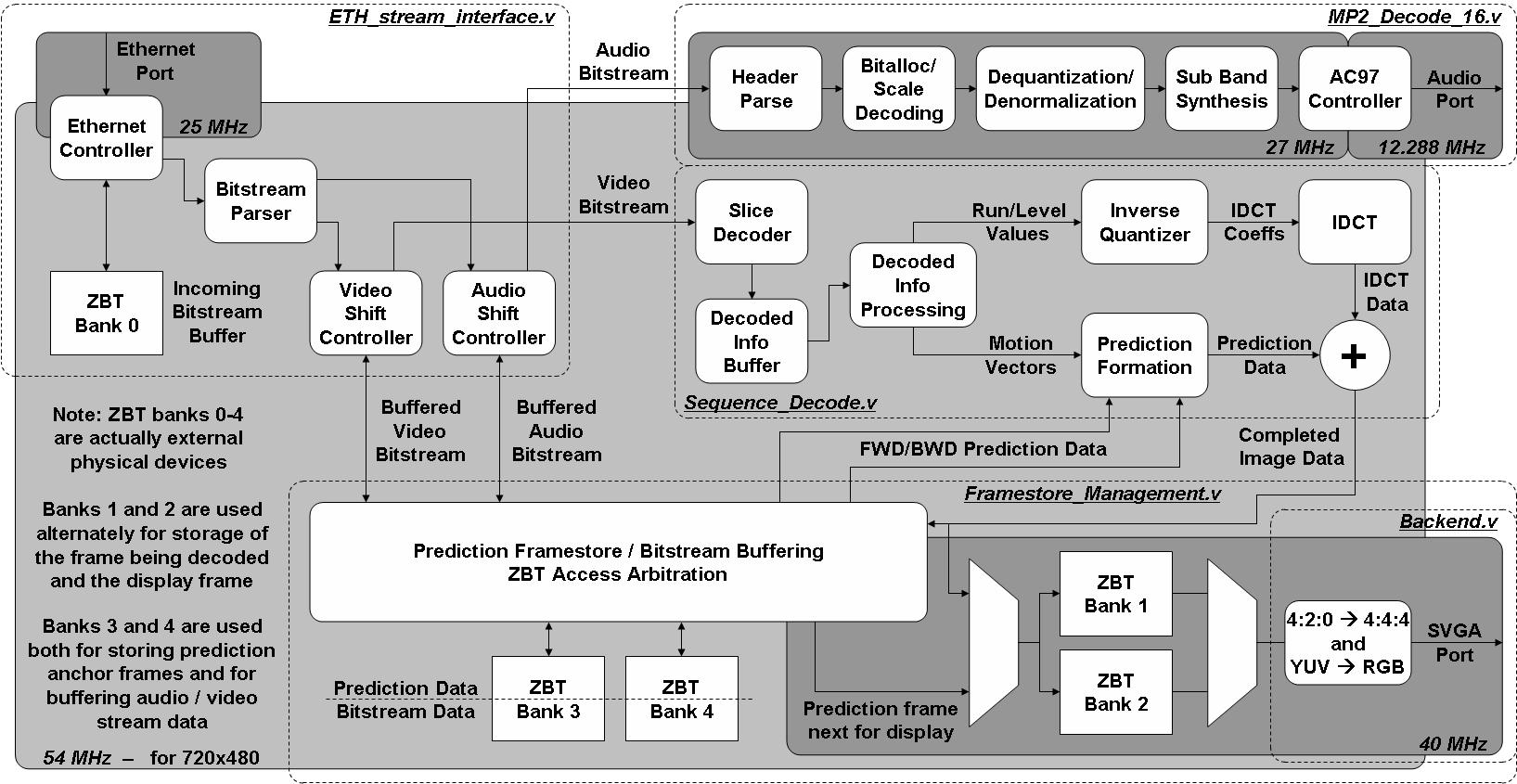

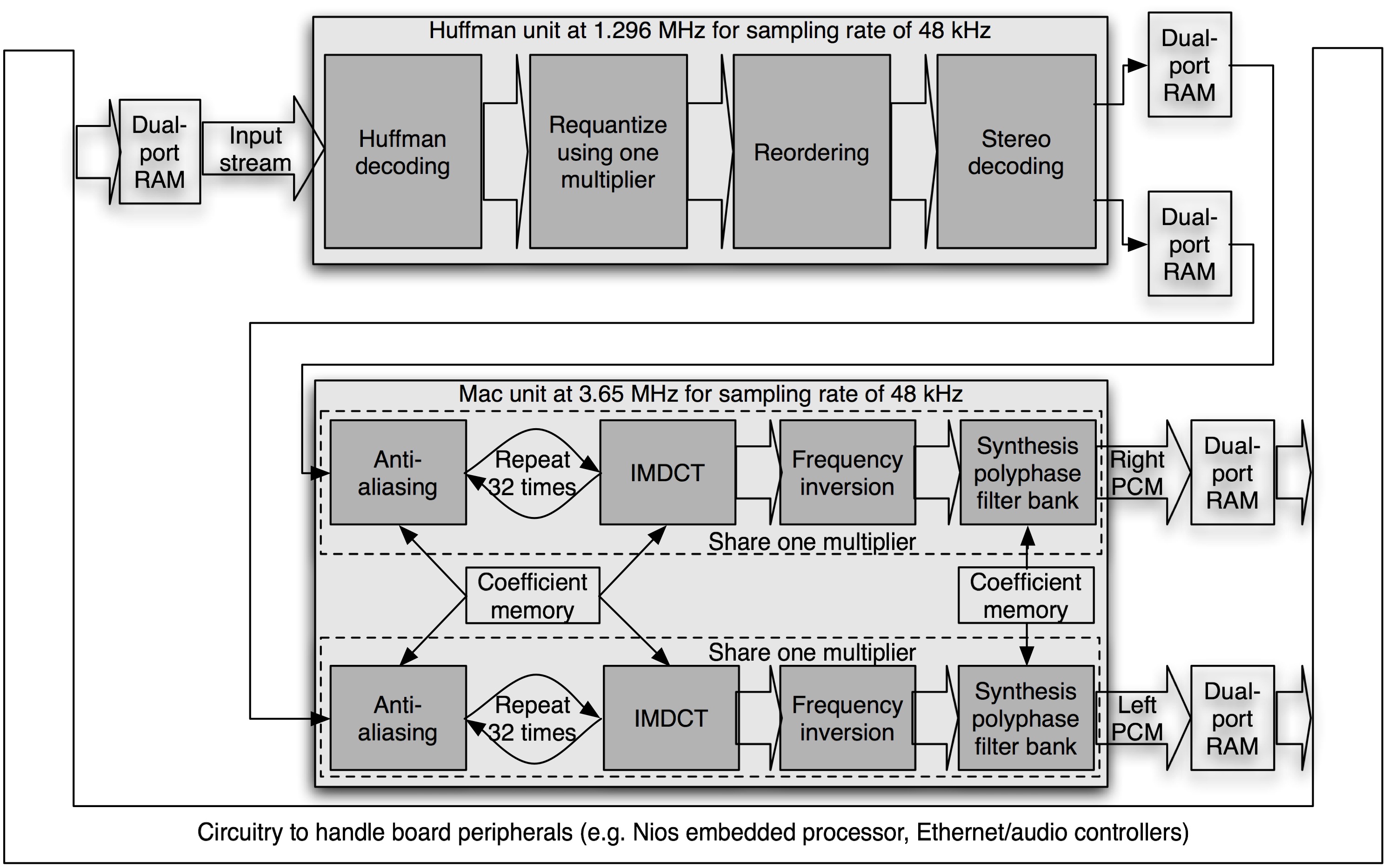

Release of Verilog design files for MP3 audio and MPEG2 audio/videoGiven the lack of public releases of source files for hardware designs that implement complete solutions for real-life applications, we have decided to develop our own MP3 audio and MPEG2 audio/video decoders. What started as a side-project, for building benchmarks for our CADT research, has become full-time work motivated by the challenge to improve the energy-efficiency of MP3/MPEG2 micro-architectures. We have achieved this by exploring fixed-point implementations that do not compromise the quality of the complete solution prototyped in the Xilinx Multimedia Board. For example, for the MPEG2 main level/main profile implementation that processes NTSC video at 720x480 @29.97 fps, we have employed only 3,337 flip-flops and 10,615 4-input look-up tables, with 28 2-KByte RAM blocks and 3 18-bit fixed-point multipliers (this includes Ethernet, ZBT memory, audio and SVGA controllers). To satisfy the SDTV resolution, the state elements are all clocked below 54 MHz (depending on the logic partition and the interface they are interacting with). Similarly, for MP3 audio, the two main blocks that are at the core of the decoding process employ less than 600 flip-flops clocked below 4 MHz, while satisfying sample rates of 48 Ksamples per second. The MP3 audio decoder has been ported also to the Altera DE2 Board. It is important to note that our release is provided as is, without any warranty or support. For furher details please consult the "doc" folder in the enclosed archives.

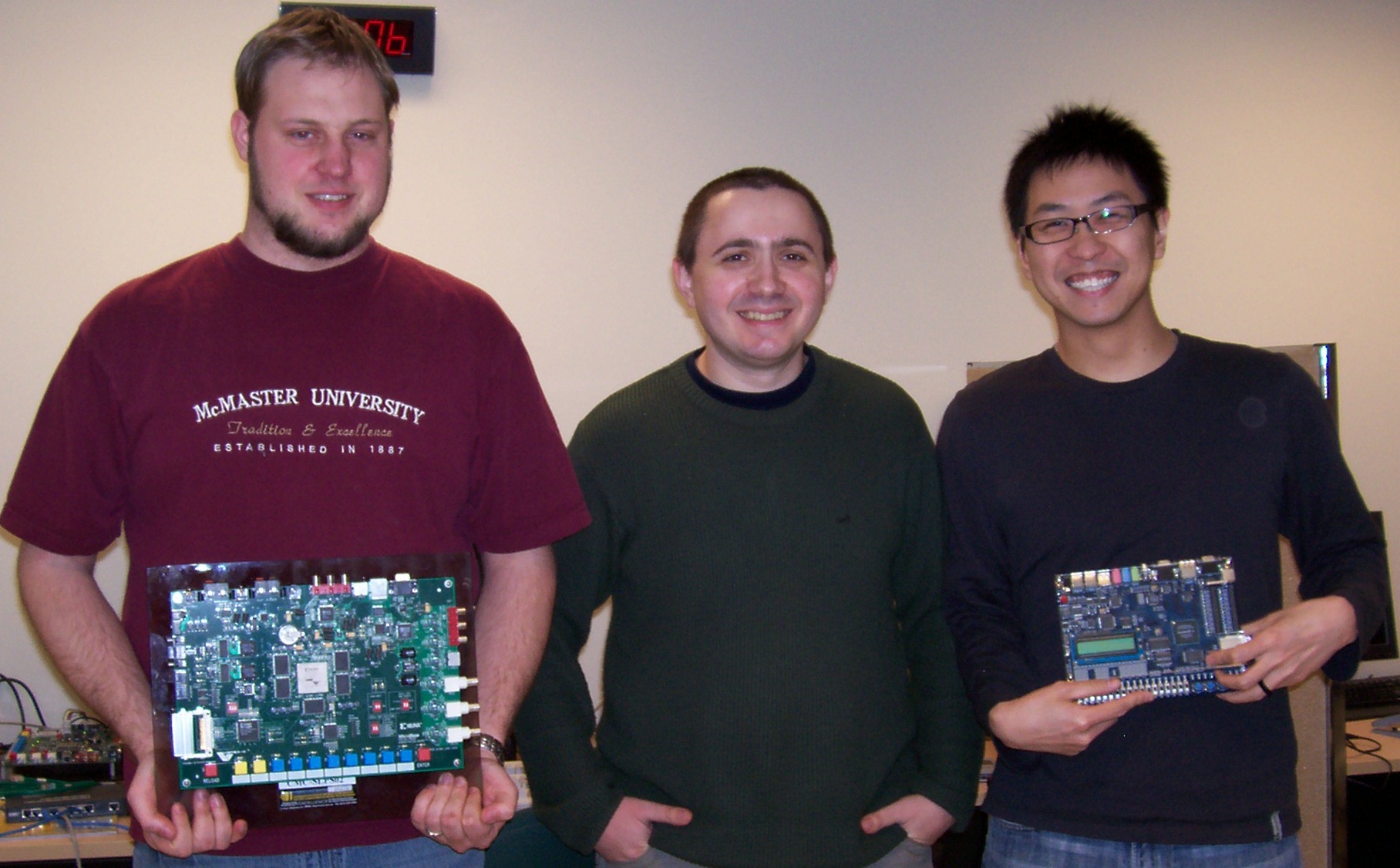

Adam Kinsman, Nicola Nicolici and Henry Ko are thankful to David Leung, Ehab Anis, Phil Kinsman and Jason Thong for their contribution to this work. They also gratefully acknowledge the Canadian Microelectronics Corporation for providing the design workstations, prototyping platforms and CAD software and EETimes for covering this release. We hope that other research groups will find these designs useful in their work. Adam, Henry and Nicola have also worked on the release of source Verilog files for digital image decompression, as part of the digital systems design course at McMaster University. Further details can be found here . |

||||||

|

Last changed on March 31, 2007 |