Software

MCsim

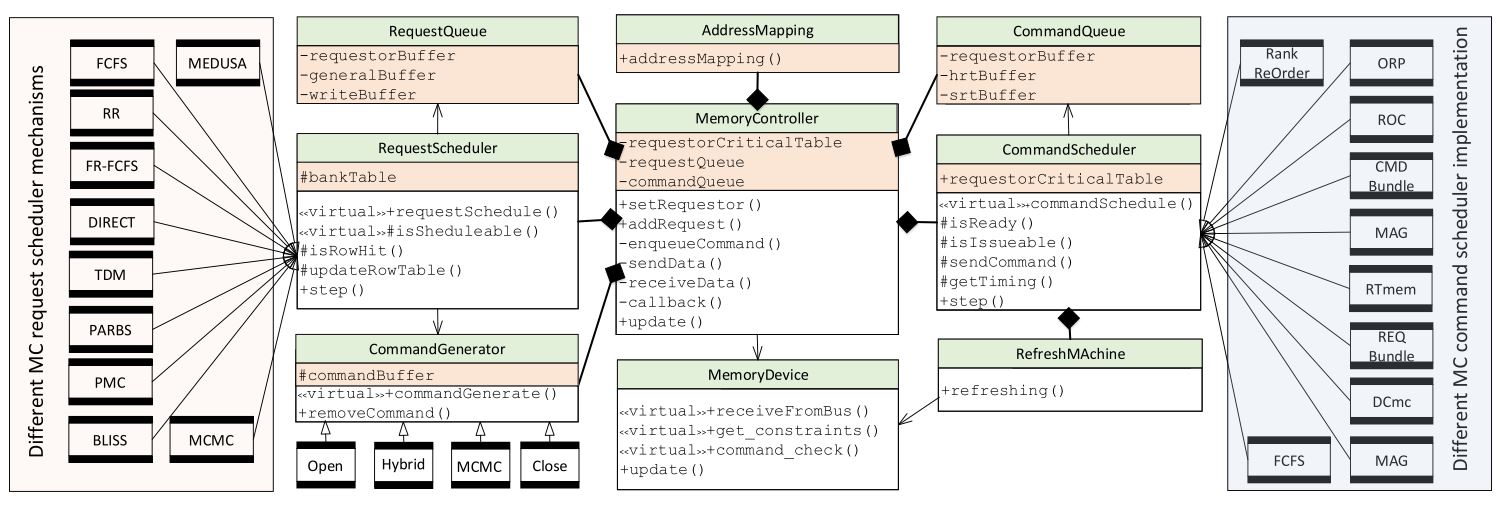

MCSim is an Open-Source Extensible DRAM Memory Controller Simulator.

MCSim source code is avaiable "HERE" and its details are recently published in the IEEE CAL paper "HERE"

If you intend to use MCsim, please cite our paper using the following BIBTEX:

@article{rezaCAL,

title={MCsim: An Extensible DRAM Memory Controller Simulator},

author={Mirosanlou, Reza and Guo, Danlu and Hassan, Mohamed and Pellizzoni, Rodolfo},

journal={IEEE Computer Architecture Letters (CAL)},

pages={1--4},

year={2020},

publisher={IEEE},

code={https://github.com/uwuser/MCsim},

pdf={/assets/publications/reza_MCsim_CAL.pdf},

}

PENDULUM

PENDULUM is a time-based cache

coherence protocol to enable simultaneous and predictable access

to shared data in Multi-Core Mixed Criticality Systems.

We release the implementation of PENDULUM in the Gem5 simualtor HERE.

PENDULUM was published in RTSS'19, the paper can be downloaded from HERE.

If you intend to use this code, please cite our paper using the following BIBTEX:

@inproceedings{niv_19_pendulum_rtss,

author = {Sritharan, Nivedita and Kaushik, Anirudh M. and Hassan, Mohamed and Patel, Hiren},

title = {Enabling Predictable, Simultaneous and Coherent Data Sharing in Mixed Criticality Systems},

booktitle = {proceedings of IEEE Real-Time Systems Symposium (RTSS)},

year = {2019},

pages = {1--11},

month = dec,

pdf={/assets/publications/niv_19_pendulum_rtss.pdf},

code={https://gitlab.com/FanusLab/pendulum-coherence},

month_numeric = {12}}

PMSI

PMSI is a predictable cache coherence protocol,

which mandates the use of certain invariants to ensure predictability.

In particular, PMSI enforces these invariants by augmenting the classic modify-share-invalid (MSI) protocol with transient

coherence states, and minimal architectural changes.

We release the implementation of PMSI in the Gem5 simualtor HERE.

PMSI was published in RTAS'17, the paper can be downloaded from HERE.

If you intend to use this code, please cite our paper using the following BIBTEX:

@inproceedings{hassan_17_pmsi,

author = {Hassan, Mohamed and Kaushik, Anirudh and Patel, Hiren},

booktitle = {proceedings of the IEEE Real-Time and Embedded Technology and Applications Symposium (RTAS)},

month = apr,

pages = {1--12},

publisher = {IEEE},

title = {Predictable cache coherence for multi-core real time systems},

code = {https://gitlab.com/FanusLab/pmsi},

year = {2017},

pdf={/assets/publications/hassan_17_pmsi.pdf},

slides={/assets/publications/hassan_17_pmsi_slides.pdf},

month_numeric = {4}

}

MCXplore

MCXplore is an automated framework for the validation of dynamic random access memory controllers (DRAM MCs) called MCXplore.

MCXplore enables validation engineers to define their test plans precisely as temporal logic

specifications. Then, it uses the NuSMV model-checker to generate

counter-examples that serve as test templates; hence, MCXplore

uses these test templates to generate memory tests to validate

the correctness properties of the memory controller.

We show

the effectiveness of MCXplore by validating various state-of-the-

art MC features as well as hard-to-detect timing violations that

often occur.

We also provide a set of predefined test plans,

and regression tests that validate essential properties of modern

DRAM MCs. We release MCXplore as an open-source framework

to allow validation engineers and researchers to extend and use.

The code as well as the test suites can be downlowded from HERE.

MCXplore was published in DATE'16 (paper is HERE) and the extended version in TCAD'17 (paper is HERE) .

If you intend to use this code, please cite our papers using the following BIBTEX:

@inproceedings{hassan_16_mcxplore,

author = {Hassan, Mohamed and Patel, Hiren},

booktitle = {proceedings of IEEE Design Automation and Test in Europe (DATE)},

date-added = {2014-09-27 19:04:05 +0000},

date-modified = {2014-09-27 19:06:55 +0000},

month = sep,

pages = {1357--1362},

numpages = {6},

publisher = {IEEE},

note = {\textbf{Acceptance rate: 24\%}},

title = {MCXplore: An Automated Framework for Validating Memory Controller Designs},

code = {https://gitlab.com/FanusLab/mcxplore},

year = {2016},

pdf={/assets/publications/hassan_16_mcxplore.pdf},

slides={/assets/publications/hassan_16_mcxplore_slides.pdf},

month_numeric = {9}

}

@article{hassan_17_mcxplore_tcad,

author = {Hassan, Mohmaed and Patel, Hiren},

journal = {IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD)},

title = {MCXplore: Automating the Validation Process of DRAM Memory Controller Designs},

year = {2017},

number = {99},

pages = {1--14},

keywords = {Benchmark testing;Computational modeling;Delays;Model checking;Random access memory;Space exploration;DRAM;memory controller;model checking;testing;validation;verification},

doi = {10.1109/TCAD.2017.2705123},

issn = {0278-0070},

pdf={/assets/publications/hassan_17_mcxplore_tcad.pdf},

slides={/assets/publications/hassan_17_mcxplore_slides.pdf},

month = {}

}